Constantin

Свой-

Постов

397 -

Зарегистрирован

-

Посещение

Весь контент Constantin

-

Altium Designer для начинающих

Constantin ответил ViKo тема в Altium Designer, DXP, Protel

Если не "редактировать", т.е. изменять модель, а только установить в условный "0" координат, мне на первых порах было проще сделать сборку, вставить в нее модель, привязать как нужно (чтобы в Altium все было в "0") и экспортировать в тот же STEP. Хотя это можно сделать и инструментами "Direct Editing". -

Altium Designer для начинающих

Constantin ответил ViKo тема в Altium Designer, DXP, Protel

Или по другому, универсальный подход для любых объектов: выделяем отверстия на материнской плате, в PCB List копируем их координаты , вставляем для соответствующих им на дочерних платах. При необходимости перед вставкой в Excel пересчитываем смещение. Но я в подобных случаях предпочитаю расположить Origin и ориентацию отдельных плат таким образом, чтобы ничего не приходилось двигать/вращать. -

Altium Designer для начинающих

Constantin ответил ViKo тема в Altium Designer, DXP, Protel

По правде говоря, в новых версиях не проверял, а когда она появилась - на немаленькой на тот момент библиотеке результат для компонентов сложнее резистора/конденсатора оказался негодным. Начиная с транзисторов во всем их разнообразии изображений и четырех квадрантов ориентации. Я попробовал, понял что придется продумать логику создания элементов и перелопатить все библиотеки, попробовал и прогнозируемый объем работы заставил отказаться от идеи. И как мне помнится, я с такими выводами на этом форуме был не одинок. -

Altium Designer для начинающих

Constantin ответил ViKo тема в Altium Designer, DXP, Protel

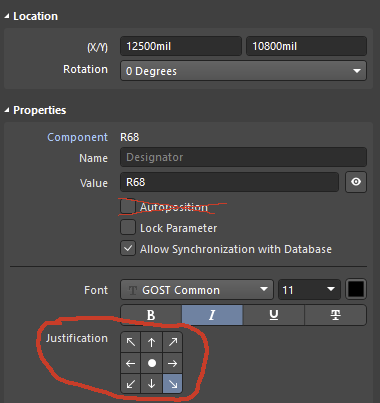

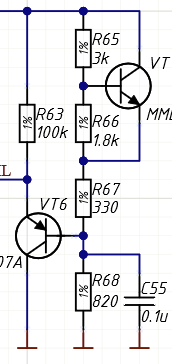

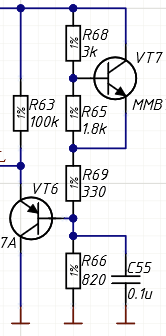

Лучше делать аннотацию по Designator, в таком случае она управляема, выполняется по координатам точки привязки этого самого Designator. А вот ее положение зависит от настроек: Для примера: исходно все привязки в левом нижнем углу: А теперь для R65 и R67 привязка изменена на правый нижний угол (зеркальное отражение по X, клавишей "x" при перемещении). Визуально неотличимо, а аннотация изменилась. -

По моему опыту - багов с заливкой полигонов в последние несколько лет не припомню, иначе предупредил бы.

-

Думается, что эта функция не различает типы via, вот и обходит ранее расставленные. Не баг, а фича. А вот насыпать "stitching via" поверх топологического элемента типа" Net tie" при том, что последний в явном виде содержит "Via Keep-out" представляется багом :-) Если это критично (как мне кажется, не в данном случае) - можно для полигона повысить требования к точности аппроксимации дуг. Ну, и уменьшить зазор в правилах на недостающую по факту величину.

-

Altium Designer для начинающих

Constantin ответил ViKo тема в Altium Designer, DXP, Protel

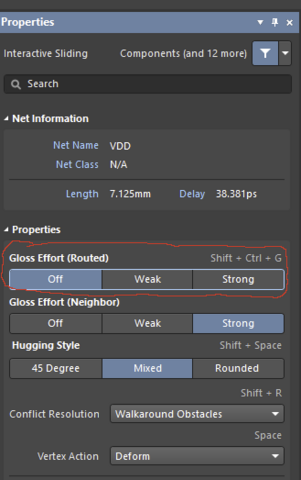

Без паники! Если находимся в режиме редактирования трасс (двигаем сегмент) то это сочетание клавиш как раз переключает Gloss Effort (Routed), попробуйте. -

Altium Designer для начинающих

Constantin ответил ViKo тема в Altium Designer, DXP, Protel

Попробуйте выключить Gloss Effort (Routed) в панели Properties при редактировании или глобально в Preferences. -

Altium Designer для начинающих

Constantin ответил ViKo тема в Altium Designer, DXP, Protel

А где написано что нарушено правило высоты? Я бы сказал, что просто XP12 не должен находиться в Room MCU. Может XP12 нужно назначить ComponentClass "MCU"? -

Altium Designer для начинающих

Constantin ответил ViKo тема в Altium Designer, DXP, Protel

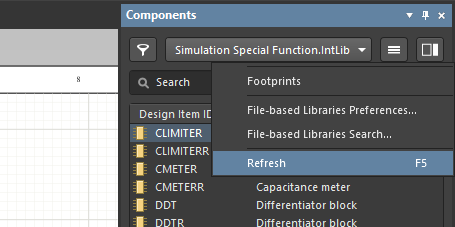

Если библиотека подключена и была отредактирована (т.е. все нормально), чтобы увидеть изменения нужно выполнить Refresh в панели Components . -

Altium 21.6 и выше

Constantin ответил Uladzimir тема в Altium Designer, DXP, Protel

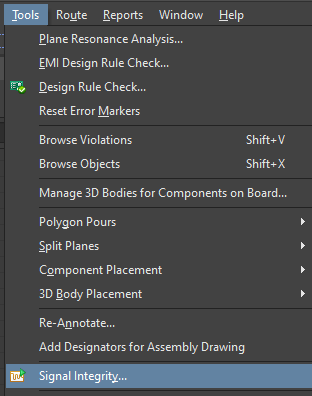

Возможность попробовать уже есть :-) Если установить расширение, то в папке \ProgramData\Altium\Altium Designer {xxxxxx yyyy....}\Extensions\EMIStreamV2\EXE\Document находятся EMI Design Rule Check Operation Manual.pdf Plane Resonance Analysis Operation Manual.pdf Вот только времени поупражняться пока нету... -

Altium 21.6 и выше

Constantin ответил Uladzimir тема в Altium Designer, DXP, Protel

Выделение контура в механическом слое и выполнение команды "Tools -> Convert -> Convert Selected Primitives to Keepouts" избавляет от двойной работы :-) -

Altium Designer для начинающих

Constantin ответил ViKo тема в Altium Designer, DXP, Protel

-

2018 Вопросы начинающих

Constantin ответил Sanchosd тема в Altium Designer, DXP, Protel

Так в том то и дело: если нужна перемычка, которую паяют, то и вопросов нет. А вот если нужен цельный элемент топологии, то без Net Tie не обойтись. Примеров таких топологий масса: это и планарные трансформаторы, и всевозможные СВЧ структуры (фильтры, делители ответвители и т.д. и т.п.). -

2018 Вопросы начинающих

Constantin ответил Sanchosd тема в Altium Designer, DXP, Protel

Да, такому компоненту присваивается тип Net Tie, им можно соединить медью две разноименных цепи. -

Altium Designer для начинающих

Constantin ответил ViKo тема в Altium Designer, DXP, Protel

А без Via Shielding все нормально? Потому как просматривается на слое Top вокруг структуры "вывод 15- track - via" Polygon Cutout, он и отрезает полигон от площадки. -

Да. Мне было бы проще и быстрее попробовать, чем ждать ответа :-)

-

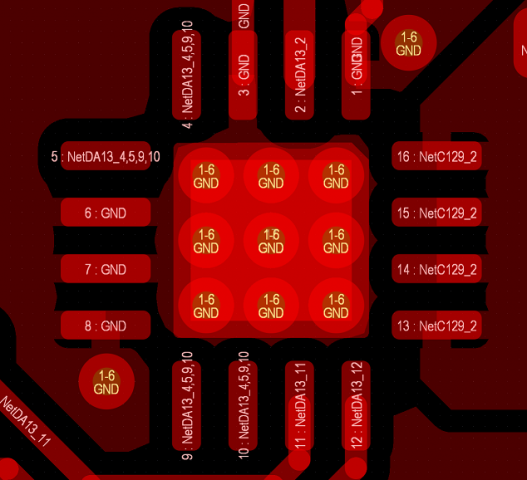

Ставится Pad подходящей стандартной геометрии с нужным Designator, поверх создается Region какой нужно геометрии, по нему можно насыпать Via. В процессе передачи данных проекта на плату вся медь присоединится к цепи Pad. Надеюсь, видно как это может выглядеть. По центру Pad, на схеме подключенный к GND, поверх него Region со скругленными и срезанным углом, ну и Via. И никаких цепей в библиотеке.

-

Altium Designer для начинающих

Constantin ответил ViKo тема в Altium Designer, DXP, Protel

Для этого нужно включить опцию Preferences - PCB Editor - General - Protect Locked Objects. -

Altium Designer для начинающих

Constantin ответил ViKo тема в Altium Designer, DXP, Protel

-

2018 Вопросы начинающих

Constantin ответил Sanchosd тема в Altium Designer, DXP, Protel

Цепи одновременно назначено Net Label и Power Port (который желтый), это разные сущности :-). Если нет необходимости в иерархии, лучше оставить Net Label и в опциях проекта Net Identifier Scope установить Global (Netlabels and ports global). Тогда все идентичные Net Label на всех листах создадут одну цепь. -

Altium 21.6 и выше

Constantin ответил Uladzimir тема в Altium Designer, DXP, Protel

1) Могу подтвердить, уже давно настройки записываю в отдельный документ и новую версию привожу в соответствие вручную 2) Никаких особых глюков именно с .mdb не наблюдаю, для современных версий использую 64-разрядный Access. С клавиатурными сочетаниями есть какая-то проблема, я тоже наблюдал частичную работоспособность, но так и не понял после чего все заработало нормально. Какой-то плавающий глюк... -

Altium 21.6 и выше

Constantin ответил Uladzimir тема в Altium Designer, DXP, Protel

Видимо имелось ввиду что для резистора 22 Ома (как следует из Design Item ID) ожидается в Description тот же номинал. Это точно не ошибка в библиотеке? Т.е. раньше было нормально? -

Когда-то давно (возможно, как раз во времена 18-й версии) в подобной ситуации помогло последовательное выполнение "Shelve" и "Restore" для всех полигонов платы.