sergunas

Свой-

Постов

462 -

Зарегистрирован

-

Посещение

-

Победитель дней

1

Весь контент sergunas

-

Актуально!

-

Smart-Git для некоммерческого использования

sergunas опубликовал тема в Управление проектами

Если кто использует, подскажите как сбросить 30-дневный срок окончания работы пробной лицензии. Переустановка программы с удалением пользовательских файлов в AppData\Roaming не помогает... -

Китайские микросхемы памяти (DDR3, NAND)

sergunas ответил sergunas тема в Микросхемы

Китайские DDR3 вообще какие-нибудь существуют? -

Китайские микросхемы памяти (DDR3, NAND)

sergunas опубликовал тема в Микросхемы

Посоветуйте микросхемы памяти китайского производства, доступные к приобретению: 1) DDR3 16Gb (аналог VD3D16G16VB96IB2WH) 2) NAND-флэш 128Gb (аналог VDNF128G08VS50IB8V25) Заранее признателен. -

Благодарю за ответ, успокоили)

-

Один вопрос вроде как снят, нашёл команду "Open IP Config file"

-

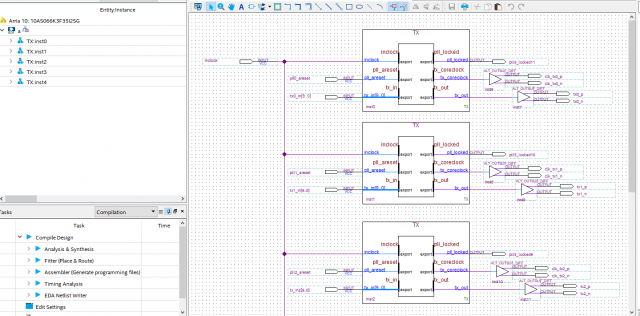

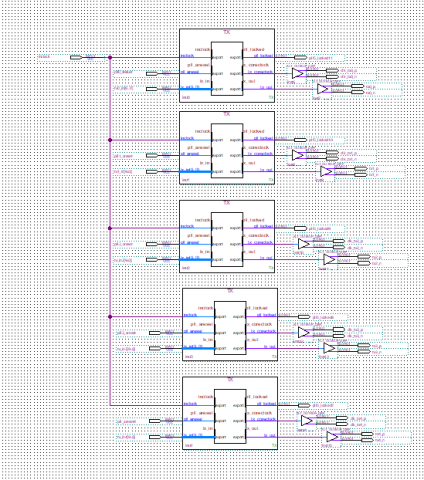

Подскажите, два вопроса по Gowin EDA: 1) Как можно открыть для просмотра/изменения параметров ранее сгенерированные IP ядра? 2) Как заставить отображаться иерархию проекта во вкладке Hierarchy? Сейчас пишет: <указанное имя топ-модуля>(Not Exist). При этом проект компилируется, работает.

-

Подскажите, в ПЛИС Gowin GW5A-138FC676 что за напряжение питания 1.2В: VCC_REG (Power supply pin of Regulator voltage)?

-

проблема снята, дело было в файле "org.eclipse.ui.ide.prefs"

- 4 ответа

-

- 1

-

-

Не запускается Vitis 2021

sergunas опубликовал тема в Среды разработки - обсуждаем САПРы

ОС Windows 11 x64, в диспетчере вижу процесс eclipse.exe. Вчера было всё норм. Подскажите в чём может быть причина. Заранее признателен.- 4 ответа

-

- 1

-

-

Да, пока на таком варианте и остановились...

-

На Evolution Board стоят два чипа Serial NOR Flash (MT25QU512ABB1EW9) размером 512Mbit каждый. Максимально, что смог найти, MRAM объёмом 16Mbit (M1016204). Итого, если заменить, получим 32Mbit - маловато... Как вариант можно повесить MRAM на выводы ПЛИС, которые выведены на FMC. Но, если возможен вариант, озвученный в сабж, было бы интереснее?

-

Умеет то умеет, на самой Evolution Board даже стоит SPI-FLASH и может быть использована для загрузки, но она не радстойкая. А наружу выведен только интерфейс SD (через микросхему IP4856CX25).

-

Есть Evolution Board с SoC с выведенным интерфейсом "SD 3.0 memory card interface". Требуется к ней подключить память для загрузки SoC. Просто SD карта не подходит: требования по тряске и по радстойкости. Поэтому возникла мысль сделать имитатор SD карты на базе памяти MRAM. Подскажите какие есть решения? Заранее признателен.

-

Переходить на новый шрифт - это перерисовывать множество готовых схем, поэтому выбрал следующий вариант Взял шрифт GOST 2.304\gost_2.304.ttf, с отображением в Altium которого проблем нет. Переименовал его в программе FontLab 7 на имя "mipgost", стало всё хорошо) mipgost_se.ttf

-

В Altium Designer 20 сломался ГОСТовский шрифт

sergunas опубликовал тема в Altium Designer, DXP, Protel

Использую в качестве ГОСТ'овского шрифта MIPGOST. Altium Designer 20 отказывается его понимать: Подскажите в чём может быть дело, в каком направлении искать решение проблемы? До 18-й версии включительно было всё норм. -

Есть 4 дифференциальных аналоговых сигнала (выходы ЦАП), частотой до 100 МГц, как лучше их передать на плату СВЧ (длина рассмтояния 20-30см). Если бы был один диф. сигнал, поставил два SMA, но в данном случае 8 штук ставить совсем не хочется. Есть какие-то решения (разъемы, кабели)? Что-то наподобии har-link от Harting.

-

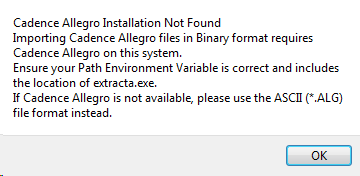

Вопрос решён согласно разделу "ASCII Conversion" по ссылке https://www.altium.com/documentation/19.0/display/ADES/((Allegro+Import))_AD Allegro2Altium.bat делает ALG-файл из BRD-файла, который без проблем импортируется в Altium.

-

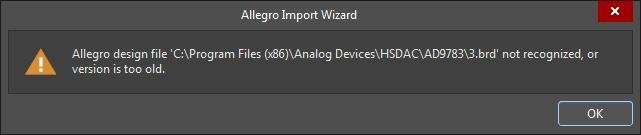

Altium при импорте ругается: При это файл "3.brd" успешно открывается в Allegro PCB Designer 17.2 Файл скачан отсюда: ftp://ftp.analog.com/pub/HSSP_SW/HSCDAC/Documents/AD9783/AD9783-DUAL-EBZ RevB.brd и отконвертирован с помощью d:\Cadence\SPB_17.2\tools\bin\dbdoctor_ui.exe

-

Импорт brd-файлов

sergunas ответил sergunas тема в Altium Designer, DXP, Protel

Вопрос снят. Прописал путь файла extracta.exe в переменные: path и AltiumPath. -

Импорт brd-файлов

sergunas опубликовал тема в Altium Designer, DXP, Protel

Подскажите как можно импортировать в Altium Designer brd-файл топологии, созданный в Cadence Allegro PCB Designer. Altium пишет: В Cadence Allegro не могу найти команды "Сохранить как ALG" -

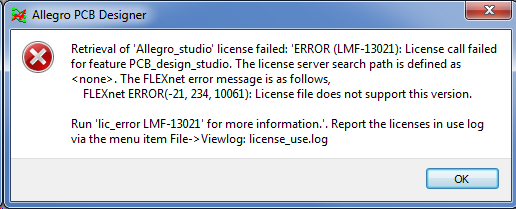

Первый раз поставил CADENCE SPB 17.20.000. Помогите с лицензией. Скачал Aleego-Crack-Master-V2_1_6.7z pubkey-verify запускал в директории, успешно отработал. В Cadence License Client Configuration Utility указал путь к license.dat (т.е. в окне Licence Path указано только: d:\Cadence\SPB_17.2\license.dat) Файл license.dat не изменял.

-

2018 Вопросы начинающих

sergunas ответил Sanchosd тема в Altium Designer, DXP, Protel

Вопрос следующий. В проекте применяются полуотверстия размера 0.8/1.4мм (обычные сквозные Pad'ы с центром в крае платы). Чтобы это полуотверстие крепче держалось, прошил их переходными отверстиями 0.2/0.5мм. Из картинки видно, что в сигнальных слоях (3 слоя) металлизация есть. Как сделать, чтобы металлизация появилась и в слоях питания? Спасибо. -

Проект был разработан в версии 5.3.0, чтобы ничего не сломать... Ошибка побеждена установкой BIOS MCSDK 2.1.2.