Sagittarius

Свой-

Постов

209 -

Зарегистрирован

-

Посещение

Весь контент Sagittarius

-

ESP12E в серии, входной брак

Sagittarius ответил Sagittarius тема в RF & Microwave Design

GPIO0 в устройстве подтянут так же. Проблемы с прошивкой своего кода в модуль, AT-командами не пользовались, может с ними что то и работает, не пробовали. -

ESP12E в серии, входной брак

Sagittarius ответил Sagittarius тема в RF & Microwave Design

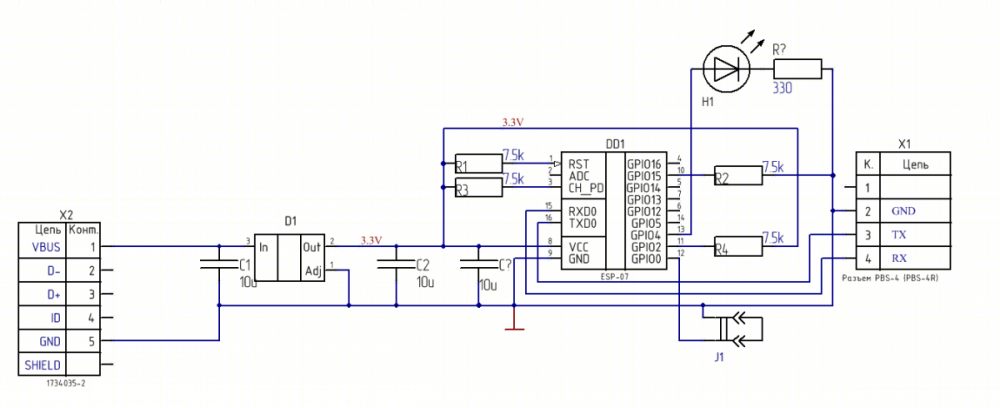

схема отдельного тестера-прошивальщика (заливаем свою прошивку), вроде все по доке. Питание с USB, с этого же компа переходник USB-UART на X1. Собрано на макетке, провода короткие, скорость 115200 (пробовал и другие, без разницы). ESP-07(на схеме) и ESP12E по боковым выводам совпадают. По общему количеству из последнего из 50 модулей по этой схеме 18 не прошились, с 32 все нормально. Из обнаруженных странностей - иногда CH_PD (Enable) у некоторых модулей притянут к 0 самим модулем. Если его подтянуть резюком 700-800 Ом к +3.3В и потом резюк убрать, то этот вход остается на уровне 1.5-2В, этого может хватить что бы модуль запустился. Если на 3.3В ткнуть без резюка то уровень на Enable будет 2-3В. из 5-ти модулей с таким косяком 2 ожило, 3 нет. Часть модулей на BOOT (GPIO0) вне зависимости от его подключения (GND/висит/подтянут к+) выдают 26МГц, у нормальных там в режиме прошивки 0. -

ESP12E в серии, входной брак

Sagittarius ответил Sagittarius тема в RF & Microwave Design

esptool, через переходник USB-UART. но еще до собственно программирования модули, с которыми все нормально мигают синим светодиодом, которые не прошьются - не мигают. Т.е. разница в работе уже просто при подаче питания. -

ESP12E в серии, входной брак

Sagittarius ответил Sagittarius тема в RF & Microwave Design

Так и делаем, на пружинных иголках стенд, 1/4 не прошивается, ни на что не реагирует, максимум если BOOT оставить висящим, то на нем 26МГц будет -

ESP12E в серии, входной брак

Sagittarius опубликовал тема в RF & Microwave Design

Здравствуйте. Кто ни будь применял модули ESP12E (AI-Thinker) в мелких сериях? Сделали устройство, делаем мелкую серию, из 70 модулей 22 не прошиваются, никакими светодиодами не мигают. Закупались в чипдипе. Такой процент брака это норма для модулей или это какие то их не учтенные особенности? У кого какой опыт применения? Спасибо. -

DbLib (Exel) Win10 и обновление KB4457128

Sagittarius опубликовал тема в Altium Designer, DXP, Protel

Здравствуйте. Скорее информации пост. После очередного обновления Win10 перестала открыватся рабочая либа (база данных через exel). Работало только если файл xls был предварительно открыт в Exel. При этом аналогичная библиотека (намного меньше размером) нормально работала. Вылечилось только удалением обновления и запретом обновлений вообще, через реестр. Если кто сталкивался с таким и победил с сохранением обновления - что делать? Спасибо. -

STM32H7 работа с SDRAM. Проблема

Sagittarius ответил Николандр тема в STM

Делел проект на STM32F746G с SDRAM и видео выходом. SDRAM инитил куском либы из примеров, идущих с кубом-мх. Конкретно файл stm32746g_discovery_sdram.c (17 013 байт) но, как уже говорили, 133 там никак не получалось, и когда читал доку на H7xx то как запомнилось, выше 100 частоту SDRAM на нем тоже поднять нельзя. У меня на 100МГц плата в 4 слоя без особых ухищрений, единственно на что смотрели - чтоб длина проводника тактовой была не менее максимального из остальных адресов/данных/команд. Из доки на F746 === SDRAM waveforms and timings • CL = 30 pF on data and address lines. CL = 10 pF on FMC_SDCLK unless otherwise specified. In all timing tables, the THCLK is the HCLK clock period. – For 3.0 V≤VDD≤3.6 V, maximum FMC_SDCLK= 100 MHz at CL=20 pF (on FMC_SDCLK) === да, про куб - на прямую проект им сгенеренный с SDRAM у меня не заработал, только с другими файлами из примеров от этого же куба. -

LwIP, UDP

Sagittarius ответил Sagittarius тема в ARM

автор забыл про отпуск перед написанием вопроса и ушел туда но уже вернулся :-) Вопрос именно про конкретную реализацию а не про сферический в вакууме RFC. Что сейчас наблюдается: используя udp_sendto раз в секунду посылается 28 пакетов. Пробовал как подряд в цикле так и с паузой 20-200 мс. Но глюк один и тот же. Иногда последний пакет из пачки задерживается и приходит как первый при начале посылок за следующую секунду. Задержка именно в LwIP, смотрел траффик по Wireshark. Так что где то внутри буферизация есть и возврат из udp_send не означает физическую отправку пакета. Собственно вопрос тот же, как правильно отправлять последовательность пакетов по UDP используя LwIP? Спасибо. -

LwIP, UDP

Sagittarius опубликовал тема в ARM

Здравствуйте. Проблемка, не могу найти как сдеалть. Микроконтроллер периодически (раз в 1с) посылает UDP пакет, все работает. Но надо за один раз посылать порядка 20 разных отдельных пакетов. Буфер для формирования пакетов один. Как определить что предыдущий пакет уже отправлен и можно формировать и отправлять следующий? Определить что именно отправлен, обработан модулем Eth и выдан в линию связи (а не принят адресатом). Спасибо. -

char * и UTF-8 vs CP1251

Sagittarius ответил Sagittarius тема в IAR

Да, по дороге на работу как раз об этом подумал :-) так и есть, одни в CP1251 а другие в UTF-8, в IAR оба отображаются корректно. Теперь вопрос - а как IAR узнает какой файл в какой кодировке? Спасибо. -

char * и UTF-8 vs CP1251

Sagittarius опубликовал тема в IAR

Здравствуйте. Какой то косяк, но в чем никак не пойму. Собрал проект (STM32746, IAR 7.80, куб+freertos+uGFX) в исходниках uGFX определяется переменная как char const* text, ей в коде выполняется присваивание text="строка", и эта строка получается в кодировке UTF-8. В моем куске кода аналогичные строки получаются в CP1251. Если в своем коде описываю переменную как extern и размещаю ее в коде uGFX то она снова получается UTF-8. Включение мultibute support на результат не влияет. Наверное где то какая то опция в хедерах uGFX поднимается, но какая? Спасибо. -

АЦП AD7124 и калибровка

Sagittarius опубликовал тема в Вопросы аналоговой техники

Здравствуйте. Очередная засада с AD7124-8, разбираюсь с калибровкой. Процесс - выдаю сброс, инициализирую, для выбранного канала провожу внутреннюю калибровку, вычитываю все регистры, смотрю результат. Как понимаю производитель откалибровал АЦП для Gain=1 (PGA=0) и записал результат в регистры gain для каждого канала? и если я произведу калибровку на тех же установках то должен получить по крайней мере близкие к стартовым. И при этом, т.к. в процессе внутренней калибровки внутренние входы АЦП отключаются от внешних, то результат должен быть не зависим от конфигурации канала (что задано как вход). Реально же наблюдаю значительные изменения в регистре gain (изменяются 2 младших байта) и при этом есть зависимость от заданной коммутации канала - если подать на вход (AVdd-AVss)/6 или (IOVdd-DGND)/6 то регистр калибровки меняется весь, получается значение порядка 0xC0xxxx. Но это при установленном PGA=0(Gain=1). Если же задать PGA=1(Gain=2) то все приходит в норму, происходит лишь небольшая коррекция регистра калибровки. Собственно вопрос - а как правильно делать? Можно проводить калибровку для усиления 1 или это не корректно? И если значение калибровки (при Gain=2) от раза к разу отличается друг от друга на 0..70 это нормально? Спасибо. -

Опа! чего то не допер сразу. А ведь в доке то стоит запятая, 13.584, это как так? Спасибо.

-

Если temperature sensor ставить на оба канала то результатом будет что то типа 0x7FFFe7, что тоже не проходит. Собственно с этой конфигурации начинал. А вот тут, вроде как форум самого AD: https://ez.analog.com/thread/94666 говорят именно про конфигурацию когда на IN+ подключают датчик а IN- на AGND. Да, по другим каналам (внешним, внутренним) приходят ожидаемые значения, там вроде как все нормально.

-

АЦП AD7124 и внутренний температурный сенсор

Sagittarius опубликовал тема в Вопросы аналоговой техники

Здравствуйте. Может кто ни будь сможет подсказать. Использую AD7124-8, пытаюсь измерить показания внутреннего температурного сенсора. На выбранном канале на "+" коммутирую сенсор, на "-" AVss. Конфиг на канал биполярный, буферизированный, референс внутренний. В принципе пробовал и всякие другие установки как по конфигу так и по фильтрам, как дефолтные так и из примеров и форума AD. Результат примерно одинаковый - результат преобразования 0xBE8xxx..0xBE9xxx что по формуле из доки дает температуру в районе 300 тысяч цельсия :-) Где то косяк, но в чем как то уже не придумывается. Может кто то сталкивался с подобным или подскажет рабочие настройки канал/конфиг/фильтр ? Спасибо. -

Здравствуйте. Такой вопрос возник. Есть многоканальная схема, что то типа основного листа, процессорной части (1 штука) и какого ни будь канала (несколько штук). Отрисовав делаю Annotate Shematic, за тем Board Level Annotate (схема наименования $ComponentPrefix$GlobalIndex). Теперь, если добавить к примеру, резистор в процессорную часть и снова сделать Annotate Schematic, то этому новому резистору будет присвоен номер, который был до этого назначен какому то компоненту канала, соответственно выполнение за тем Board Level Annotate приводит к тому, что нумерация всех резисторов каналов съезжает. На этапе первоначальной схемы ладно, терпимо. Но когда уже есть плата и надо внести изменения это как то напрягает. Очевидно какая то кривость в том, как я выполняю нумерацию. Как это делать правильно, чтоб нумерация в каналах сохранялась при изменении других частей схемы? Спасибо.

-

STM32F746 и внешняя SRAM

Sagittarius ответил Sagittarius тема в STM

О, спасибо! Коллега рядом как раз на подобное наткнулся, когда другая бага переехала из F4xx в F7xx, была в еррате на 4xx но отсутствовала в еррате на 7xx. Действительно, если прерывания запрещать то все читается нормально. -

STM32F746 и внешняя SRAM

Sagittarius ответил Sagittarius тема в STM

1. кеширование отключено 2. чтение происходит ошибочно, если, к примеру, последним в адрес base[11] было записано число 0x1234xxxx то выполненное сразу после этого чтение по адресу base[0] выдаст 0x12341234, хотя по этому адресу лежит совсем другое значение (по останову в отладчике читается правильное). При этом сам цикл чтения на шине будет отсутствовать. т.е. бага не просто в отсутствии цикла чтения на шине а в ошибочном результате самого чтения. -

STM32F746 и внешняя SRAM

Sagittarius опубликовал тема в STM

Здравствуйте. Возникла непонятная ситуация. Проц STM32F746, к нему подключено внешнее статическое ОЗУ, 16 бит данных. Скелет программы сгенерен в CubeMX, кеш на команды и данные отключен. Тест простой - сначала пишу во внешнюю RAM 12 штук 32-бит слов (используя memcpy) потом читаю в цикле по одному uint32_t. В зависимости от наличия, частоты и длительности прерываний (простой таймер и инкрементом переменной во внутреннем ОЗУ), паузы между записью и чтением, уровнем оптимизации кода при компиляции иногда происходит сбой - циклов записи на внешней шине всегда 12 а вот циклов чтения иногда проскакивает только 11 (отсутствует выдача сигналов CS и OE). Судя по всему аппаратура проца пропускает первый запрос на чтение, при этом результатом самого чтения оказывается значение, которое последним записывалось во внешнюю RAM (продублированные последние записываемые 16 бит). В зависимости от каких то шаманских действий частота сбоев может быть от 1-2 в секунду до 1-го за 7-8 часов. Пробовал собирать проект в IAR и Keil. Может будут у кого какие мысли по этому поводу? Спасибо. -

пошаговый режим и прерывания

Sagittarius опубликовал тема в Keil

Здравствуйте. Ниже была похожая тема, но там у ТС проблема что в IRQ было не попасть :-) у меня на оборот заведено периодическое прерывание 6-го таймера и отладчик в пошаговом все время попадает туда. В том же IAR это решалось опцией в настройках, а как тут? MDK ARM 5.17, проц STM32F746 + ST-Link/V2. Драйвера и прошивку обновил. Спасибо. -

Спасибо. Другими словами, мой пример просто некорректен с самого начала, а такие конструкции надо реализовывать через if-else, case и пр. ?

-

Verilog, неблокирующее присваивание

Sagittarius опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Здравствуйте. Изучаю Verilog, возник вопрос, который не понимаю. пример счетчик 0-10: === module test1(clk, count); input clk; output reg[7:0]count; always @(posedge clk) begin count <= count + 8'b1; if (count == 8'b00001010)count <= 0; end endmodule что на него сгенерил Quartus: меняю строки в always блоке местами: always @(posedge clk) begin if (count == 8'b00001010)count <= 0; count <= count + 8'b1; end исчезает условие проверки на 8'hA: Вот никак не пойму - почему так? вроде в данном случае результат не должен зависеть от последовательности строк? Спасибо. -

темная сторона силы, асинхронные схемы :rolleyes: давно не работал с FPGA, со времен Max plus+, может быть просто привык :-D освою таймквест и тоже буду rtl обходиться.

-

Спасибо, хоть что то стало прояснятся ... test_family... на max10 выдал 0, хотя это семейство устанавливалось (q16.0), на maxv выдало 1, но раз базы пусты то грустно, а как раз под него тест на gate level simulation и делал. а как включить для max10? Почитал Quartus II Scripting Reference Manual так вроде нет такой магии как "test_family_trait_of" - где про это пишут?

-

опаньки ... а тогда вопрос - как отмоделить схему на пример в Max10 или циклон II ? вообще никак?