cpl

Свой-

Постов

385 -

Зарегистрирован

-

Посещение

Весь контент cpl

-

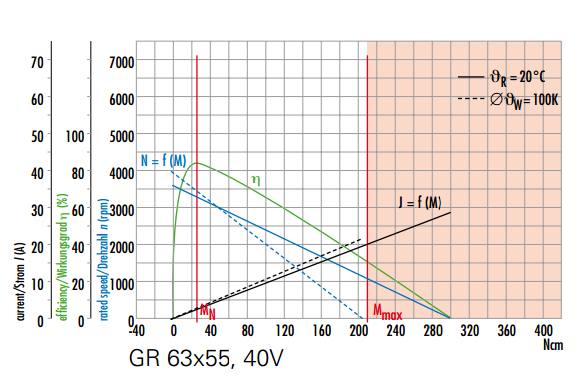

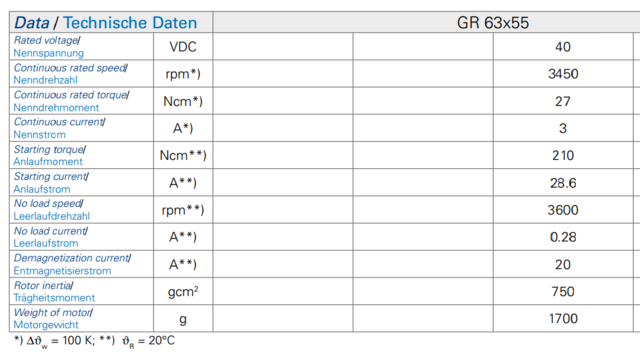

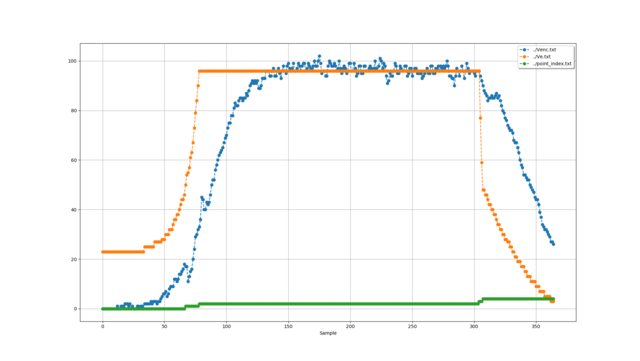

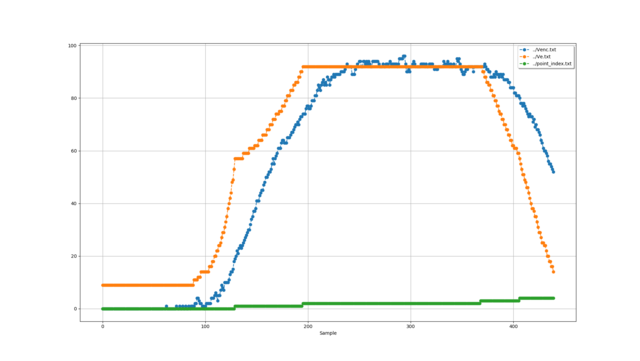

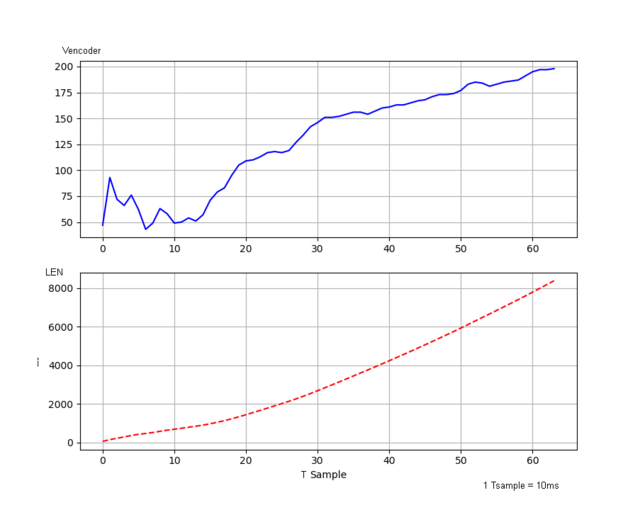

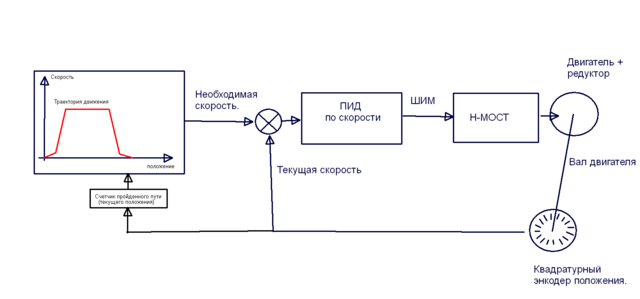

Здравствуйте коллеги ! Прощу помощи разобраться, что к чему... Поручили мне разработку софта контроллера управления автоматическими дверями. Это мой первый проект с ТАУ. Устройство механизма следующее: Две створки, через ролики подвешиваются на рельсу, по которой осуществляется перемещение. Сами створки крепятся в ремню. На одном конце устанавливается двигатель постоянного тока с редуктором, на другом натяжной ролик. В крайних положения есть упоры. На валу двигателя установлен квадратурный энкодер. По электроники: Микроконтроллер по средствам ШИМ управляет Н-Мостом к которому подключен ДПТ (100Вт). Микроконтроллер получает данные от: квадратурного энкодера(текущая скорость, и подсчет пройденного пути), АЦП датчика тока в цепи мотора и АЦП входного питающего напряжения. Алгоритм калибровки(первый запуск): 1. Измерение длинны пути от края до края. 2. Реакция системы на ступенчатое воздействие. Из крайнего положения производится ускоренное движение до 1/3 пути. По отклику системы по методу Циглера–Никольса программно определяются параметры ПИД регулятора скорости. По тз длинна может быть разной, масса створок тоже заранее не известна. Параметры двигателя известны, количество шагов энкодера тоже (500 ед. на оборот). Штатная работа: Весь участок делиться на 5 частей: плавный старт, разгон, равномерное движение, торможение, медленное доведение до крайней точки(чтобы створка не ударялась об упор или друг об друга). Реализация: Что получается есть ПИД регулятор по скорости, на вход которого подаются значения уставки скорости из таблицы. Т.е. зная текущее положение двери -> выдается значение уставки скорости. И все бы хорошо, но есть большая задержка между тем что выдал ПИД и тем как это отрабатывает мотор. При разгоне это не критично, а вот при подходе к крайней точке скорость оказывается слишком велика что приводит к удару. Т.е. в текущем варианте реализации получаемая(реальная) скорость как бы соответствует теоретической скорости уставки но сдвинутой на величину задержки. Вопрос как побороть или учесть задержку ? На графиках: Желтый - уставка скорости, Синий - реальная скорость с энкодера, Зеленый - участок пути. Резкий сброс скорости ПИД, до половины. Плавное снижение скорости: VПИД=10, Vэнкодера=55 ! Если на участке торможения замкнуть двигатель на землю то дверь производит резкую остановку в несколько раз быстрее чем по ПИД. Получается торможение двигателем по ПИД не эффективно, мотор ведет себя как "ватный". Не совсем разобрался с эффектом, но получается двигатель превращается в генератор и это не дает ему погасить скорость ? (т.к. двери толкают мотор по инерции). Такая схема построения регулятора корректна, а то берут сомнения ? Вопрос что нужно сделать чтобы точно приходить в конечную точку с заданной скоростью ? Правильно ли я понимаю что необходимо переходить к подчиненному управлению, для улучшения точности регулирования ? и добавить еще один ПИД регулятор по положению, а то что у меня сейчас реализовано (управление по положению), это получилось разомкнутое управление ? На сколько поможет если использовать три контура (третий по току) ?

-

вариант реализации передачи UDP пакета: https://lab85.ru/index.php/laboratoriya-stati/30-ethernet-peredacha-paketa

-

Gowin_V1.9.8 В списке M25P80 нет, поэтому Generic Flash.

-

Для информации: M25P80 не прошивается через jtag (ft2232h).... Плата своя: GW2A18QFN88 + M25P80. Программатор SPI FLASH не видит.... (SRAM загружает без проблем). Поставил winbond (то что было под рукой W25Q32BV) работает...

-

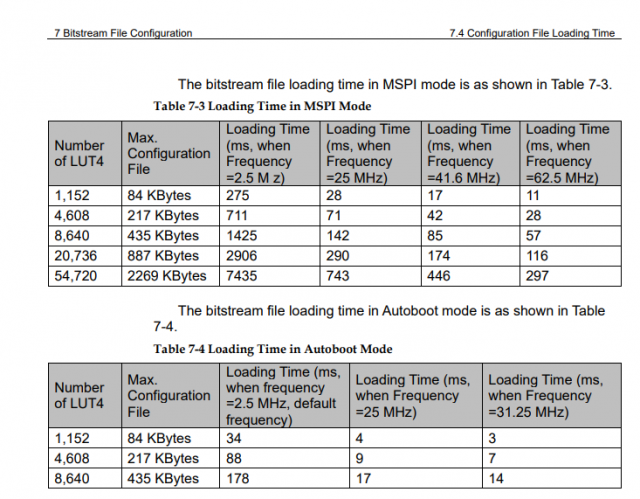

Для GW2A-LV18PG256S. А как определить достаточный объем SPI FLASH, если в документации не указано ? К примеру у меня есть M25P80 (1M x 8), её хватит или нет ? Разобрался, нашел, таблицу с указанием объема необходимой конфигурационной флеши.

-

Какие SPI FLASH подходят для GW2A в качестве загрузочных ? Минимальный размер, фирмы производители, ограничения может есть какие ? Искал в разделе документации на сайте и не нашел...

-

Точно так и есть, отрабатывал глобальный ресет. Спасибо.

-

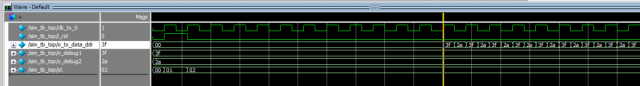

Моделирую вывод DDR данных.(Spartan 6, QuestaSim) Наткнулся на странное поведение компонента ODDR2. При старте моделирования ПЕРВЫЕ данные на выходе ODDR2 появляются только через 12 тактов, до этого 00. Не пойму в чем причина, что не так делаю ? тестбенч прилагаю. `timescale 1ns / 1ps module top( input wire i_clk_tx_0, input wire i_clk_tx_180, input wire i_rst, output wire [5:0] o_tx_data_ddr , output wire [5:0] o_debug1 , output wire [5:0] o_debug2 ); reg tx_ce = 1; // CE для ODDR2 reg [23:0] fifo_rd_data = 24'b1111_11__00_0001__1010_10__00_0010; wire [5:0] d0; wire [5:0] d1; reg rst = 0; assign d0 = fifo_rd_data[23:18]; assign d1 = fifo_rd_data[11:6]; reg [4:0] st = 0; reg [1:0] empty_cnt = 0; reg [7:0] delay = 0; always @(posedge i_clk_tx_0) begin case(st) 0: begin delay <= delay + 1'b1; if (delay == 2) begin delay <= 0; // rst <= 0; st <= st + 1'b1; end else begin // rst <= 1; end end 1: begin delay <= delay + 1'b1; st <= st + 1'b1; end 2: begin $display("fifo_rd_dataR = 0x%x 0x%x 0x%x 0x%x", fifo_rd_data[23:18], fifo_rd_data[17:12], fifo_rd_data[11:6], fifo_rd_data[5:0]); fifo_rd_data[23:12] <= fifo_rd_data[23:12] + 1'b1; fifo_rd_data[11:0] <= fifo_rd_data[11:0] + 1'b1; if (delay == 100) st <= 3; else st <= 1; end 3: begin end default: st <= 0; endcase end ODDR2 #( .DDR_ALIGNMENT("C1"), // Sets output alignment to "NONE", "C0" or "C1" .INIT(1'b0), // Sets initial state of the Q output to 1'b0 or 1'b1 .SRTYPE("SYNC") // Specifies "SYNC" or "ASYNC" set/reset ) ODDR2_inst0 ( .Q ( o_tx_data_ddr[0] ), // 1-bit DDR output data .C0 ( i_clk_tx_180 ), // 1-bit clock input .C1 ( i_clk_tx_0 ), // 1-bit clock input .CE ( 1'b1), // 1-bit clock enable input // .CE ( tx_ce), // 1-bit clock enable input .D0 ( d0[0]), // 1-bit data input (associated with C0) .D1 ( d1[0]), // 1-bit data input (associated with C1) .R ( rst), // 1-bit reset input .S ( 1'b0) // 1-bit set input ); ODDR2 #( .DDR_ALIGNMENT("C1"), // Sets output alignment to "NONE", "C0" or "C1" .INIT(1'b0), // Sets initial state of the Q output to 1'b0 or 1'b1 .SRTYPE("SYNC") // Specifies "SYNC" or "ASYNC" set/reset ) ODDR2_inst1 ( .Q ( o_tx_data_ddr[1] ), // 1-bit DDR output data .C0 ( i_clk_tx_180 ), // 1-bit clock input .C1 ( i_clk_tx_0 ), // 1-bit clock input .CE ( 1'b1), // 1-bit clock enable input // .CE ( tx_ce), // 1-bit clock enable input .D0 ( d0[1]), // 1-bit data input (associated with C0) .D1 ( d1[1]), // 1-bit data input (associated with C1) .R ( rst), // 1-bit reset input .S ( 1'b0) // 1-bit set input ); ODDR2 #( .DDR_ALIGNMENT("C1"), // Sets output alignment to "NONE", "C0" or "C1" .INIT(1'b0), // Sets initial state of the Q output to 1'b0 or 1'b1 .SRTYPE("SYNC") // Specifies "SYNC" or "ASYNC" set/reset ) ODDR2_inst2 ( .Q ( o_tx_data_ddr[2] ), // 1-bit DDR output data .C0 ( i_clk_tx_180 ), // 1-bit clock input .C1 ( i_clk_tx_0 ), // 1-bit clock input .CE ( 1'b1), // 1-bit clock enable input // .CE ( tx_ce), // 1-bit clock enable input .D0 ( d0[2]), // 1-bit data input (associated with C0) .D1 ( d1[2]), // 1-bit data input (associated with C1) .R ( rst), // 1-bit reset input .S ( 1'b0) // 1-bit set input ); ODDR2 #( .DDR_ALIGNMENT("C1"), // Sets output alignment to "NONE", "C0" or "C1" .INIT(1'b0), // Sets initial state of the Q output to 1'b0 or 1'b1 .SRTYPE("SYNC") // Specifies "SYNC" or "ASYNC" set/reset ) ODDR2_inst3 ( .Q ( o_tx_data_ddr[3] ), // 1-bit DDR output data .C0 ( i_clk_tx_180 ), // 1-bit clock input .C1 ( i_clk_tx_0 ), // 1-bit clock input .CE ( 1'b1), // 1-bit clock enable input // .CE ( tx_ce), // 1-bit clock enable input .D0 ( d0[3]), // 1-bit data input (associated with C0) .D1 ( d1[3]), // 1-bit data input (associated with C1) .R ( rst), // 1-bit reset input .S ( 1'b0) // 1-bit set input ); ODDR2 #( .DDR_ALIGNMENT("C1"), // Sets output alignment to "NONE", "C0" or "C1" .INIT(1'b0), // Sets initial state of the Q output to 1'b0 or 1'b1 .SRTYPE("SYNC") // Specifies "SYNC" or "ASYNC" set/reset ) ODDR2_inst4 ( .Q ( o_tx_data_ddr[4] ), // 1-bit DDR output data .C0 ( i_clk_tx_180 ), // 1-bit clock input .C1 ( i_clk_tx_0 ), // 1-bit clock input .CE ( 1'b1), // 1-bit clock enable input // .CE ( tx_ce), // 1-bit clock enable input .D0 ( d0[4]), // 1-bit data input (associated with C0) .D1 ( d1[4]), // 1-bit data input (associated with C1) .R ( rst), // 1-bit reset input .S ( 1'b0) // 1-bit set input ); ODDR2 #( .DDR_ALIGNMENT("C1"), // Sets output alignment to "NONE", "C0" or "C1" .INIT(1'b0), // Sets initial state of the Q output to 1'b0 or 1'b1 .SRTYPE("SYNC") // Specifies "SYNC" or "ASYNC" set/reset ) ODDR2_inst5 ( .Q ( o_tx_data_ddr[5] ), // 1-bit DDR output data .C0 ( i_clk_tx_180 ), // 1-bit clock input .C1 ( i_clk_tx_0 ), // 1-bit clock input .CE ( 1'b1), // 1-bit clock enable input // .CE ( tx_ce), // 1-bit clock enable input .D0 ( d0[5]), // 1-bit data input (associated with C0) .D1 ( d1[5]), // 1-bit data input (associated with C1) .R ( rst), // 1-bit reset input .S ( 1'b0) // 1-bit set input ); assign o_debug1 = d0; assign o_debug2 = d1; endmodule ODDR2_test.zip

-

ADSP-BF518BSWZ-4F4

cpl ответил Victor1963 тема в Продам

Здравствуйте, год выпуска? какая ревизия ? -

Отладочная плата StarterKit SK-iMX53. Комплект: Плата + СД диск. Состояние: Отличное. Стоимость: 4000 руб. +79162127280

-

Продана, просьба закрыть тему.

-

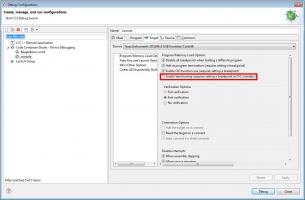

Нашел проблему, (потратив несколько дней.... новый проц новые приключения, да еще в бареметале.....) Debug configurations -> вкладка Target -> галка Enable Semihosting (requires setting a breakpoint at SVC_Handler) галку нужно УБРАТЬ. :smile3046:

-

Здравствуйте, Есть плата BeagleBone(белая) с отладчиком на борту (XDS100v2). Процессор XAM3359. Среда Win7, CCS v6.2 компилятор GCC gcc-arm-none-eabi-4_9-2015q3. ПО собираю из исходников AM335X_StarterWare_02_00_01_01, пытаюсь вызвать программное прерывание, но не происходит перевода на обработчик. программа запускается из DDR (gel делает инит переферии и т.п.), таблица векторов располагается в RAM 0x4030FC00. при вызове asm volatile("swi #458752"); процессор переходит по адресу 0x4030FC08, там он должен загрузить адрес подпрограммы SVC_Handler но заместо этого возвращается на сл. команды после вызова swi #458752. При этом IRQHandler, AbortHandler работают. main(){ while(1) asm volatile("swi #458752"); } SVC_Handler: b SVC_Handler /****************************************************************************** ** INTERNAL VARIABLE DEFINITIONS *******************************************************************************/ const unsigned int AM335X_VECTOR_BASE = 0x4030FC00; static unsigned int const vecTbl[14]= { 0xE59FF018, /* Opcode for loading PC with the contents of [PC + 0x18] */ 0xE59FF018, /* Opcode for loading PC with the contents of [PC + 0x18] */ 0xE59FF018, /* Opcode for loading PC with the contents of [PC + 0x18] */ 0xE59FF018, /* Opcode for loading PC with the contents of [PC + 0x18] */ 0xE59FF014, /* Opcode for loading PC with the contents of [PC + 0x14] */ 0xE24FF008, /* Opcode for loading PC with (PC - 8) (eq. to while(1)) */ 0xE59FF010, /* Opcode for loading PC with the contents of [PC + 0x10] */ 0xE59FF010, /* Opcode for loading PC with the contents of [PC + 0x10] */ (unsigned int)Entry, (unsigned int)UndefInstHandler, (unsigned int)SVC_Handler, (unsigned int)AbortHandler, (unsigned int)IRQHandler, (unsigned int)FIQHandler };

-

Продам две отладочные платы, обе рабочие: TMDXLCDK138 OMAP-L138 Development Kit (LCDK) - 1 шт HAWKBOARD OMAP-L138 - 1 шт 6000 руб за обе платы. email: sgot () inbox.ru

-

1. Перед тем как запустить сборку все дополнительные пакеты установили ? 2. Используемая версия YOCTO совместима с версией линукса на ПК ?

-

Часть параметров можно передать ядру при загрузке, в виде текстовой строки (uboot). Команды можно подавать через консоль (загрузить/выгрузить драйвер, запустить пользовательское ПО, посмотреть состояние и т.д.) Драйвер можно собрать как отдельно от ядра так и в месте с ядром. Если вы используете дистрибутив от аналог девайса то пересобрать ядро + файловую систему не составит труда. >P.S. Еще вопрос. А можно ли подключится к терминалу через usb? Т.е. запустив Terminal на компе и подключив плату через usb-кабель. можно и даже нужно. >И еще проясните момент один. Как я понял из книги, в линукс есть драйвера уровня пользователя и драйвера уровня ядра. Драйвер дисплея и клавиатуры желательно делать на каком уровне? Драйвер должен быть на уровне ядра. В ядре есть драйвер для управления дисплеем в нем прописаны все параметры, измените на свои.

-

VGA to ADC.

cpl ответил sgot тема в Аудио/Видео интерфейсы

Мне помогло, хотя шум еще остается. -

Внешне похоже на правду т.к. в данном описание есть описание регистров noise filtra которого нет вообще в sprugu8c и т.п. Спасибо буду разбираться. За полтора года общения - бодания, почувствовал . . . Кто может сказать ? Как обстоят дела у freescale с документацией и тех поддержкой (в частности интересует IMX6) ? т.к. на перспективу надо будет переходить с TI. . .

-

DM365 Документация под NDA.

cpl опубликовал тема в Сигнальные процессоры и их программирование - DSP

Здравствуйте Разрабатываем устройство на DM365 + CMOS матрица, Собрали макет, дошли до работы с CMOS матрицей (коррекция цвета, экспозиция, битые пикселы), выяснилось что в документе: TMS320DM36x Digital Media System-on-Chip (DMSoC) Video Processing Front End (VPFE) User's Guide sprufg8c.pdf нет описания на данные модули... На форуме техаса сказали что описание модулей есть в документе: TMS320DM36x Digital Media System-on-Chip (DMSoC) Video Processing Front End (VPFE) User's Guide. The document number is: SPRUGU5B Который находится под NDA, обращайтесь в местное отделение TI. Запросили отделение TI (Москва), в ответ присылают документ sprufg8c.pdf и говорят что это новый документ (лежит в открытом доступе и т.п.) в замен старого SPRUGU5B, пробовали объяснять что в нем отсутствует необходимое описание и что сам техас ссылается на SPRUGU5B.pdf под NDA ! В ответ ТИШИНА... Вопрос где взять документ: TMS320DM36x Digital Media System-on-Chip (DMSoC) Video Processing Front End (VPFE) User's Guide. The document number is: SPRUGU5B Понятно что документация под NDA, Вопрос с тем кто уже получил данный документ: К кому обращаться, через кого получали ? какие условия ? PS. Жалко времени, потратили год чтобы разобраться и запустить все это хозяйство, несколько месяцев на переписку в поисках документации и теперь тупик. :1111493779: -

MAX10 security bit

cpl ответил cpl тема в Работаем с ПЛИС, области применения, выбор

Спасибо за ответ, Verify protect - выставил. Шифрование прошивки пока не требуется. -

MAX10 security bit

cpl опубликовал тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте Хочу закрыть доступ к MAX10 по jtag интерфейсу, но при этом была возможность перепрошить кристалл заново, не могу выставить security bit в программаторе, т.к. он не активен. Среда Quartus 15.1. Как включить security bit ? -

1)используйте else 2) mkdir