-

Постов

2 052 -

Зарегистрирован

-

Посещение

Весь контент Krys

-

Ещё некоторая дополнительная информация от моего коллеги, что невозможно на RTL написать соединение PCOUT -> PCIN, если эти порты находятся в разных модулях: https://forums.xilinx.com/t5/Welcome-Join/C...ros/td-p/754013

-

Комлексное умножение

Krys ответил FatRobot тема в Алгоритмы ЦОС (DSP)

Делал комплексный умножитель на 36 битов из вещественного умножителя на 36 битов (описан в доке на DSP48) , там оказалось, что выгоднее по числу DSP-блоков реализовать комплексное умножение в лоб по определению. -

А откуда следует, что умножение на синусоиду и последующую децимацию-фильтрацию можно заменить на децимацию-фильтрацию с синусом? И откуда следует, что потом ещё нужен доворот на линейно нарастающую фазу? А такой поворот на линейно нарастающую фазу не является ли синусом? Не пробовали в матлабе отмоделировать?

-

Короче победил я эту штуку... не в лоб, конечно, как хотелось... Я просто переконфигурил ту DCM-ку на рисунке из первого поста, чтобы у неё не было обратной связи, т.е. убрал галочку source sycnhronous. Соответственно, нет цепи - нет и конфликта )) Конечно, такое решение не для всех проектов пригодно, вдруг кому-то надо клок на выходе, синхронный с входом.

-

Ну вобщем Вы отчасти правы, но и я правильно ответил ))) Дело в том, что тот самый писиайный егошный клок просто подаётся внутрь корки, и внутри самой корки нет BUFG и соответственно он никак не законстрейнен. Но вообще BUFG конечно для этого клока есть, просто снаружи. И создался он, как я понимаю, автоматически, когда я подключил сигнал с тактовой ножки ПЛИС на тактовый вход всех триггеров корки. Естественно плейсер догадался, что неплохо было бы и BUFG поставить )) Ну в любом случае же ни один сигнал писяй не меняется быстрее тактовой, т.е. 33МГц?

-

Не, корка PCI - она же довольно тупая и примитивная, там же 33МГц )) Там нет в принципе ни одного перечисленного элемента - DCM, MMCM, BUFG, BUFIO. LOC атрибутов тоже нету, всё разводится типа на автомате - полная свобода для творчества ))

-

Так-то возможность есть, утилизация неплотная. Просто знать бы что двигать. Как я писал сообщением ранее, проблема возникла у сигналов, никак не связанных с внедрённой PCI-коркой, просто она что-то подвинула. И уже подвинутый сигнал вызвал коллизию. А найти эту взаимосвязь довольно сложно...

-

В том-то и дело, что ругается на сигналы, никак не связанные с PCI. Просто корка PCI расталкивает другие цепи, и взаимосвязь установить довольно сложно. Я конечно буду пытаться искать... двигаться-то по проекту надо...

-

Пока результаты такие. Открыл FPGA Editor в двух окнах: со старым проектом, в котором всё красиво, и с проектом после изменений. Начал вести руками ту цепь, которая не хотела разводиться. Вёл тем же маршрутом, что и в старом проекте, подсматривая в соседнее окно. Благо число пересечений там небольшое, и можно за 10 минут развести. Вёл-вёл, пока не упёрся в один из многочисленных switch-box-ов, на котором стало видно, что тот выход этого свичбокса, где был мой сигнал в старом проекте, в новом проекте занят другим сигналом. При том другой сигнал не из числа вновь добавленных элементов в новом проекте. Похоже вновь добавленные элементы потеснили старый сигнал, и он занял другое место. Я не долго думая удалил разводку того сигнала, который залез в свичбоксе на чужое место. После этого для моей цепи дал команду autoroute. Цепь развелась полностью, тем самым маршрутом, как и в старом проекте. Теперь я дал команду autoroute для того сигнала, который залез на чужое место. И в результате выдало ошибку, мол, развёл частично, не смог подвести цепь к таким-то элементам. Эти элементы находятся как раз в том же районе, что и проблемный свичбокс, из-за которого подрались сигналы )) Вот теперь сижу чешу репу, как эти сигналы подружить. Видно, что на свичбоксе много пустых выходов, но почему-то по ним эта цепь, которая залезла на чужое место, идти не хочет, видимо дальше линии идут не в те места. Передвинуть в другой регион элементы, до которых не дотянулся этот сигнал, не могу, т.к. они идут на рядом находящиеся ноги плис.

-

RobFPGA, спасибо за подсказку, но у нас обычный PCI, так что не подходит... Подскажите, пожалуйста, как посмотреть конфликты BUFG и BUFIO? Как я писал в предыдущем сообщении, я смотрел согласно документу UG382, Clocking resources - вроде ничего и не нарушается... Но мог что-то и упустить конечно...

-

Большое спасибо за такой развёрнутый ответ! Пробовал этот параметр менять и даже добавил все возможные стратегии разводки ну типа вот так: и попробовал все, каждая выдала одинаковую ошибку. Да, я тоже к этому бы хотел стремиться. Тем более, что проект развивается, и не будешь же при каждом изменении так каждый раз плясать с бубномFPGA Editor-ом ))) Было добавлено ядро PCI в виде корки XPS (внутри потроха в виде ngc, и туда не залезть). Больше собственно ничего не было добавлено. И ноги в ucf перекинуты. Чую, что у PCI корки добавился один клок, который где-то не лезет по каким-то путям. Где-то не хватает трассировочных ресурсов. Точнее не так. Нарисованная на картинке в первом сообщении DCM-ка совершенно не связана с PCI-коркой, и была там всегда. Видимо PCI-корка заняла какие-то трассировочные ресурсы и вытеснила сигнал clkfb у DCM-ки. Как говорится была у зайца избушка лубяная, а у лисыPCI-корки ледяная ))) Главно что согласно документу UG382, Clocking resources вроде ничего и не нарушается... Где-то ещё есть узкое местечко...

-

Подскажите, пожалуйста, поподробнее, как это сделать. Или в каком датащите весь этот алгоритм прописан?

-

Я сравнивал с предыдущим проектом до изменений. Указанные проблемные компоненты находятся на тех же местах, так что условия полностью те же.

-

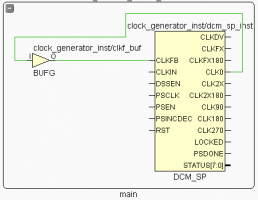

Здравствуйте. Есть проблемка. Хочу заставить Planahead скушать результаты частичной разводки в FPGA Editor. У меня в Planahead не разводится 1 цепь, попытался её вручную развести в FGPA Editor и подсунуть планахеду. Но он всё делает так, как будто ничего не съел. Предыстория: Плисина xc6slx100tfgg484-3, используется Planahead и XPS. После добавления определённого функционала и изменения ног в *.ucf перестала разводиться одна цепь. В проекте есть такая DCM-ка: С выхода нарисованного на картинке BUFG сигнал в действительности подаётся не сразу на вход CLKFB этой DCM-ки, а проходит через буфер BUFIO2FB. Этот буфер вставляется средой автоматически (UG382, Clocking resources, стр. 55: "The ISE Design Suite automatically inserts matching BUFIO2FB and BUFIO2 buffers when the CMT feedback path is used."). Так вот если я обычным образом запускаю разводку в планахеде, то цепь от BUFG до BUFIO2FB не разводится. Говорит следующее: 1 signals are not completely routed. See the module_1_stub_routed.unroutes file for a list of all unrouted signals. WARNING:Par:100 - Design is not completely routed. There are 1 signals that are not completely routed in this design. See the "module_1_stub_routed.unroutes" file for a list of all unrouted signals. Check for other warnings in your PAR report that might indicate why these nets are unroutable. These nets can also be evaluated in FPGA Editor by selecting "Unrouted Nets" in the List Window. В указанном файле имеется следующее содержимое: 1 signals are not completely routed. WARNING:ParHelpers:360 - Design is not completely routed. module_1_i/blablabla/main_inst/clock_generator_inst/clkfb , где clkfb - это и есть тот самый сигнал обратной связи, что и на картинке выше. Я решил на ещё неразведённом проекте сделать предварительную разводку этих проблемных цепей в FPGA Editor-е, а уже затем отдать всё обратно планахеду. Для этого я в планахеде нажал на свою стратегию impl1 правой кнопкой, затем launch next step to MAP. После MAP у меня появился файл с расстановкой компонентов, но без разводки: module_1_stub.ncd. Открыл его FPGA Editor-ом, нашёл нужные мне цепи (до и после BUFIO2FB), нажал кнопку Autoroute. Они развелись. Затем нажал Attrib и установил у каждой из них Locked и Priority. Нажал сохранить. После этого у меня обновились файлы module_1_stub.ncd (где появилась разводка только 2х цепей - это я проверил открытием файла повторно в FPGA Editor-е) и module_1_stub.pcf, где добавились мои атрибуты: ... SCHEMATIC END; NET "module_1_i/blablabla/main_inst/clock_generator_inst/clkfb" LOCK; NET "module_1_i/blablabla/main_inst/clock_generator_inst/clkfb" PRIORITIZE = 100; // fpga_editor - P.20131013 - Tue Jul 19 13:34:37 2016 NET "module_1_i/blablabla/main_inst/clock_generator_inst/dcm_sp_inst_ML_NEW_O" LOCK; NET "module_1_i/blablabla/main_inst/clock_generator_inst/dcm_sp_inst_ML_NEW_O" PRIORITIZE = 99; После этого я надеялся подсунуть эти результаты планахеду. Нажал на стратегии правой кнопкой и дальше launch next step to PAR. Всё запустилось, в логах PAR написало, что вроде как подхватило все нужные файлы: *** Running par with args -intstyle pa "module_1_stub.ncd" -w "module_1_stub_routed.ncd" -ol high -mt 4 Constraints file: module_1_stub.pcf. ... Но результат тот же, что и раньше, т.е. одна неразведённая цепь, та же самая. Я ещё раз открыл module_1_stub_routed.ncd в FPGA Editor-е и увидел, что моя цепь до BUFIO2FB является неразведённой. Т.е. это значит, что Planahead либо вообще не увидел, что я ему подсунул в module_1_stub.ncd и module_1_stub.pcf, либо увидел, но проигнорировал, и в результате собственной разводки отцепил разведённое мною и переразвёл по-своему. Вот мой вопрос и состоит в том, как заставить Planahead скушать результаты частичной разводки в FPGA Editor? Либо другой вопрос: как развести и сделать рабочим мой проект возможно каким-то другим способом, не через FPGA Editor? Ведь, видимо, раз эта цепь не разводится, значит, среде что-то не нравится, только она сказать не может (как умная собака ))) ).

-

Тут вот тоже ненавистные синтезатору $rtoi встречаются )))

-

Именно так, для округления. Спасибо за подсказку.

-

И вообще верилог )))

-

Решил проблему генерацией корки, вызвав coregen отдельным приложением из пускового меню. Это конечно не победа, а всего лишь обходной путь, но всё же, хоть так можно работать...

-

Timmy, спасибо, попробую.

-

Intekus большое спасибо! Я попробую ) Вы могли бы подсказать, как обойти такую запись:localparam ACK_MIN_DUR_OUT = $rtoi(ACK_MIN_DUR_IN * CLK_RATIO + 0.5); Здесь CLK_RATIO может быть рациональным числом. Если я напрямую подставлю это в качестве ширины шины например, то будет ругаться, что только целые ему подавай.

-

Здравствуйте. Кто-нибудь может поделиться: нужны самодельные функции взамен системных для Verilog типа $clog2, $rtoi и т.д., а то тут внезапно выяснилось, что под старыми ПЛИСами xst не всё поддерживает. Берём одни и те же исходники, делаем синтез под spartan 6 - всё прекрасно. Меняем тип ПЛИС в свойствах проекта на Virtex 4 - синтезатор ругается на эти системные функции.

-

Здравствуйте. Подскажите плиз, как можно порешать: при создании корки FIFO в Coregen Planahead вылазит такая вот ошибка [Common 17-11] Failed to parse xmsgs file _xmsgs/cg.xmsgs - No element found Находил подобную же проблему: https://forums.xilinx.com/t5/Embedded-Devel...ead/td-p/318471 Но ответа там не было...

-

Спасибо откликнувшимся. Мне это не просто для развлекухи надо было, а для математического обоснования при составлении одного документика

-

Здравствуйте. Вопросик в качестве разминки для мозгов: Как математически доказать, что число 2^x может быть поделено нацело только числом вида 2^y, где y<=x, и никаким другим числом не может (или наоборот может и ещё есть какие-то числа)? Т.е. например число 2 в 12 степени это 4096 нацело делится двойкой в любой степени до 12 и ничем другим. Т.е. для меня важно доказать, что нет ничего другого, кроме 2^y

-

PlanAhead - запуск bitgen

Krys ответил dsmv тема в Среды разработки - обсуждаем САПРы

Да, думаю, так можно. Вопрос в первую очередь касался гуя. Можно ли где-то в гуе поставить какую-то галочку, чтобы запустился битген?...