komah

Участник-

Постов

50 -

Зарегистрирован

-

Посещение

Весь контент komah

-

IODELAY на GoWin

komah ответил iiv тема в Работаем с ПЛИС, области применения, выбор

Попробую оживить тему. А есть простой способ получить на GW1 задержку больше, чем 128*30 пс, например, 6 нс, без PLL или DLL? Например, блок DLLDLY - дает 256 элементов в линии задержки. А сколько таких блоков на кристалле, столько же, как и DLL? Или они синтезируются по мере надобности из стандартных ячеек? -

Посмотрел внимательнее, 6730 - это 6,73 нс. Удобно, конечно, если требуемая задержка сразу в секундах задается. Но непонятно, с какой дискретностью ее можно реально установить.

-

Приветствую! Есть кусок проекта для Cyclone IV, там используется блок altpll с параметром clk0_phase_shift = "6730". Никто не знает, как это значение вычисляется в конструкторе? Хотелось бы понять, сколько это в градусах, долях периода, еще в чем-нибудь. Входная частота, коэффициенты умножения и деления известны. Ну и вдогонку второй вопрос - clk0_duty_cycle равен 56. Для чего это может быть сделано? Сигнал используется для чтения данных с параллельного АЦП в режиме DDR.

-

Это же разные вещи. Антенна обеспечивает прием/излучение сигнала в двух (возможно) ортогональных поляризациях - разнесение по поляризации. Про отсчеты и задержки она ничего не знает. Лучше, хуже - не ее вопрос. Если F - разъемы на 75 Ом, то с 50 Ом они согласуются хуже, чем с 75. RG-58 это тонкий кабель с большим затуханием, особенно дешевый. А толстый 50-омный кабель на такие частоты - это дорого. Вот производитель антенн и дает возможность использовать более доступный 75-Омный. Естественно, при подключении к 50-омному оборудованию будет рассогласование. Что хуже - рассогласование или затухание, нужно решать на месте. Для приемника рассогласование не особо критично, для передатчика - по разному может быть. Имеется в виду - наведение по углу места / азимуту? Или настройка по поляризации? Для решения первой задачи ДН нужна соответствующая - см. моноимпульсный пеленгатор. Без поляризации - это как? В смысле, в оба канала один сигнал подавать?

-

Похоже, что обе антенны с X - поляризацией, могут работать в паре. Разъем 75 Ом - скорее всего, чтобы можно было "толстый" SAT кабель на 75 Ом использовать, он дешевле и выбор больше, чем на 50. Если на роутере выход 50 Ом, будет рассогласование. Но разница в цене кабеля может его победить 🙂 Наверняка можно. Крутить вправо/влево.

-

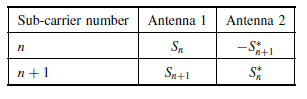

В LTE и Wimax используется SFBC - space–frequency block code. На первую антенну символы идут без изменений. На вторую - с перестановкой. K. Fazel and S. Kaiser, Multi-Carrier and Spread Spectrum Systems Second Edition

-

Вытащить биты из фазового демодулятора

komah ответил repstosw тема в Алгоритмы ЦОС (DSP)

А какой нужен диапазон, чтобы не было разрывов? И что переполнилось в первом разрыве на первом рисунке? -

Вытащить биты из фазового демодулятора

komah ответил repstosw тема в Алгоритмы ЦОС (DSP)

На первом графике могут быть разрывы, обусловленные тремя причинами: 1. Некорректным преобразованием 7-bit signed в 8-bit signed 2. Пропуском отсчетов при считывании из буфера 3. Периодичностью арктангенса. Они явно видны. Если смущают циферки на вертикальной оси - не надо на них смотреть. Первые две причины победил ТС. Третью победил unwrap. -

Вытащить биты из фазового демодулятора

komah ответил repstosw тема в Алгоритмы ЦОС (DSP)

Убирает разрывы на графике полной фазы, возникающие из-за того, что арктангенс возвращает значения в диапазоне от -Pi до Pi. Разность мгновенных фаз между соседними отсчетами не должна превышать Pi, если она больше - добавляется или вычитается 2Pi. В данном случае (детектор ЧМ) целиком восстанавливать полную фазу не нужно, достаточно скорректировать разность фаз. -

Вытащить биты из фазового демодулятора

komah ответил repstosw тема в Алгоритмы ЦОС (DSP)

Отвечу за ТС 😉 Да, прокатит. Там ЧМ с непрерывной фазой. -

HART FSK протокол

komah ответил dips11 тема в Алгоритмы ЦОС (DSP)

Если стартовый бит - низкий уровень (0), то проблем никаких. Преамбула дает 1 на выходе RxD, подключенное устройство ждет стартового бита, пока его нет - никакие биты не считает. 11 бит - это, очевидно, без преамбулы. 5 и более преамбул вида FF - это ведь больше 11? -

FFT + FIR на ядре CORTEX M4

komah ответил TAutomatic тема в Алгоритмы ЦОС (DSP)

Если фильтр реализован правильно, то новых спектральных составляющих он добавлять не должен. Думаю, дело не в нем. Код на Си, можно просто просто проверить на ПК, с модельным сигналом. Самый главный вопрос - соотношение между частотой сигнала и частотой дискретизации. Ну и посмотреть, нет ли ограничения при оцифровке - амплитуда слишком большая, опорное напряжение неправильное... -

FFT + FIR на ядре CORTEX M4

komah ответил TAutomatic тема в Алгоритмы ЦОС (DSP)

Это модуляция или все-таки сумма двух сигналов, один из которых с очень низкой частотой? Если частота сигнала Fs на входе АЦП превышает Fd/2, цифровой фильтр уже не поможет. Если сигнал узкополосный (чистый синус), то его можно и с меньшей, чем Fs*2 частотой оцифровывать (вторая зона Найквиста и т.д.). Но если частота сигнала близка к Fd, то разностная частота попадет в первую зону и соответственно в спектр. КИХ фильтр это ФНЧ? Вот он эту частоту и приподнял. -

Вытащить биты из фазового демодулятора

komah ответил repstosw тема в Алгоритмы ЦОС (DSP)

Там уже и деления никакого нет. Информация об амплитуде отсутствует, делить на 1 не имеет смысла. Фазовый сдвиг за счет разности времени прохождения сигнала на частоте манипуляции явно меньше погрешности взятия отсчетов в получившейся схеме. Можно сразу битовые потоки суммировать. Главное, в нечетном количестве. -

Вытащить биты из фазового демодулятора

komah ответил repstosw тема в Алгоритмы ЦОС (DSP)

Так-то не должны быть больше. Главное, чтобы динамического диапазона хватало. А это про мягкие решения для многоуровневой PAM. Весь диапазон выходных напряжений синхронизатора нужно разделить на области, соответствующие принятым символам. И нормировать значение относительно размера этих областей. Но если символ соответствует двум и более битам, а декодеру нужно мягкое решение для каждого бита, придется подумать. -

Вытащить биты из фазового демодулятора

komah ответил repstosw тема в Алгоритмы ЦОС (DSP)

Это про нормировку: Мягкие решения для (G)FSK2 - это амплитуда на выходе синхронизатора. Если нужны целочисленные - умножьте на максимальное значение и округлите. -

Вытащить биты из фазового демодулятора

komah ответил repstosw тема в Алгоритмы ЦОС (DSP)

1. Амплитуду входного сигнала для синхронизатора к 1 подтяните. Я писал, как правильно нормировать. 2. Попробуйте оценить, сколько в среднем отсчетов на бит приходится. Может, там не целое число. Просто поделите число полученных отсчетов на число бит в пакете. 3. В настройках синхронизатора loop bandwidth я бы для начала в 0,0001 поставил. -

Вытащить биты из фазового демодулятора

komah ответил repstosw тема в Алгоритмы ЦОС (DSP)

Сомнительная информация. GNU Radio генерит скрипт на питоне на основе блок-схемы. Но сами библиотеки в основном на с++. Код открыт и естественно его можно использовать. Но это не самый простой вариант, особенно для переноса на слабое железо. Зачастую выгоднее просто разобраться с алгоритмом (посмотрев его в том же GNU Radio) и реализовать уже на основе своих базовых элементов. Насчет фильтров - в Матлабе есть инструмент для их расчета. Можно им пользоваться, если характеристика фильтра предполагается неизменной. Просто скопировать оттуда коэффициенты в код на Си. Не знаю, какого качества там HDL, думаю примерно как Cи. То есть, посмотреть и забыть. Хотя, понемногу система совершенствуется, в языке уже вполне себе типизация данных появилась. -

Вытащить биты из фазового демодулятора

komah ответил repstosw тема в Алгоритмы ЦОС (DSP)

Выше petrov уже в основном ответил, добавлю от себя Я разделил схему на два интерполятора. Задача первого - из имеющихся, например, 12,5 отсчета на символ, получить целое число, например, 4. Без привязки к моменту тактирования. Второй интерполятор уже должен вычислить значение между отсчетами в оптимальный момент. Мне так удобнее, но в общем это не лучший вариант и я даже знаю, почему. До первого интерполятора. Если у него на входе 1,2 отсчета на символ, делать из них 10 не имеет смысла. С мгновенной частотой. Еще точнее, с сигналом PAM с выхода частотного дискриминатора. Там еще несколько статей в продолжение - конкретные варианты TED рассматриваются. С двумя - это алгоритм на основе максимума правдоподобия. Теоретически, наверное, оптимальный. Для определенных условий. В статье нарисована глазковая диаграмма. Наша задача - взять отсчет в точке максимального раскрытия этого глаза. И это не зависит от вида модуляции. Не применяя схем по стабилизации тактовой, мы к концу пакета (а может и раньше) уползем на границу между символами. Если при оптимальной синхронизации и почти без шумов в вашем сумматоре накапливается значение около 12, то сместившись на 6 отсчетов мы рискуем получить 0. Как насчет помех? Кстати, декодируя на глаз, тактовую тоже приходится восстанавливать. И у вас это делается - по переходам через 0. out = (1.0-alpha)*out + alpha*current_sample; alpha обычно 0,0001..0,001 Ну, коэффициент децимаиции 8,3 : 1. Я хотел обратить внимание, что синхронизатор может выдавать отсчеты асинхронно, главное, чтобы количество было правильным. Визуальные перепады, как и пик импульса, не всегда легко найти алгоритмически. К глазам нейронка более мощная подключена. Лучше какой-нибудь готовой библиотекой пользоваться. Например, liquid-dsp. -

Вытащить биты из фазового демодулятора

komah ответил repstosw тема в Алгоритмы ЦОС (DSP)

Вот хорошее начало: https://wirelesspi.com/phase-locked-loop-pll-for-symbol-timing-recovery/ Без восстановления тактовой все остальное не имеет смысла. А в учебниках про это пишут мало и неправильно. А можно записать сигнал передатчика свистком (RTL-SDR) и демодулировать полностью. И сравнивать не только программные реализации, но и условно железную (в трансивере). -

Вытащить биты из фазового демодулятора

komah ответил repstosw тема в Алгоритмы ЦОС (DSP)

Здесь вместо согласованного фильтра интегратор со сбросом (счетчик). Можно обойтись одним сумматором и вычитать отсчет, задержанный на длительность символа, если знак совпадает. Тогда переполнения не будет. Решение принимается по переходу через 0, для 4FSK работать не будет. И даже сам переход по моему не очень правильно ищется. Лучше не по одному отсчету смотреть, а по выходу интегратора. Ну и подстройки тактовой здесь нет. -

Вытащить биты из фазового демодулятора

komah ответил repstosw тема в Алгоритмы ЦОС (DSP)

Напомнило одно открытие, сделанное много лет назад ). Если постоянно суммировать отсчеты (в виде +1 и -1) и вычитать отсчет, задержанный на длительность символа, можно наблюдать интересную картину. -

Вытащить биты из фазового демодулятора

komah ответил repstosw тема в Алгоритмы ЦОС (DSP)

1. Согласованный фильтр. Импульсная характеристика должна соответствовать ИХ фильтра на передаче. Есть вероятность, что он уже присутствует до вычисления фазы. Можно проверить - на передачу выбрать режим FSK, а на приеме сначала FSK, потом GFSK. Если результаты разные, фильтр уже есть. 2. Ресемплер (интерполятор) - на каждый символ должно приходиться целое число отсчетов, например 2. 3. Выбрать метод оценивания ошибки синхронизации. Выбор зависит от числа отсчетов на символ и формы символа (ИХ фильтра). Если предполагается передача настроечной последовательности в каждом пакете, то выбор богаче, но я с такими вариантами дела не имел. Из NDA самые популярные алгоритмы - Early-Late и Гарднер. Если использовать решения о принятых символах (обратную связь) - Zero-Crossing. 4. В синхронизаторе присутствует интерполятор (например, на основе pfb), который должен выдавать значение в зависимости от полученной оценки ошибки синхронизации (в пределах интервала времени между отсчетами). 5. Если ИХ фильтра и число отсчетов на символ на входе синхронизатора всегда одни и те же (для любой скорости), п. 1, 2 и 4 можно объединить. 6. Оценка ошибки фильтруется простейшим БИХ - фильтром. Коэффициенты определяют скорость подстройки синхронизатора. 7. Если накопленная ошибка превышает интервал времени между отсчетами, следующий отсчет пропускается. 8. В схеме с pfb можно реализовать оценку ошибки синхронизации на основе максимального правдоподобия. Для этого делается два банка фильтров - с ИХ==ИХ согласованного фильтра (mf) и с ИХ== производной ИХ согласованного фильтра (dmf). Оценка ошибки рассчитывается как произведение выходов mf и dmf. 9. В итоге, при исходных 8,3 отсчета на символ, синхронизатор будет выдавать 10 выходных отсчетов на 83 входных. То есть, на каждый входной отсчет, будет получаться от 0 до N выходных. N зависит от реализации. Выше некоторых звезд ) Наверное, стоит говорить о потенциале реализации демодулятора, который обеспечит вероятность ошибки на бит не хуже, чем встроенный. В большинстве случаев мягкое решение - это просто квантованное значение амплитуды на выходе демодулятора. Дальше можно уже всякие правдоподобия считать и их отношения. Просто для выхода демодулятора в виде PAM с несколькими уровнями, нужно для каждого бита значения как-то нормировать. -

Вытащить биты из фазового демодулятора

komah ответил repstosw тема в Алгоритмы ЦОС (DSP)

Действительно весело. Это на длительности символа (бита) мгновенная частота к нулю 6 раз возвращается? Там, похоже, частота записи в регистр жестко связана с тактовой. То есть, число отсчетов на символ примерно одинаковое для любой скорости передачи. Хотя если отсчеты фазы на нижнем графике в той же временной шкале, то просто мгновенная частота неправильно считается. -

Вытащить биты из фазового демодулятора

komah ответил repstosw тема в Алгоритмы ЦОС (DSP)

Амплитудно-модулированная. Такая АЧХ у приемника получилась, НЧ ослабляются больше. А ровнее нижний график наверное потому, что A и B в знаменателе формулы для вычисления производной найдены через sin и cos. И одновременно нулю никогда не равны.