dips11

Новичок-

Постов

23 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о dips11

-

Звание

Участник

Посетители профиля

Блок последних пользователей отключён и не показывается другим пользователям.

-

Да, действительно проблема была в printf(), которая затесалась в одном из файлов. Правда я пока не пойму, как она влияла на симуляцию. Спасибо за помощь.

-

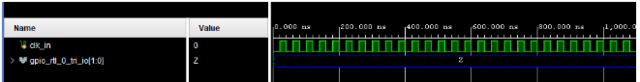

Не помогло. И вроде файл .mem откуда берутся данные для симуляции нормально записывается. Но в логическом анализаторе ILA, после прошивки ПЛИС я вижу данные(1-ое фото), а в vivado при нажатии behavioral simulation нет(2-ое фото).

-

Симуляция Microblaze в Vivado

dips11 опубликовал тема в Среды разработки - обсуждаем САПРы

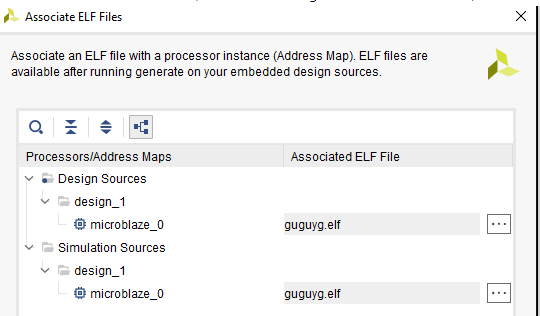

Доброго времени суток. Хочу промоделировать Microblaze в Vivado, с прошивкой написанной в Vitis. Я создал проект в Vivado, экспортировал файл .xsa в Vitis, там получил .elf файл. Его я экспортировал в Vivado, с помощью вкладки tool -> associate ELF Files, как на 1-ом фото. Запускаю симуляцию и получаю дефолтные значения на выходах GPIO в z-состоянии, как на втором фото, как будто Vivado не видит прошивки .elf . Надо сказать, в реальной ПЛИС, на выходах GPIO я получал нормальные выходные данные. Что я делаю не так? -

HART FSK протокол

dips11 опубликовал тема в Алгоритмы ЦОС (DSP)

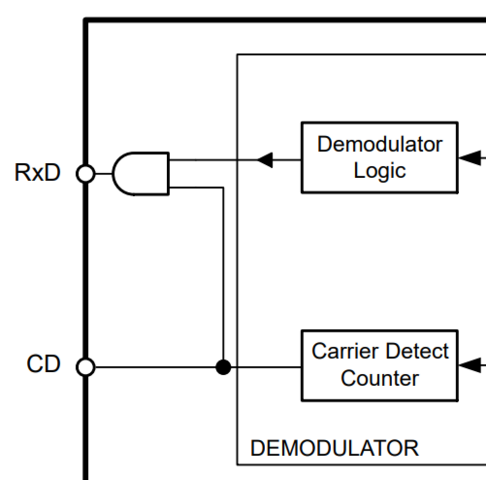

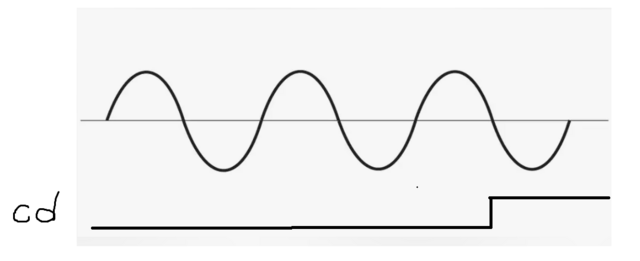

Добрый день. В спецификации протокола HART говорится, что перед отправкой сообщения необходимо передать как минимум 5 преамбул вида "ff" для обнаружения несущей (carrier) и синхронизации приемника сигнала. И вот тут мне непонятен момент.. В приемнике есть демодулятор, фрагмент которого изображен на фото. На его выходе вывод RxD, который по "и" умножает сигнал carrier detect (CD) и демодулированный сигнал (11 бит в UART формате). Но сигнал CD появляется где-то посередине первой посылки, как на втором фото. То есть как я понимаю, как минимум первая посылка из преамбулы будет некорректна выведена на RxD (вместо 11 бит выведено 6 например) ? Наверное для этого и нужна преамбула, но ведь какое то устройство будет снимать сигнал с Rxd в формате UART посылки со (стартовым и стоповым битом), и уже в первой же посылки будет ошибка (например старт бит не на своем месте), и как следствие остальные посылки, тоже не будут корректно приняты. Или в преамбуле это не важно, и ее никто не собирается принимать? Спасибо. -

Спасибо всем за ответы, по ним я понял, надо искать более рациональный метод, в том числе из предложенных выше, чем костыль в шапке темы.

-

Ну наверное, задержка в 1 период частоты допустима, я пока расплывчато представляю все детали

-

Можно, пожалуйста, разъяснить, что значит помехи симметричны? Симметричны относительно чего?

-

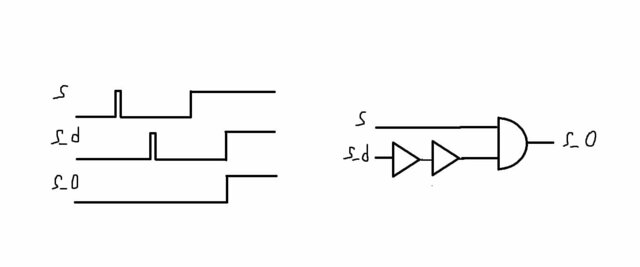

Про длительность не скажу, однако я подумал в любом случае, если способ рабочий он уменьшит вероятность помехи, если скажем она будет до 5 нс. при периоде частоты 100 нс. (10MHz) Надо было уточнить в вопросе, что мне надо получить сигнал на первом фронте при его появлении. То есть я не могу к слову поставить синхронизатор из двух триггеров, ибо они создадут задержку на два периода частоты.

-

Обработка помех на пути сигнала

dips11 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Доброго времени суток. Не знаю, по адресу ли пишу.. Ну в общем, возникла задача обрабатывать сигнал на котором есть вероятность возникновений кратковременных всплесков. Какого-то решения в интернете не нашел, что-то пытался сделать сам, но сомневаюсь в адекватности решения. Ничего лучше не придумал, чем пропустить сигнал и его задержанный вариант через элемент "И". На фото S - искомый сигнал, S_d - он же задержанный, S_o - выходной сигнал. То есть если произойдёт помеха на линии, то на выходе элемента "И" она не должна появиться. Выход измениться, только если время сигнала в высоком состояние будет больше чем время задержки сигнала S_d относительно S. Это допустимый вариант? Или я могу в корне ошибаться? Симуляция вроде бы показала такое же поведение, как и теория. Спасибо. -

Спасибо за ответ, из за ваш код в прошлом ответе

- 10 ответов

-

- verilog

- clock gating

-

(и ещё 2 )

C тегом:

-

Извините, я вас не совсем понял. Вы хотите сказать, что по рисунку в паспорте там будет возможность синхронизовать асинхронный сигнал CS, который может прийти в любое время между 2 и 10 спадом?

- 10 ответов

-

- verilog

- clock gating

-

(и ещё 2 )

C тегом:

-

Забыл в сообщение сверху вас процитировать

- 10 ответов

-

- verilog

- clock gating

-

(и ещё 2 )

C тегом:

-

Вот например микросхема АЦП с SPI интерфейсом, где сигнал CS управляет режимами питания. И как раз цитата для режима отключения микросхемы https://www.farnell.com/datasheets/1814854.pdf - здесь на 17 странице. То есть если сигнал CS поднимется после 2 и до 10 SCLK микросхема отключиться. По поводу синхронизации, у меня есть сомнения, что там будет минимум два такта для пары триггеров после того, как придет сигнал управления режимами CS. Ведь например для режима включения микросхемы на 18 странице говориться что не обязательно нужен полный цикл SPI из 16 тактов. Поэтому предполагал, что для входа в режим отключения питания можно подать два SCLK и поднять CS. И предполагал, там есть другое схемотехническое решение кроме синхронизации.

- 10 ответов

-

- verilog

- clock gating

-

(и ещё 2 )

C тегом:

-

Обработка асинхронного сигнала

dips11 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

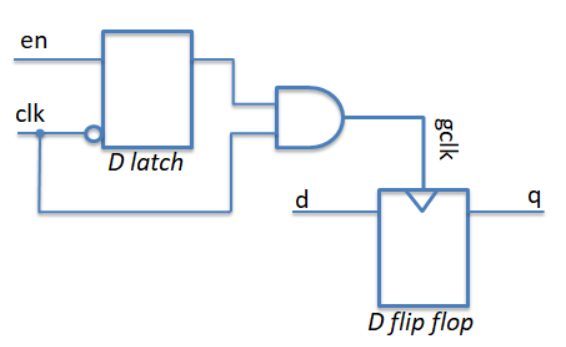

Доброго времени суток. В даташитах на микросхемы иногда встречается момент, где говорится примерно следующее: если сигнал ST придёт до 5 сигнала CLK, то микросхема перейдёт в такое-то состояние, а если после 5 и до 10 CLK то в такое-то. Причём не сказано за какое минимальное время до 5 CLK должен прийти сигнал ST. То есть сигнал полностью асинхронный. И мне интересно как может происходить обработка этого сигнала в микросхеме, ведь так как сигнал асинхронный нельзя просто использовать условие: always@(posedge CLK ) if(cnt==4 && !ST) reg0<=1; И возможности синхронизировать его нет. По сути задача может звучать как "надо определить какой сигнал приходит раньше ST или 5 CLK". Вот основные варианты, которые удалось найти. 1) Использовать сигнал ST как асинхронный сброс триггера. Если сигнал ST придет раньше то он сбросит триггер и не даст ему установиться, но как не достаток решения, если сначала придет 5 CLK то триггер установиться в 1, но потом все равно сброситься по сигналу ST и не сохранит свое состояние. always@(posedge CLK or posedge ST) if(ST) reg0<=0; else if(cnt==4) reg0<=1; 2) Использовать clock gating, то есть по сигналу ST отключить тактовую частоту. Если сигнал ST придет раньше 5 CLK то он заблокирует тактовую частоту для триггера, и он не установиться в 1, если позже пропустит. Где то встречал, что такое решение может вызвать метастабильное состояние. Это правда? Просто я вижу здесь либо наличие сигнала clk_gate для триггера либо его отсутствие. Элемент "И" ведь не должен выдавать шумов. assign clk_gate = CLK & !ST; always@(posedge clk_gate ) if(cnt==4) reg0<=1; Еще встречается реализация с защелкой. И говориться,что защелка добавляется для устранения glitch, так как такая схема будет пропускать сигнал ST только при низком значении CLK и его изменение не вызовет переключение выхода "И". Другие варианты являются производными от этих. Я был бы благодарен за советы, по тому как возможно правильно решить такую задачу. Возможно я вообще не там ищу. Спасибо.- 10 ответов

-

- verilog

- clock gating

-

(и ещё 2 )

C тегом: