nden

-

Постов

26 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные nden

-

-

4 hours ago, UART said:

почему так дешево за 12 бит?

Что за странный вопрос!?

-

Продам 12-битный осциллограф Rigol DHO804

Новый, в запечатанной заводской упаковке.

4 канала

Цена 36500Так как осциллографы DHO804, DHO814, DHO914, DHO924 имеют идентичное "железо", в том числе и АЦП, это позволяет программным способом превратить DHO804 в модель DHO924, за исключением 16-канального логического анализатора и генератора сигналов произвольной формы.

Программно разблокируется до полосы пропускания в 250 МГц.

Из функций открывается:

Максимальная память 50М точек

Декодирование протоколов CAN, LIN

Коэффициент развертки 2 нс/дел по горизонтали, 200 мкВ/дел по вертикали.С возникшими вопросами и уточнениями писать в личные сообщения

-

-

Устройство продано.

В августе месяце освободится на продажу еще пару штук таких же ускорителей. Если кто-то заинтересован, обращайтесь в личные сообщения -

-

Опубликовано · Изменено пользователем nden · Пожаловаться

10 hours ago, Flood said:При этом корпус B2104 вместо D2104 говорит о происхождении из Китая, но вот вендора не узнаю

Ревизия корпуса микросхемы ни о чем подобном не может говорить. Для примера, в фирменной отладке зайлинкса VCU118 применяется первая ревизия корпуса FLGA2104

10 hours ago, Flood said:Судя по количеству фаз питания - для майнинга

У отладки VCU128 чип по логическим ресурсам ровно на 1/4 меньше (3 SLR кристалла 8х6 размерностью, вместо 4 SLR в XCVU13P), и при этом 5 фаз питания VCCINT. Прошли те времена, когда крупные камни можно было питать одной-парой фаз импульсного стабилизатора напряжения

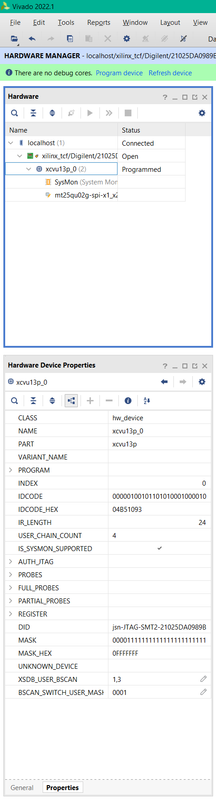

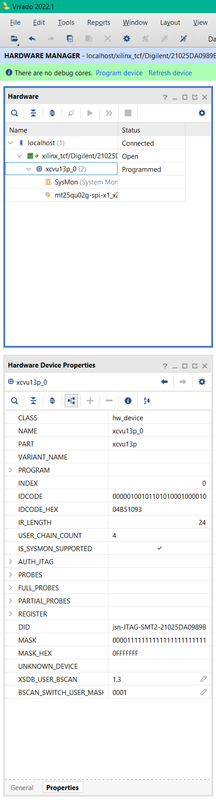

6 hours ago, RobFPGA said:если конечно железка живая и FPGA фюзами не залочена под вендора

Продается как рабочее устройство, а не "кот в мешке". Само-собой не залочен eFuse

Устройство под брендом Алибабы, если это так важно для кого-то -

10 hours ago, RobFPGA said:

Может и нет.

Схожесть есть, но это другое устройство.

-

1 hour ago, RobFPGA said:

Судя по всему китайска FPGA NSA-X1 от Hengyang Data

нет.

-

Ценник более чем хорош, согласен. Для понимания, схожее по компоновке устройство от BittWare на таком же чипе на вторичном рынке в Штатах стартует от $2500+

Есть .XDC на все интерфейсы, подключенные к микросхеме ПЛИС. В таком случае для чего вам нужна схема?

Speed grade -2LE

BMC-контроллер выполняет только роль мониторинга основных напряжений, токовой нагрузки и температуры мсх. -

31 minutes ago, Flood said:

Есть схема? BMC описан?

Что со стоимостью устройства?

Приветствую.

Полной электрической принципиальной схемы всего устройства нет.

Есть pinout/xdc на DDR, QSPI-флеш, PCIE-16x, QSFP, генератор тактовых сигналов, набортных светодиодов. На BMC есть описание регистров.

90 т.р. -

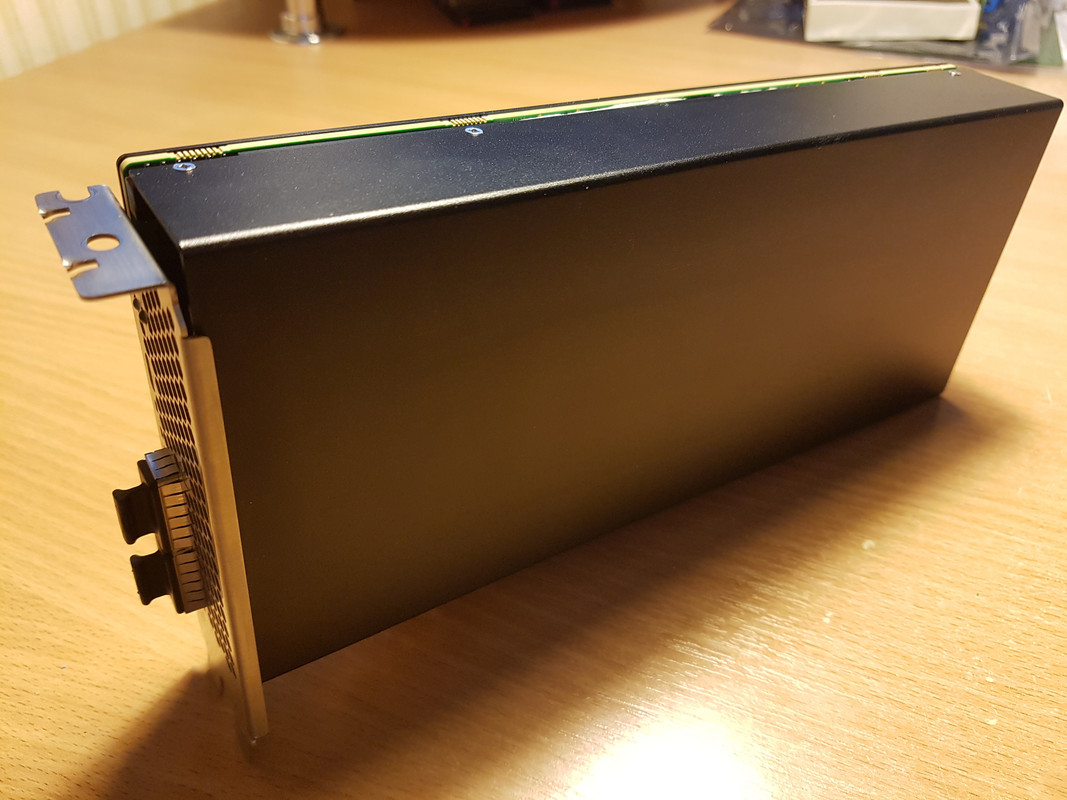

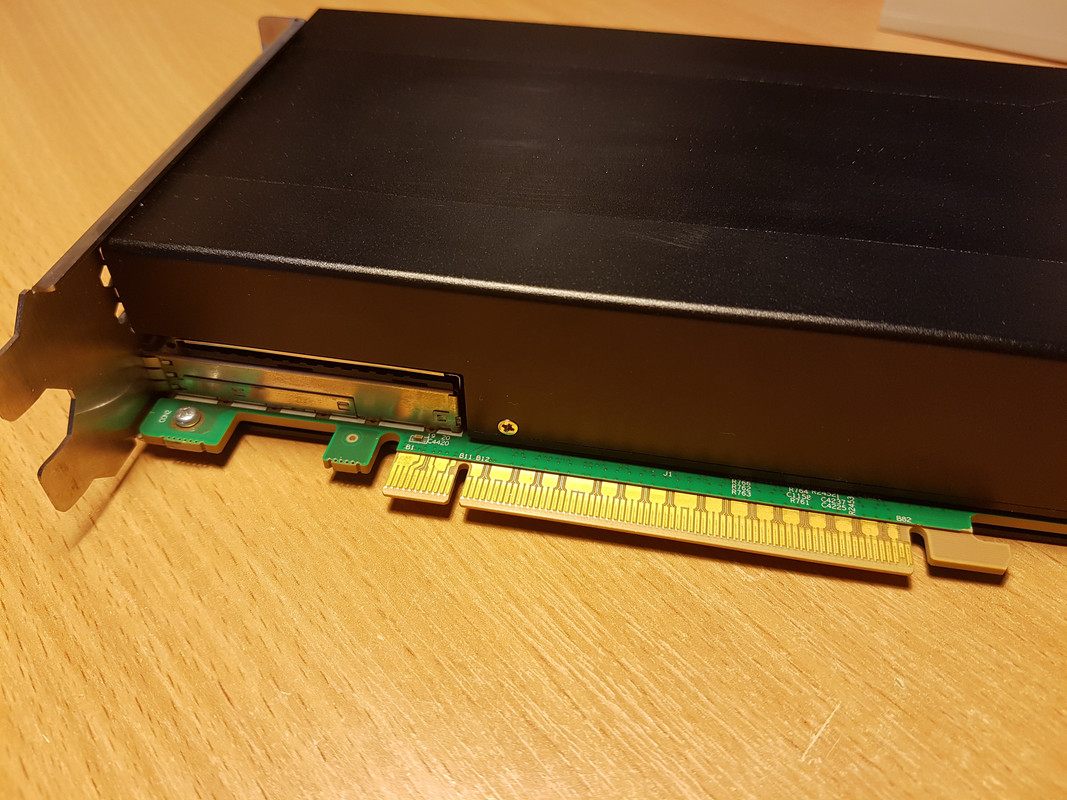

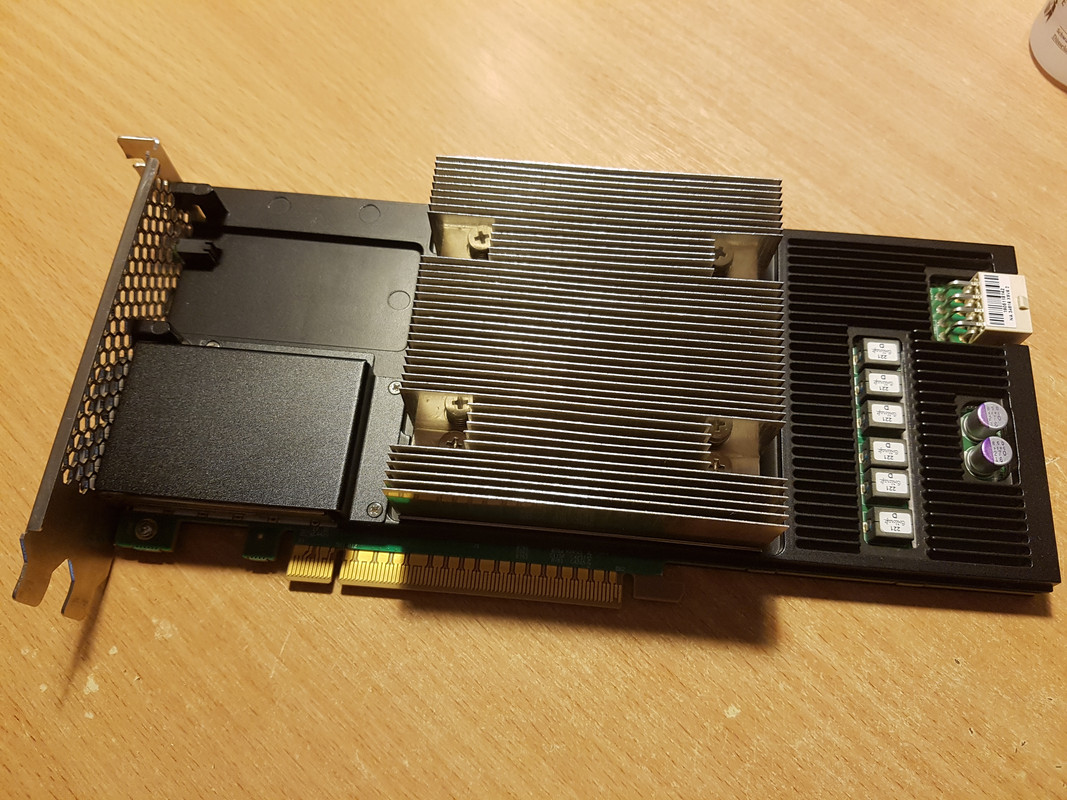

Реконфигурируемый ускоритель в форм-факторе платы PCIe с сетевым интерфейсом 2х100G QSFP28+ на базе FPGA микросхемы Xilinx XCVU13P серии UltraScale+.

Массив конфигурируемой логики состоит из 1,728 млн ячеек LUT;

3,456 млн flip-flop триггеров;

12288 DSP-блоков;

360Mb UltraRAM;

76 GTY-трансиверов 32.75Gb/s.На плате распаяно 16 Гбайт памяти DDR4, она поделена на четыре массива по 4 ГБайт (каждый имеет ширину шины 64-bit + 8-bit ECC).

Также на плате присутствует конфигурационная QSPI-флеш объемом 256 МБайт и CPLD выступающая в роли BMC-контроллера.

Многоканальный тактовый генератор с заведенными на микросхему ПЛИС шестью тактирующими сигналами.Ускоритель выполнен в виде полноразмерной двухслотовой карты расширения с основным интерфейсом PCIe 3.0 x16 (может работать в режиме PCIe 4.0 x8), двумя портами QSFP28+ 100G (обратная поддержка 2*40G/8*25G) и выделенным портом JTAG.

Питание через слот PCIe + 8pin EPS.

6-фазная подсистема питания, 240А номинальный выходной ток.Пассивная система охлаждения, предназначенная для применения в серверных стойках.

Может применяться в паре с турбиной, в таком случае устройство может также располагаться в корпусе рабочей станции/ПК.На устройство предоставлю всю необходимую документацию (pinout, файлы проектных ограничений .XDC и тд).

С возникшими вопросами писать в личные сообщения

Фото устройства -

Опубликовано · Изменено пользователем nden · Пожаловаться

On 11/6/2020 at 7:23 AM, Александр Мылов said:Все-таки хотелось бы узнать, удалось ли достичь таких результатов ТС?

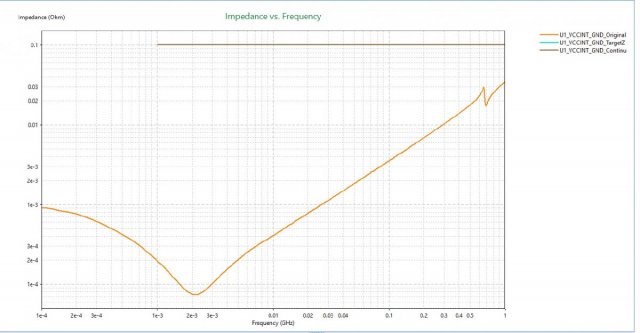

Два варианта набора развязывающих конденсаторов.

При необходимости, лучшего результата для конкретного варианта стека МПП, кол-ва выводов питание/земля у целевой микросхемы будет довольно проблематично достичь

-

5 hours ago, PorychikKize said:

А не сориентируете на конкретный чип? (такие схемы питания пока не делал, но хочу посмотреть на них)

ISL68137, ISL681X7, ISL681X4

3 hours ago, Flood said:В контексте предыдущего обсуждения, скорее всего речь про ISL68127. На мой взгляд - экзотика, вдохновленная примером VCU128

В пользу выбора ШИМ от Intersil/Renesas повлияли несколько факторов, основные из них - наличие открытой документации, доступноость у постащика, положительный опыт применения коллегами в других устройствах.

ПС: это ровно такая же "экзотика", как и "цифровые" ШИМ последних линеек от TI, Infineon - функционал можно сказать идентичный, с небольшими нюансами. Полную документацию что на шим-контроллеры, что на силовые транзисторные ключи последних моделей Инфинеон предоставляет только при подписании соглашения о неразглашении.

-

22 hours ago, EvilWrecker said:

X2Y/3-х выводные они вообще говоря для "более высоких" частот, и соответственно обычные банки(единицы и более мкФ) они не заменяют, а дополняют.

Это понятно, как раз и смотрю на 3-выводные кондеры как на дополнение к bulk алиминий-полимерным, керамике 0805, 0603, с собственным резонансом на значительно более низких частотах; на замену россыпи большого кол-ва 0402

22 hours ago, EvilWrecker said:В тоже самое время имеет смысл прорабатывать разводку обычных 0402, 0805 и пр. Пример просто нормального фанаута, без чудес и пр.

Однако, правильно скомбинировав например тот же LLL153 + X2Y то выйдет декап настолько ок, и притом с таким малым числом конденсаторов что не получится его побить даже если ставить все как у вас на каждый пин. Но я на самом деле не уверен, что именно в вашем случае потребуется такая комбинация, скорее всего будет достаточно просто LLL153, а несколько футпринтов под X2Y можно заложить для успокоения

Спасибо за рекомендации, приму к сведению.

По стеку есть возможность поднять пары питание/земля ядра на один слой ближе к потребителю.9 hours ago, peshkoff said:Мой вопрос в следующем: какой источник питания используется и как измеряете напряжение на ядре? вписываетесь в необходимые 3%?

Источник питания - силовые транзисторные ключи и "цифровой" ШИМ-контроллер от Renesas/Intersil с обратной связью/remote sense, снимающей показания выходного напоряжения, например, с контактных площадок под BGA (смотря куда завести дифф. пару обратной связи).

Возможно Вы неправильно поняли, я уточню - устрояство в "в железе" не произведено, собрано. Находится на этапе оптимизации развязки по питанию.

Как указывал в первом сообщении, анализ плотности токов и падения напряжения провели, небольшие правки понадоблось внести. В целевые 3% укладываемся. Это без учета возможности снятия ШИМ-контроллером показаний выходного напряжения непосредственно на выводах микросхемы-потребителя, или рядом, если расположить равноудаленно от двух микросхем с общей цепью питания от одного регулятора напряжения.

9 hours ago, moon333 said:Но это тоже решается, берут обратную связь прям с нагрузки. А ещё лучше, чтобы усилитель обратной связи был с диф. входом, тогда получится скомпенсировать падение напряжение как на + так и на -(в DC/DC эта функция называется Remote Sense)

Наш случай.

47 minutes ago, Soldier said:Надо понимать физику процесса, а для этого лучше всего читаем до дыр Джонсона-Грэхема, да Эрика Богатина.

Здесь бываем: https://www.signalintegrityjournal.com/

Есть куча webinars того Богатина и сама его книга.

Я всего-лишь придирчивый, нудный "заказчик", однако за за наводку на ресурс и литературу Вам спасибо.

-

2 hours ago, EvilWrecker said:

парт от TDK не интересней(и не при прочих равных), а просто другой

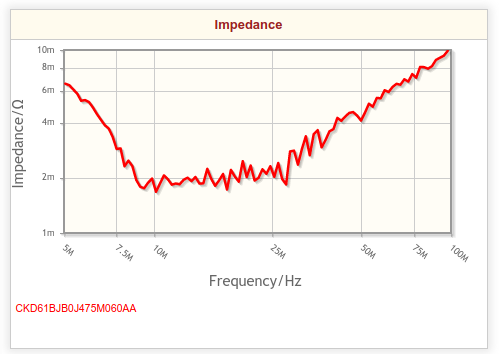

ну почему же не интересней? более низкие значения импеданса на более широком частотном диапазоне. Сравните лоб в лоб графики обоих кондеров.

А вообще было бы интересно не только мне прочитать более развернутое ваше мнение насчет сравнения в качестве развязки по питанию данных двух типов конденсаторов.

2 hours ago, EvilWrecker said:Так для этого платы никакие не нужны

Интерес был глянуть что из себя представляет конкретная отоладочная плата в плане частотной зависимости импеданса цепи питания ядра. Тем более, как писал ранее, опыта в вопросе оптимизации импеданса цепей питания не было до этого.

2 hours ago, EvilWrecker said:чрезмерное количество банок с неоптимизированными номиналами

Насчет чрезмерного кол-ва - возмоджно Вы правы. Для оценки был выбран наиболее простой путь - на каждый пин питания по развязывающему кондеру типоразмера 0402.

В плане оптимизации стека и топологии печатной платы есть несколько мыслей/вариантов, влияние которых на импеданс цепи питания будет оценено в ближейшее время. Увеличить распределенную емкость объемного резонатора (слой питания+диэлектрик+слой земли), снизить индуктивность переходных отверстий, по возможности расположить пары слоев питание и земля поближе к микросхеме-потребителю.

2 hours ago, PorychikKize said:Стесняюсь спросить, а какими средствами шло моделирование? Встроенными средствами Cadence SPB Allegro and OrCAD 17.4? Cadence Design System Sigrity v19?

И можно ли то же самое сделать в Mentor HyperLynx?

Сигрити 19, пакет OptimizePI.

Да, насколько я знаю, Гиперлинкс позволяет выполнять анализ целостности питания, целостности сигналов. Оптимизацию по постоянной составляющей (падения напряжения, плотности токов), и частотной (импеданс цепей питания)

-

On 8/13/2020 at 12:03 PM, peshkoff said:

позвольте задать глупый вопрос. напряжение щупаете на дальнем конце? что за источник питания?

Может вы далеко копнули в исследованиях и надо бы схему изучить?

Частотную зависимость импеданса цепей питания Сигрити изображает на графике так, как это выглядит со стороны БГА-шаров микросхемы-потребителя.

Да какие тут исследования? :) Не понял вашу мысль насчет изучения схемы, будьте добры уточните.

On 8/13/2020 at 4:18 PM, _4afc_ said:Может лучше было поставить 0204-X6S-4v-1uF LLL153C80G105ME21D

Спасибо за преджложение, на данном этапе хотелось бы обойтись без экзотики. А если уж применять экзотику, тогда, при прочих равных, можно подобрать поинтересней варианты. Например такой - трехвыводной чип-конденсатор от TDK CKD61BJB0J475

On 8/13/2020 at 5:18 PM, EvilWrecker said:

On 8/13/2020 at 5:18 PM, EvilWrecker said:Так в этом ничего удивительного нет- просто подобрать конденсаторы еще далеко недостаточно.

On 8/13/2020 at 5:18 PM, EvilWrecker said:Именно в случае плис ориентироваться нужно на то, насколько вся ее внутрянка задействована- в числах это от 50%, а при использовании на полную от 80%

Понимание этих нансов имеется ;)

On 8/13/2020 at 5:18 PM, EvilWrecker said:Если что-то полезное хотите найти в отладках хилых, то только время потеряете

Цель была посмотреть на частотную зависимость импеданса цепей питания в подобного рода "жирных" платах с прожорливыми потребителями-ПЛИС на борту.

-

Да, вендора микросхемы Вы верно определили.

11 hours ago, EvilWrecker said:Нехитрым движением нагугливается документ, в котором содержится фраза отметающая напрочь все сенсации:

ug583 от Зайлинкса, конечно же, бегло был прочитан в свое время. Но, как говорится: "повторение - мать учения". Спасибо, что напомнили :)

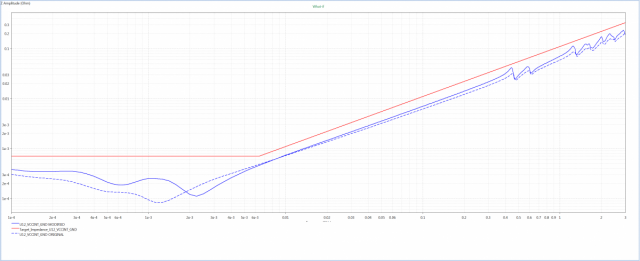

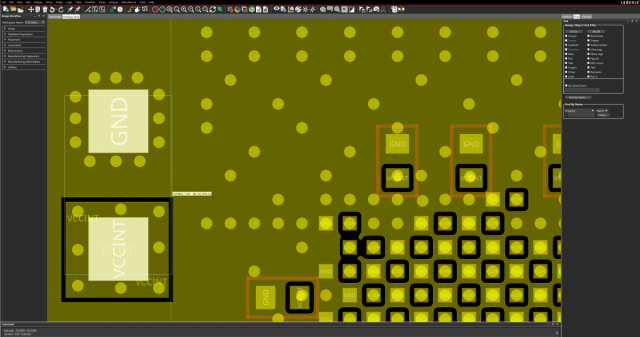

Предлагаемый в данном документе вариант матрицы развывающих конденсаторов не смог обеспечить целевое значение импеданса цепи питания ядра (VCCINT) до частоты 1МГц.11 hours ago, EvilWrecker said:- поставили бга, со всеми фанаутами(даже NC), подключили полигоны питания

- по несложной формуле/в лоб/на авось пробуете ставить разные банки с разными фанаутом

- поставив банки и подключив, засовываете в симулятор и смотрите от кого толк есть, а от кого нету, какой фанаут хорош а какой нет, и самое главное до какой частоты все эти игры имеют смыслПо такому методу и действуем на данном этапе.

11 hours ago, EvilWrecker said:Остальное, а точнее самое главное берет на себе decoupling в корпусе бга(банки/плейны)- т.к. loop/mounted/mutual inductance не забороть на целевой плате для BGA2000+ 1mm pitch никоим образом абсолютно никаким конденсаторами.

До начала анализа целостности цепи питания этот нюанс впринципе был понятен. И то, что выше частот ~100МГц обеспечить "низкое" значение импеданса силами керамических конденсаторов, расположенных только на печатной плате, впринципе не возможно из-за паразитных ствойств - монтажная индуктивность. И импеданс на частотах выше ~100МГц формируется в первую очередь набором развязывающих/блокировочных конденсаторов на подложке самой микросхемы

11 hours ago, EvilWrecker said:Выглядит запредельно избыточным- а сколько слоев в плате и на каких сидит питание 80А с ближайшим землями?

8. PWR - 4, 5; GND - 3, 6

11 hours ago, EvilWrecker said:Разводку таких банок можете показать?

Пример "голой" ПЛИС с подключенными только выводами питания ядра и землей, без подключенных I/O выводов под трансиверы и прочие прелести

11 hours ago, EvilWrecker said:Как посчитали Ztarget, а точнее transient current?

Зайлинкс в том же UG583 рекомендует ориентироваться на значение в 25% от тока потребления ядра. Интел в документации на PDN Tool 2.0 для Stratix 10 ведет речь про 30-50%

0.85v* 0.025(допуск по пульсациям из документации зайлинкса 3% - 0.5% точность установки выходного напряжения модулем VRM) / 80A * (0.25-0.45)

Токи потребления ядра из XPE (Xilinx Power Estimator)

12 hours ago, EvilWrecker said:А зачем столько фаз на жалкие 80А? Или у вас обе микрульки запитываются от одного VRM?

Да, обе ПЛИС питаются одним 7-фазным регулятором напряжения. Целевой ориентир по КПД подсистемы питания ~90%. При необходимости, ШИМ-контроллер позволяет отключать и подключать налету фазы питания, взависимости от нагрузки и заданных параметров.

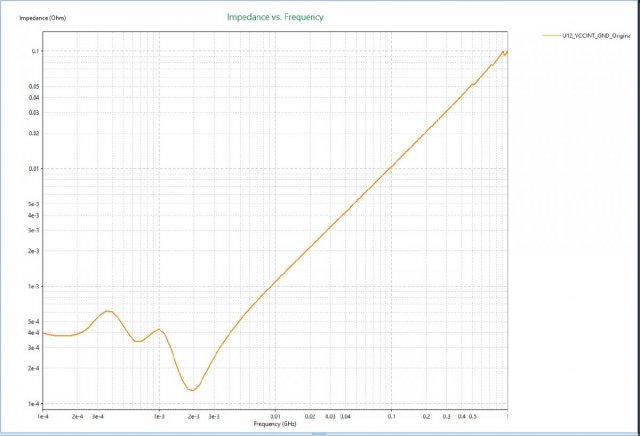

В качестве примера промоделировали цепь питания ядра одной из свежих "топовых" отладочных плат от Xilinx - VCU128 (VIA in pad и прочие прелести).

Получили следующий результат:

-

3 hours ago, EvilWrecker said:

Ну не знаю- тот же ADS втягивает brd без проблем(плата притом может быть в любом состоянии), можно и в ANSYS(посложнее)- на SIGRITY свет клином не сошелся. В тоже самое время, говоря про потребление 80А(VCC_CORE видимо) следует подразумевать импеданс PDN заметно ниже 0.1 Ом (важный порог) в целевом диапазоне частоты(гораздо более узком и низкочастотном нежели "все говорят" в роликах)- здесь больше половины успеха это pre-layout подбор банок и тщательнейший дизайн фанаутов/подключения этих банок к полигонам(не говоря о правильном дизайне этих полигонов). Говоря иначе, если провален этот этап и просто "насыплено 2 мешка 0.1мкФ 0402 с подключением через одиночные виа по длинной стороне тонкими трасками" то на уже разведенной плате в иных случаях можно и не пытаться даже подбирать/анализировать- все без толку. Не приведи случай если есть номиналы менее и сильно менее 0.1мкФ

А что за камень кстати? Банки стоят на противоположной стороне от бга, или на той же? Питание на чем сделано?Конечно, свет клином на Кейденс не сошелся. Важнее результат, а не примененный инструмент/САПР.

Тот же SIwave от ANSYS даже напрямую без конвертации в ODB++ работает с *.BRD файлами.

Если вкратце, то целевое значение импеданса цепи питания ядра - 0.6-1 мОм. Только на PWR выделенно два слоя с полной заливкой, 70мкм, и два земляных слоя.

В качестве развязки по питанию - размещение керамики 0402, 4.7мФ непосредственно на переходные отвертстия идущее на контактные площадки под все BGA шары питания (около 70шт). Плюс расположение в непосредственной близости от микросхемы около десятка 0603 0805 значительно бОльших номиналов, и нескольких алюминий-полимерных 470мФ (с низким ЭПС 4.5 мОм) - все это на данном этапе позволо добиться следующего результата

Из графика видно, что значение импеданса цепи питания до 1мОм удердживается до частоты около 10МГц.

По причине отсутствия опыта выполнения анализа по частотной составляющей, и оптимизации импеданса цепей питания с большими токами, пока остаются неясными седующие моменты - до какой частоты удерживать целевое значение импеданса цепи питания, каким должен быть угол наклона кривой импеданса.

Частота работы целевой микросхемы до ~900МГц

Питание на 7-фазном ШИМ-контроллере + 60А силовые транзисторные ключи

-

EvilWrecker,

Мы же должны понимать, что цель подобного рода семинаров не обучить всем нюансам, а прорекламировать свои услуги. Но здесь палка о двух концах - сразу поонятен "уровень" специалистов.

Ответ на Ваш вопрос почему Сигрити - устройство разработано в пакете Аллегро, так же был опыт выполнения анализа по постоянной составляющей (плотности токов, падения напряжения) в Sigrity PowerDC

Александр Мылов,

Данные приведены верно.

-

Здравствуйте.

Прошу помощи или ищу проектировщика с опытом работы в САПР Cadence Sigirty для выполнения оптимизации топологии цепей питания по частотной составляющей (импеданс сети распределения электропитания) в разработанном устройстве.

Имеется спроектированное устроство с двумя основными потребителями на печатной плате, по 80А на микросхему.

Своими силами выполнена оптимизация топологии печатной платы на основе анализа токовых нагрузок (плотности токов и падения напряжения) в пакете Sigrity.

На данный момент стоит задача по оптимизации цепей питания (до целевого значения импеданса) с выявлением резонансных частот, путем подбора матрицы блокировочных/фильтрующих конденсаторов, их расположения, номиналов и количества.

-

Доброго времени суток.

Есть ли на этом форуме проектировщики с опытом работы в Sigrity, которые могли бы на платной основе проконсультировать относительно проведения анализа целостности сети распределения электропитания по частотной составляющей уже имеющегося дизайна устройства? -

3 hours ago, Aldec said:

Схемные узлы разводятся в ПЛИС или нужны еще дополнительные?

Плату можно развести с разными полигонами, слоями на каждый интерфейс.В первом сообщении указал, что все подробности можно получить через личные сообщения, так же привел электронную почту для связи

1 hour ago, mcheb said:4х слойная печатная плата + PCAD 2002 решают эту задачу на 5+ за неделю без всяких Cadence Sigrity, Mentor HyperLynx, AltiumDesigner PDN Analyzer и т.п. заумностей

Более того скажу, на этот проект выделена 6-слойная ПП

-

On 10/7/2019 at 11:37 AM, Aldec said:

Потребуется не только плата, схема но прошивка плис.

?

Ищется инженер-проектировщик с опытом разработки устройств на базе микросхем ПЛИС/FPGA для проектирования устройства по ТЗ.

Желателено наличие навыков выполнения анализа целостности питания - определение чрезмерного падения напряжения и высокой плотности тока в узких местах полигонов (Cadence Sigrity, Mentor HyperLynx, AltiumDesigner PDN Analyzer).

-

06.10.2019 в 00:13, Aner сказал:Личка у вас пока не работает, тк первое сообшение. Оставьте ваш мейл.

Здравствуйте, списались с вами через личные сообщения.

06.10.2019 в 08:38, sergey.ka сказал:Хоть бы обратный адрес оставили.

Здравствуйте. Первичная связь через личные сообщения.

Новый 12-битный осциллограф Rigol DHO804

в Продам

Опубликовано · Пожаловаться

Всем спасибо.

Приборы проданы