Trumr

Участник-

Постов

12 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйПосетители профиля

Блок последних пользователей отключён и не показывается другим пользователям.

-

ПЛИС PangoMicro

Trumr ответил Gas Wilson тема в Работаем с ПЛИС, области применения, выбор

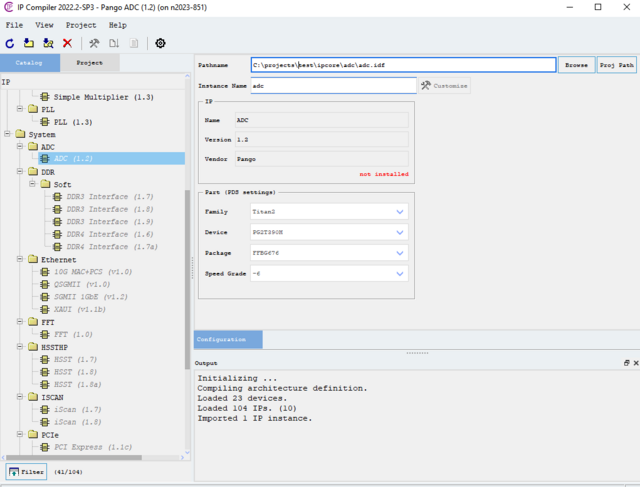

Спасибо, с ADC разобрался. Однако всё ещё непонятна ситуация с другими IP. Наверное можно делать по аналогии и будет всё работать, но хочется разораться что это - просто заглушка или с этим можно как-то работать? -

ПЛИС PangoMicro

Trumr ответил Gas Wilson тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте, подскажите пожалуйста, где брать IP для PDS? Например ADC и FFT точно поддерживаются выбранным чипом, но написано "not installed". Логично предположить, что их нужно откуда-то скачать и установить 🙂 можете поделиться у кого они есть? -

Защита данных FPGA

Trumr ответил prom тема в Работаем с ПЛИС, области применения, выбор

Не нашёл в теме про шифрование прошивки в 7 серии xilinx. Пишут, что прошивка шифруется, а при программировании на лету дешифруется уже внутри ПЛИС (ug470 стр. 96), а ключ для дешифровки зашивается один раз и навсегда. Это разве не решает вопрос защиты от копирования? И может кто знает, есть ли что-то подобное у Альтеры? -

Подскажите где искать

Trumr ответил Trumr тема в Микросхемы

Спасибо, похоже это именно то, что нужно. -

Подскажите где искать

Trumr опубликовал тема в Микросхемы

Стоит задача разработки медиаконвертера из меди в оптику, проблема в том, что необходимо использовать только отечественные элементы, но китайские тоже можно. Наверняка есть какие-то китайские аналоги микросхем физики ethernet, но вот где искать не знаю... -

Отлаживал на большом циклоне, но количество занятого места не больше 10% от ёмкости чипа - явно надо брать что-то поменьше. У MAX V есть постоянная память же. Объём памяти, частоты ещё можно сравнивать более-менее напрямую. Мне вот интересно как оценить (пускай грубо) сколько проект будет занимать на плис другого производителя. Вот например 600 ALM это на циклоне, а вот сколько это будет в CLB у ксайлинкса? Вот в описаниях чипов есть параметр как логические ячейки, по ним можно напрямую сравнивать?

-

Ёмкость ПЛИС у разных производителей

Trumr опубликовал тема в Работаем с ПЛИС, области применения, выбор

Есть небольшой проект. Для отладки я делал на макетной плате с циклоном 5 (DE0-Nano-SoC). Но так как проект маленький - занимает ~500-600 ALM, выбираю микросхему помельче. И тут думаю взять CPLD. Но не знаю max5 от альтеры или CoolRunner-II. Вопрос в том, что я знаю сколько проект занимает в ALM, но как перевести это в блоки от xilinx'a? Как вообще сравнивать по ёмкости чипы разных производителей? -

FPGA Lattice

Trumr ответил Trumr тема в Работаем с ПЛИС, области применения, выбор

Я это увидел. Кстати, памяти там как раз больше. Я думал что разницу в 60$ можно увидеть не углубляясь в тонкости архитектуры и не сравнивая под микроскопом доп блоки. -

FPGA Lattice

Trumr ответил Trumr тема в Работаем с ПЛИС, области применения, выбор

Да, есть бесплатная версия, но там ограничения. Для коммерческой разработки надо покупать лицензию. Но это частности, мне интересны именно отличия в чипах - при производстве приборов хотя бы от 50 штук, выгода выходит уже 50*60$ = 3000$, что для небольшой компании уже неплохо. Но я начинающий разработчик и многих нюансов не знаю. Вот я увидел 2 чипа - разница в цене 60$ и сразу подумал, что они по характеристикам они должны отличаться, но отличий не увидел (даже дешёвый чуть получше будет). Значит я что-то не понимаю. Но раз это просто следствие различного подхода к производству, то значит это просто нехватка опыта и всё придёт со временем. Про плис от Lattice и microsemi я узнал буквально вчера. -

FPGA Lattice

Trumr ответил Trumr тема в Работаем с ПЛИС, области применения, выбор

Ну там и софт платный. -

FPGA Lattice

Trumr ответил Trumr тема в Работаем с ПЛИС, области применения, выбор

Настолько всё плохо? У Lattice, вроде, для разных семейств разные среды разработки, и везде всё плохо? Документацию посмотрел, она очень хорошая - всё подробно и понятно расписано. А Lattice чуть больше 10$. Циклон ~70$. Откуда такой большой разброс цен? Это просто такая ценовая политика компаний или это чем-то обосновано? -

FPGA Lattice

Trumr опубликовал тема в Работаем с ПЛИС, области применения, выбор

Увидел две похожих ПЛИС 1. https://www.digikey.com/product-detail/en/lattice-semiconductor-corporation/LFE5U-25F-6BG256I/220-2206-ND/9553919 2. https://www.digikey.com/product-detail/en/intel/EP4CE22F17I7/EP4CE22F17I7-ND/2288336 Вроде по характеристикам не особо отличаются, но вот цена очень сильно. Как такая плис может стоить ~10$? И вообще кто-нибудь работал с чипами от Lattice? Какие есть у них нюансы? Вроде они сильно дешевле чем Xilinx и Altera, но по характеристикам норм.