flammmable

Свой-

Постов

298 -

Зарегистрирован

-

Посещение

Весь контент flammmable

-

Эта логическая схема показывает главное: условный контакт на процессоре SA_DQ[0] соединён с двумя контактами в двух разных разъёмах DIMM, причём в одном из разъёмов может отсутствовать планка памяти и контакт в нём будет торчать из дорожки, по сути, в воздух на несколько миллиметров. При этом, система в целом будет работать. Это важное уточнение :) Серьёзно? То есть двухканальный контроллер памяти, поддерживающий четыре модуля DIMM - малоосмысленен, но от чего-то такую конфигурацию пихают почти в каждый процессор и почти в каждую материнскую плату, например, в вышеупомянутую GIGABYTE B550 (можно пройти по ссылке и убедиться)?

-

Ладно, по поводу PCIe я ляпнул не подумав. Но вот в даташите на Core-i7 распиновка (стр.85): 64 штуки SA_DQx и 64 штуки SB_DQx. А вот в том же даташите блоксхема (стр.10) про два канала памяти и два модуля на каждый из каналов. Абсолютно очевидно, что для планок DDR нет никакого point2point. Как вы это объясните? :)

-

Насколько критичны стабы в переходных отверстиях?

flammmable опубликовал тема в В помощь начинающему

Часто, когда речь заходит про целостность сигналов, находится мудрец с седой бородой и усами Фу Ман Чу, который обязательно расскажет про высверливание стабов в переходных отверстиях. При этом он будет рассыпать терминами LPDDR4, PCI-Egen4, потери -20дБм, четверть-волновой шлейф, в предельном случае ещё может вытащить на свет диаграмму Смитта. Но у меня возникает вопрос: вот, к примеру, материнская плата GIGABYTE B550 с четырьмя запараллелеными слотами PCI-Egen4 и четырьмя запараллелеными слотами DIMM под DDR4. В каждом незанятом слоте по несколько десятков контактов, длинной миллиметров по 5 каждый, которые торчат вверх и терминированы... воздухом. И ничего - всё работает. Понятно, что если постараться, можно и хрен сломать, и наделать переходных отверстий со стабами через каждый сантиметр полуметровой шины, ведущей к DDR4 - и ничего не будет работать. Но если не возводить тупость в абсолют. К примеру, на каждой дорожке всего по три переходных отверстия - под процессором, под памятью и ещё одно где-нибудь в середине. В таком случае, по вашему опыту, насколько критичны стабы в переходных отверстиях? -

Почему ADS SI/PI не подтягивает топологию?

flammmable опубликовал тема в В помощь начинающему

Тренируюсь симулировать в ADS. Взял простой тестовый проект - двухслойка с логическим элементом. Я создал в ADS воркспейс. Создал в нём стек из двух слоёв. Импортировал два гербера и отверстия, раскидав их по трём слоям. Набросал пинов, указал землёй опорные полигоны. Жму кнопку SI/PI, появляется диалог "из чего создать SI/PI" с вариантами стека и топологии. Т.к. их по одной штуке в воркспейсе - вариантов ровно по одной штуке. Жму ок - открывается пустой просмотровщик. Что я делаю не так? -

Чем просимулировать HSPICE?

flammmable опубликовал тема в В помощь начинающему

Хочу потренироваться симулировать выходы интеловской ПЛИС. У неё есть IBIS и HSPICE. С IBIS всё хорошо симулируется в MicroCap-12. Вопрос про HSPICE. Я так понимаю у Analog Devices немного свой формат SPICE и свой Ltspice, у Texsas Instruments - также свой SPICE и своя TINA-TI. И HSPICE напрямую не поддерживается ни тем, ни этим симулятором. Чем бесплатным просимулировать HSPICE? -

AT91RM9200 и Keil

flammmable ответил flammmable тема в Microchip (Atmel)

Накатив MDK79525.EXE вот отсюда, данное ядро появилось )) Но чувствую, что у меня будут еще вопросы ))) -

AT91RM9200 и Keil

flammmable опубликовал тема в Microchip (Atmel)

На сайте Keil есть упоминание о микроконтроллере AT91RM9200. Однако при создании нового проекта в свежескачанном Keil в списке микроконтроллеров AT91RM9200 отсутствует. Как при помощи Кейла помигать на данном микроконтроллере лампочками? -

Хотелось бы подвигать фронты на 0,5-1,0нс. Не разберусь, как это синтаксически записать в *.sdc .

-

Вот он, эталонный ответ по существу! )))))

-

И тем не менее, это возможно?

-

Допустим имеется: 1) тактовый вход clk_ext на который поступает 100МГц 2) регистр test_sequence, который проинициализирован некоторым значением 3) и два выхода hs1 и hs2, которые выдают значение из test_sequence[0] Допустим также, что на каждый щелчок clk_ext регистр test_sequence сдвигается на один бит налево с переносом старшего бита в младший (циклический сдвиг). Как задать в *.sdc констрейны, чтобы сигнал с выхода hs1 был смещен на заданное небольшое значение относительно сигнала hs2?

-

Аналог разъема Samtec

flammmable опубликовал тема в Компоненты

Есть ли у каких-нибудь TEconn, Molex и т.д. аналог пружинного разъема FSI от Samtec для соединения одной платы с контактными площадками другой платы? Т.е. разъем, не требующий отдельной ответной части. -

Как согласовать линию?

flammmable ответил flammmable тема в В помощь начинающему

Как раз этим и занят. Смотрите, с одиночной линией стало понятно. Но как быть с древовидной трассировкой (T-routing), скажем, в случае линий DQ микросхем DDR? Линия с одним импедансом разделяется на две с точно такими же импедансами. Да, в DDR есть встроенные терминаторы. Но от активной микросхемы отражение же будет? Оно вернется к точке разветвления и отразится от него обратно, в сторону активной микросхемы. Причем точку ветвления не удастся поставить в упор к процессору/ПЛИСу. Второй вопрос в том, что если бы процессор/ПЛИС обладал выходным импедансом Z/2, то можно было бы проложить линию с таким же импедансом до точки ветвления, а дальше развести линии с импедансом Z. И сигнал от процессора/ПЛИС не отражался бы от точки ветвления и пришел бы на память с полной амплитудой. Но в обратную сторону - от памяти к процессору/ПЛИС - отражение будет как ни старайся. С этим придется жить? -

Как согласовать линию?

flammmable ответил flammmable тема в В помощь начинающему

Ага! Теперь яснее. Спасибо! Я спросил на electronics.stackexchange, там, по моему мнению ответили более ёмко по форме (и то же самое - по сути). -

Как согласовать линию?

flammmable ответил flammmable тема в В помощь начинающему

Предположим, у нас переход 100-омной линии в 50-омную. Сама 50-омная линия на другом конце терминирована на землю резистором 50 Ом. Со стороны 100-омной линии на переход набегает импульс. Импульс по ряду причин (нет сознания, к примеру) не знает длину 50-омного отрезка и тупо разделяется на прошедший и отраженный. Прошедший доходит до терминирующего резистора, рассеивается на нем и исчезает. Вы хотите сказать, что длительность отраженного импульса как-то коррелирует с длиной 50-омного участка? Если да, то за счет чего? -

Как согласовать линию?

flammmable опубликовал тема в В помощь начинающему

Предположим, я хочу передать сигнал по коаксиальному кабелю на высокоомную нагрузку. Сам сигнал - прямоугольный импульс ТТЛ 3,3 вольта (несимметричный) с вывода ПЛИС в корпусе LQFP-144. Кабель - 50-омный тонкий коаксиал вроде RG-174. Разъемы на плату - SMA/SMB или что-нибудь похожее. Нагрузка - высокоимпедансный вход другой микросхемы (ПЛИС/МК), либо вход осциллографа, выставленный в 1МОм. Предположим, из IBIS-а на ПЛИС стало ясно, что выходы у него имеют импеданс ниже 50 Ом. Следовательно, в теории, можно согласовать линию последовательным резистором на стороне источника сигнала. Но! При соединении двух линий передач с разными волновыми сопротивлениями, будет происходить отражение от точки их соединения. Это отражение будет зависеть только от разности волновых сопротивлений и НЕ будет зависеть от длины каждого участка. Если бы к 50-омной линии подходила бы дорожка меньшего импеданса (скажем 20 Ом), то можно было бы согласовать линии при помощи последовательного резистора (30 Ом). Однако, как показывает Saturn PCB, даже при толщине FR4 в 0,2мм, линия в 50 Ом достигается при ширине в 0,35мм. При толщине FR4 в 0,5мм импеданс линии в 50 Ом достигается при ширине аж 0,922мм! Т.е. при шаге LQFP-144 в 0,5мм любая дорожка на плате, отходящая от микросхемы будет иметь импеданс заведомо выше 50 Ом. Получается, что импульс, выпущенный ПЛИСом в сторону осциллографа 1МОм отразится от него, побежит обратно, а затем, несмотря на все согласования на стороне источника, отразится от мм... контактной площадки на плате или перехода "дорожка-разъем". 1) Всё ли так, как я описал? 2) Если да, то возможно ли согласовать такую линию на стороне источника? 3) Если нет, то где справедливость? -

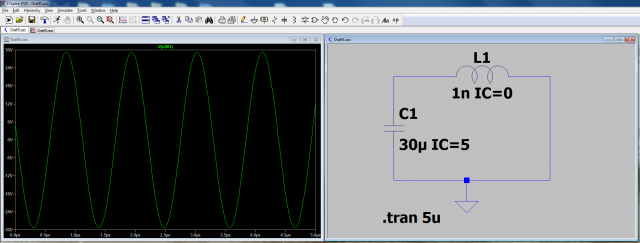

Схему, в точности по условию ТС (я - ТС) продемонстрировали cybersonner, Plain и Leka на первой странице обсуждения. Ну и еще вы на третей. Для LTspice важно отметить, что у индуктивности по умолчанию ненулевое последовательное сопротивление. Для незатухающих колебаний его нужно установить в ноль (ну и другие сопротивления можно обнулить на всякий случай).

-

Большое спасибо cybersonner, Plain, Leka!! Это да ) MicroСap тоже заработал - стоило вставить в цепь один ключ и прописать ему замыкание через 100нс. Как обычно, порадовал комментарий от человека (ничего личного, такой человек обязательно оказывается в обсуждении), прочитавшего вопрос через слово по диагонали и выплалившего первое, что пришло на ум.

-

Схема чего? Колебательного контура? Конденсатор соединен обоими концами с индуктивностью. Всё. Один из двух проводников между конденсатором и индуктивностью имеет ответвление, соединяющее его с землёй, чтобы симуляторы не ругались на отсутствие земли. Ответ написан в четвертом предложении исходного вопроса - в момент времени t=0 ток через индуктивность равен нулю, а напряжение на конденсаторе равно 5 вольтам. Энергия в контур не подводится.

-

Как просимулировать колебательный контур?

flammmable опубликовал тема в В помощь начинающему

Попытался просимулировать классический колебательный контур в LTSpice и в MicroСap. Накинул на схему конденсатор, индуктивность и землю. Задал значения ёмкости и индуктивности что-то около 100нф и 1нГн. Добавил для конденсатора начальное значение 5В - в обоих симуляторах это делается записью в Value конденсатора строки "100n IC=5". Включил отслеживание напряжения на конденсаторе. Оба симулятора показали синусоиду с амплитудой от 100 вольт и выше. Понятно, что по закону сохранения энергии, на конденсаторе не может оказаться амплитуда выше начальной. Добавил IC=0 (initial condition) для индуктивности - всё тоже самое. Поигрался с ёмкостью и индуктивностью - амплитуда поменялась, но по прежнему была больше чем 5 вольт. Добавил в цепь резистор 0,001ом - колебания стали затухающими, но первые несколько колебаний всё равно сильно выше 5 вольт. Попробовал запускать схему при помощи отдельного источника питания и двух свитчей. Одни - ждет, включается, дает конденсатору зарядиться и выключается. Второй - через некоторое время после зарядки конденсатора и отключения источника, соединяет конденсатор с индуктивностью в контур. В MicroCap - та же фигня, напряжение выше номинального на источнике, в LTSpice не проверял. Два вопроса: 1) Что за чепуха, что симуляторы не симулируют школьную схему? 2) Как их заставить сделать это? -

Ссылки на даташиты приведены в первом посте. Одни даташит на 10 страниц, другой - на 18 страниц. Если найдёте подходящий параметр, я буду благодарен. Но, кажется я понимаю почему просимулировать проще. Я сегодня поигрался с IBIS-ом ISSI-вской памяти и её выходной буфер ведет себя совсем не как идеальный источник напряжения + внутреннее сопротивление. Возник другой вопрос. Похоже, что некий усреднённый импеданс выходных буферов SRAM несколько выше, чем 50 ом. Возможно ли, так скажем, подкрутить размерами дорожки и толщиной платы (дорожки делаем тоньше, экранирующий полигон отодвигаем дальше) волновое сопротивление линии до 100-150 ом, чтобы память работала с наименьшей длительностью фронтов? Вообще, порочна ли практика такой подкрутки?

-

Огромное спасибо! Это именно то, что я хотел узнать!

-

Каков выходной импеданс однопортовых SRAM?

flammmable опубликовал тема в В помощь начинающему

У навороченной SRAM IS61QDPB451236C есть пин ZQ, который управляет выходным импедансом в относительно широких пределах: А что насчет более простых памятей типа IDT71256 и CY7C199? По слову "impedance" в даташитах всего 3-5 совпадений и они идут в паре со словом "high". Каков их выходной импеданс? -

Номиналы резисторов для SRAM

flammmable опубликовал тема в В помощь начинающему

На стр.3 даташита на IDT71256 и на стр.5 на CY7C199 указаны схемы AC test load. Чем определяются магические номиналы резисторов 480/255 ом? Почему именно такие числа? Что это вообще за схема и почему у Cypress есть схема с 50-омной линией, а у IDT (Renesas) - нет? -

Какова амплитуда отраженного импульса?

flammmable опубликовал тема в В помощь начинающему

Предположим, имеется: - Источник сигнала с внутренним сопротивлением 75 Ом, способный выдавать прямоугольные импульсы амплитудой 10 вольт. - Длинная линия без потерь с волновым сопротивлением 50 Ом - Приёмник с сопротивлением 350 Ом. Источник выдает импульс в линию. Пока импульс идет по линии от источника к приёмнику, его амплитуда будет равна 4 вольтам, т.к. внутреннее сопротивление источника и линия в момент начала передачи образуют квази-делитель (50 Ом / (75 Ом + 50 Ом))*10 вольт = 4 вольта. Какова будет амплитуда на приёмнике? И какова будет амплитуда отраженного от приёмника импульса? MicroCap 12 говорит, что на приёмнике будет 7 вольт и, соответственно отразится 3 вольта. Но почему именно 7 и 3 ?