-

Постов

12 216 -

Зарегистрирован

Весь контент ViKo

-

А в течение 6-ти часов? :) И второму автомату задать частоту, например, 333 MHz... И фронты ему завалить конденсатором! :) Хотя... это ж в одной ПЛИС? Тогда... нагрузить выход от второго автомата на кучу триггеров (только это, наверное, не поможет). Придумал - вывести наружу, завалить конденсатором, а потом уже - на вход первого автомата. То-то он "порадуется"!

-

Не обязательно. Например, можно описать сдвиговый регистр следующим образом: always @ posedge CLK begin d = c; c = b; b = a; a = IN; end И скомпилируется абсолютно в то же, что и при неблокирующих присваиваниях. Только думать над кодом придется дольше. И смысла - никакого. А в остальном - полностью поддерживаю.

-

Не стоит смешивать в одном блоке блокирующие и неблокирующие присваивания, особенно, если в них участвуют те же переменные. А результат можно использовать где угодно, и как угодно. Если заменить у Вас <= на =, результат будет однозначным, определяемым последовательным выполнением операторов.

-

Скажите, а есть ли способ не подсчитывать вручную количество ячеек в массиве для строки "Hello, world"? А так, чтоб само посчитало и завело массив нужного размера. :)

-

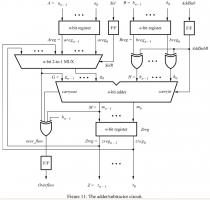

Вот, в качестве примера - схема из Tutorial по Quartus (файл tutorial_quartusii_intro_verilog.pdf, запрятан внутри каталога с установленным Quartus, так, что хрен найдешь...)

-

Автор точнее бы ответил... Часто заказчик сам не знает, что ему надо. На мой взгляд, больше похоже на учебное задание. К примеру, переполнения счетчиков уже не важны? Разрядность сумматора без обратной связи должна быть на 1 больше входных сигналов, а сумматора с обратной связью даже и не знаю, какая... То же касается и следующих за ними цепей.

-

Так ли уж нужно подавать на сумматор с обратной связью выход сумматора без обратной связи, когда компаратор переключит мультиплексор на сумматор без обратной связи (трудно высказать :) ? Все равно выход сумматора с обратной связью наружу не пойдет (по крайней мере, пока компаратор не переключит мультиплексор на него). Здесь получается как-то странновато: на одном конце компаратора - выход сумматора без обратной связи, на другом - тот же сигнал с добавкой от входа... Т.е. если этот входной сигнал не 0, компаратор обязательно переключится на сумматор с обратной связью. Если всего этого не нужно, то можно исключить мультиплексор из обратной связи. Ввести конвейер в схему сравнения. И достичь предельного быстродействия. Например, так: module QuartusAccumulator #(parameter WIDTH = 10) ( input RES_n, input CLK, input [WIDTH-1:0] A, input [WIDTH-1:0] B, input [WIDTH-1:0] C, output reg [WIDTH-1:0] MUX ); reg [WIDTH-1:0] AReg; reg [WIDTH-1:0] BReg; reg [WIDTH-1:0] CReg; reg [WIDTH-1:0] SumSAReg, SumSARegReg; reg [WIDTH-1:0] SumBCReg, SumBCRegReg; reg CmpReg; always @(negedge RES_n, posedge CLK) if (!RES_n) begin AReg = 0; BReg = 0; CReg = 0; SumSAReg = 0; SumSARegReg = 0; SumBCReg = 0; SumBCRegReg = 0; CmpReg = 0; MUX = 0; end else begin AReg <= A; BReg <= B; CReg <= C; SumSAReg <= SumSAReg + AReg; SumSARegReg <= SumSAReg; SumBCReg <= BReg + CReg; SumBCRegReg <= SumBCReg; CmpReg <= SumSAReg > SumBCReg; MUX <= CmpReg? SumSARegReg : SumBCRegReg; end endmodule

-

Согласен. Вроде, пришли к консенсусу. А если принять во внимание еще и схему сравнения... то экспериментировать еще есть над чем. Заглянул в даташит на Cyclone-III, действительно, только 2 режима. А у ACEX было 4. То-то, я смотрю, в мой проект счетчика на Verilog Quartus так и норовит сунуть сумматор.

-

Никто при этом не говорил, что оставлять выходной регистр нельзя. Сумматор работает медленно, мультиплексор свои задержки добавляет. Куда ни ставь регистр, будет задержка: сумматор+мультиплексор(регистр), или мультиплексор+сумматор(регистр), или сумматор+мультиплексор+регистр. В-общем - один регистр куда-то сунуть можно. Но не более. В какой-то схеме быстродействие будет чуть больше, чем в других.

-

В начале разговора речь шла именно о конвейере. И Вы предлагали ввести регистр после сумматора. Получили бы именно то, что я описал. Взгляните внимательнее...

-

Берем упрощенную до предела схему. Сумматор, на один вход приходит входной сигнал In, на другой результат с этого же сумматора. Если бы после сумматора не было регистра, то при подаче на вход чего-нибудь сумматор тут же "насчитался" до насыщения, перевалил через переполнение, в-общем, загенерил на своей максимальной частоте. К счастью, после сумматора стоит регистр Rg1, и сигнал на втором входе сумматора появляется через такт. Подаем на вход последовательность 0, 1, 2, 3, 0, 0, 0... Смотрим, что имеем на выходе (регистра Rg1, хотя можно было бы и на выходе сумматора): In 0 1 2 3 0 ... Sum 0 1 3 6 6 ... Rg1(Out) 0 0 1 3 6 6 ... А теперь вводим еще один регистр после Rg1, и подаем на вход сумматора (и на выход) уже с Rg2. Что имеем для той же входной последовательности: In 0 1 2 3 0 ... Sum 0 1 2 4 2 4 2 Rg1 0 0 1 2 4 2 4 Rg2(Out) 0 0 0 1 2 4 2 4 2 4 2 ... Что это? Загенерил наш сумматор!: 2, 4, 2, 4... Я несколько раз проверил на бумаге. Попробуйте сами на досуге. Может быть, я ошибся... Если все верно, то... сами знаете... Конвейер, братцы, не так прост.

-

Насколько я понял из кода, signal rst_m0 : std_logic; -- асинхронный сброс ... rst <= rst_m0 when rst_mode="00" else ... if( rising_edge( aclk ) ) then ... if( rst='1' ) then stp <= "00" after 1 ns; то внутри сигнал сброса использовался как синхроннный с тактами aclk. Т.е. эксперимент был верный. Только лучше, вместо выявления предельной работоспособности по частоте, определить количество ошибок на максимальной рабочей частоте, для разных схем синхронизации.

-

А вот гляньте на следующий код! Та же программа, что демонстрировал вначале, была слегка модернизирована. Компилятор, правда, 9.70. Но, думаю, дело не в нем, а неком "стечении обстоятельств", позволяющих компилятору решить, что биты выбора страниц "ператрахивать" не надо. Out = 0; Delay10K(Time); // 0.05 .. 0.4 s 036 1105 BCF 0x5, 0x2 037 0825 MOVF 0x25, W 038 23F2 CALL 0x3f2 95: Out = 1; Delay10K(30); // 0.3 s 039 1505 BSF 0x5, 0x2 03A 301E MOVLW 0x1e 03B 23F2 CALL 0x3f2 96: // Out = 0; Delay10K(20); // 0.2 s 97: Out = 0; Delay10K(Time); // 0.05 .. 0.4 s 03C 1105 BCF 0x5, 0x2 03D 0825 MOVF 0x25, W 03E 23F2 CALL 0x3f2 98: Out = 1; Delay10K(30); // 0.3 s 03F 1505 BSF 0x5, 0x2 040 301E MOVLW 0x1e 041 23F2 CALL 0x3f2 99: // Out = 0; Delay10K(20); // 0.2 s 100: Out = 0; Delay10K(Time); // 0.05 .. 0.4 s 042 1105 BCF 0x5, 0x2 043 0825 MOVF 0x25, W 044 23F2 CALL 0x3f2 101: Out = 1; Delay10K(30); // 0.3 s 045 1505 BSF 0x5, 0x2 046 301E MOVLW 0x1e 047 23F2 CALL 0x3f2 В-общем, все не так просто. Найти бы эти "обстоятельства"...

-

Хочу спросить у автора (так как не разбираюсь в VHDL) - у вас внутри первого (проверяемого) автомата сигнал сброса используется как синхронный или асинхронный? Если сброс асинхронный, то в первом случае нет условий для возникновения метастабильного состояния. Если частота сигналов выше предельной, то, может быть, уже нужно говорить, что сигналы просто не успевают переключиться из-за ограниченной скорости нарастания? Наверное, нет смысла использовать микросхему в недопустимом режиме работы, только если для выяснения ее предельных возможностей :)

-

Поиск метастабильности

ViKo ответил dsmv тема в Языки проектирования на ПЛИС (FPGA)

Если вы боретесь с метастабильным состоянием на транзисторном уровне - искренне желаю вам успеха. Верю, что здесь есть над чем поработать. На мой взгляд, больше на уровне технологии производства. Если у устройств, использующих ваши изделия, увеличится MTBF - здорово! Правда, вряд ли я воспользуюсь результатами ваших трудов, по понятным причинам. К счастью, мне нужно бороться на уровне HDL. Надеюсь, читающие эту ветку нашли для себя что-то полезное. -

Поиск метастабильности

ViKo ответил dsmv тема в Языки проектирования на ПЛИС (FPGA)

Когда появится результат ваших исследований, применимый к метастабильному состоянию триггера, дайте мне знать. -

Поиск метастабильности

ViKo ответил dsmv тема в Языки проектирования на ПЛИС (FPGA)

Еще раз, для полного "просветления": Преобразования Лапласа используется для решения линейных дифференциальных уравнений. Линейная система обладает, например, свойством пропорциональности: увеличился сигнал на входе в 2 раза - увеличился в 2 раза выходной сигнал. Как вы понимаете, цифровые устройства принципиально нелинейные, это их основополагающее свойство. Поэтому применять преобразование Лапласа, исследовать нули и полюсы, говорить об устойчивости для цифровых устройств не имеет смысла. Можно, конечно, рассмотреть поведение логического элемента на неком малом участке передаточной функции (не переходной характеристики, как я говорил раньше, извиняюсь). Для регистра на 4-х транзисторах и аналогового мультиплексора, возможно, преобразование Лапласа что-то дает... Но для изучения метастабильности нужно изучать не это. Не то, как "шарик скатывается с горки" под воздействием внешнего импульса, а когда он туда попадает, и когда "скатится". Для этого нужны совсем другие инструменты. А если шагнуть выше, то здесь работает теория вероятности и математическая статистика. Кстати, в логике, например, ACH, на передаточной функции есть гистерезис, около 150 mV, и это, заметьте, не в триггерах Шмитта, а в обычных инверторах. А сама характеристика - резкая, хоть линейку прикладывай. А метастабильные состояния возникают, тем не менее. Я, наверное, сказал уже раз пять одно и то же, только разными словами - дело не в передаточной функции, не в порогах. Нужно рассматривать процесс во времени. Как, я не знаю... -

Поиск метастабильности

ViKo ответил dsmv тема в Языки проектирования на ПЛИС (FPGA)

Верно, это не полюс. Это... нуль! :) (Если модератор уничтожит, я... не хотел... не смог удержаться) Преобразование Лапласа позволяет решать дифференциальные уравнения. Шарик на горке - почему бы нет? Деньги в кошельке - почему бы нет? В конце концов можно добраться до движения электронов, которые тоже описываются какими-то уравнениями. Нужно остановиться на определенном уровне абстракции. Инженеру для понимания метастабильного состояния триггера достаточно знать, что оно было, есть, и будет... есть входные сигналы :) -

Поиск метастабильности

ViKo ответил dsmv тема в Языки проектирования на ПЛИС (FPGA)

Так можно в любом явлении полюс найти. Вот, кончились деньги у меня в кошельке - чем ни полюс? :) -

Поиск метастабильности

ViKo ответил dsmv тема в Языки проектирования на ПЛИС (FPGA)

Чтобы вас переубедить, нужно копнуть слишком глубоко. На это у меня нет ни времени, ни желания. Возможно, найдется другой энтузиаст... Вот статья с сайта Altera. Там про полюса ничего не говорится. http://www.altera.com/literature/wp/wp-010...tastability.pdf -

Поиск метастабильности

ViKo ответил dsmv тема в Языки проектирования на ПЛИС (FPGA)

Метастабильность и стабильность - понятия разные. О стабильности (устойчивости) устройств, с полюсами и т.д. нужно говорить не в этой теме. Уверяю вас, с устойчивостью у триггеров и остальной цифровой техники все в порядке! Метастабильность - именно некое состояние, длящаеся достаточно длительно, а потом прекращающееся. Вы, SM, смешиваете эти понятия. Где-то раньше вы упоминали, что любой триггер в момент переключения находится в метастабильном состоянии - в корне неверно! Прислушайтесь к словам Oldring'а. 2 Oldring Триггеры обычно работают по чему-то одному - фронту или срезу. Чтобы триггер срабатывал по срезу, нужно подать инвертированные такты. Естественно, на порогах срабатывания это никак не скажется. Они - одни и те же. -

Поиск метастабильности

ViKo ответил dsmv тема в Языки проектирования на ПЛИС (FPGA)

Экспонента-то - затухающая, так что со стабильностью схемы все в порядке. Звенеть выход может из-за внешних цепей (емкостей), смещающих эти полюсы. Логичнее было бы назвать не "пороговая" характеристика, а "переходная", от входа к выходу. Причем характеристика не линейная (как в аналоговых усилителях) и не вертикальная прямая (как должно быть в идеале), а нечто S - образное (только монотонное). И беда возникает, когда входной сигнал попадает на середину этой кривой. К счастью, в большинстве случаев входной сигнал не задерживается в этой точке, растет или падает. Обычные логические элементы продолжают переключаться вслед за входным сигналом. Но для триггера - приходится "фиксировать" именно это "неопределенное" состояние. Вот и не знает, "куды ж хрыстьянину податься". -

Поиск метастабильности

ViKo ответил dsmv тема в Языки проектирования на ПЛИС (FPGA)

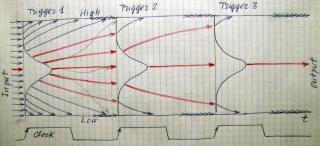

К вопросу о метастабильном состоянии и плотности распределения вероятности его возникновения. Я изобразил картинку, на которой показано прохождение сигналов через цепочку из 3-х триггеров, в несколько гипертрофированном виде. Слева - входной сигнал, распределенный равномерно, справа - он же, выходной. По фронту тактового сигнала первый триггер начинает переключаться в низкое или высокое состояние, в зависимости от уровня входного сигнала. В большинстве случаев это происходит достаточно быстро, и ко второму фронту синхроимпульса первый триггер находится в устойчивом состоянии. Второй и следующие триггеры только подтверждают это состояние. Если бы входной сигнал постоянно переключался из высокого в низкое состояние и обратно, то для сигналов с "логическими" уровнями выход первого триггера переключался бы в полном диапазоне напряжений от низкого до высокого. А так как пороговая область переключения триггера (второго), как и любой другой логики, по входу значительно меньше выходного размаха, этот триггер будет переключаться с еще большим "энтузиазмом". Потому что пороговое состояние сигнал на его входе пробегает быстро. Следующий триггер переключится еще быстрее, и так до своего предельного быстродействия. 25 лет назад это называлось "нормализация фронтов". (На картинке это не показано, просто вспомнилось). Но когда входной сигнал находится в области порога переключения ("горка"), триггер "задумывается" надолго. В идеальных условиях на самой вершине "горки" - навсегда. Вывести его из этого состояния может любой толчок - шум, бросок по питанию... Когда этот толчок произойдет - неизвестно, а до того времени триггер находится в метастабильном состоянии. Очевидно, что если сигнал попал на склон "горки", ему проще выбрать направление переключения. Но и такое переключение затягивается (такие сигналы красненьким показаны). Например, после первого триггера 5 сигналов не достигли логического уровня к моменту прихода второго фронта синхроимпульса. Но для второго триггера уже большая часть сигналов на входе находятся вне пороговой области. Поэтому после второго триггера осталось 3 нелогических сигнала. А после третьего триггера - все, кроме одного, находятся в устойчивом логическом состоянии. Чтобы говорить о вероятности возникновения метастабильного состояния, нужно знать форму этой самой "горки", а также поведение сигнала в зависимости от места, на которое он попал. Очевидно, что эти закономерности нелинейные. В зависимости от количества триггеров, думаю, вероятности метастабильного состояния нужно перемножать. Т.е. условно, для одного триггера 0.01, для двух 0.0001, для трех 0.000001... Зависимость метастабильного состояния от периода синхроимпульсов тоже, естественно, нелинейная. Похожа на спадающую экспоненту. Чем больше период, тем менее вероятно сохранение метастабильного состояния. Это можно увидеть и по списку цифр, с которых вся эта дискуссия началась. А еще я могу сделать вывод, что использование нескольких триггеров дает намного больший эффект для уменьшения метастабильного состояния, чем увеличение периода синхроимпульсов. P.S. После того, как все это написал, понял, что дал маху. "Горка"-то должна быть по времени, в районе фронта синхроимпульса, а не по напряжению! Но, предполагая линейное изменение входного сигнала во времени, "горку" по времени можно превратить в "горку" по напряжению. Не исключаю, что именно пороговая характеристика по напряжению определяет метастабильное состояние триггера. -

Поиск метастабильности

ViKo ответил dsmv тема в Языки проектирования на ПЛИС (FPGA)

Так и я... о методах. Метод уменьшения вероятности появления метастабильных состояний прост - цепочка триггеров. Об этом уже говорилось. Мне кажется, вы что-то упустили в понятии метастабильности. Дело не в порогах, а в вероятности попадания на эти пороги, и времени схода с них. -

Поиск метастабильности

ViKo ответил dsmv тема в Языки проектирования на ПЛИС (FPGA)

Тогда, скажите пожалуйста, о чем здесь идет речь. В двух словах. Если не о метастабильности, я удалюсь.