-

Постов

68 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о aleshanoff

-

Звание

Участник

- День рождения 01.11.1987

Старые поля

-

skype

Array

Контакты

-

ICQ

Array

Информация

-

Город

Array

Посетители профиля

-

VHDL - автомат взбесился!

aleshanoff ответил aleshanoff тема в В помощь начинающему

спасибо за ответ))) извините, что потратил ваше время. Бьюсь головой об стену от стыда)))) -

VHDL - автомат взбесился!

aleshanoff опубликовал тема в В помощь начинающему

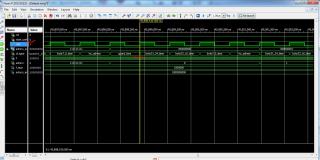

Всем доброго времени суток, товарищи. Творю проектик на VHDL. Написал автомат pr_2 : process (clk1, start_uart, rst ) begin if clk1'event and clk1 ='1' then -- сброс if rst = '1' then st_type <= guard_time; else case st_type is when guard_time => -- режим ожидания if start_uart <= '1' then st_type <= byte31_24_time; else st_type <= guard_time; end if; when byte31_24_time => ------------------------------------------- st_type <= byte23_16_time; ---------------------------------------------- when byte23_16_time => ------------------------------------------- st_type <= byte7_0_time; ---------------------------------------------- when byte7_0_time => ------------------------------------------- st_type <= inc_adress; ---------------------------------------------- when inc_adress => if adress = adress_max-1 then st_type <= guard_time; adress <= 0; else adress <= adress + 1; st_type <=byte31_24_time; end if; when others => st_type <= guard_time; end case; end if; --- конец сброса end if; --- конец клока end process; Переходит из режима ожидания самостоятельно в следующую стадию. Перепробывал все, что знал. (а знаю я немного)) Помогите мне, пожалуйста. Прилагаю скрин ISim'a -

куплю IDT72V261LA10

aleshanoff опубликовал тема в Куплю

Нужно 10 шт микросхем памяти с питанием 3.3 вольта, 9 каналов, глубина 16кб, частота не ниже 50 МГц. Звонить +79203178564 Писать [email protected] -

Местонахождение товара: г. Смоленск Возможна доставка Почтой России (оплата по договоренности) тел. +79203178564 (могу перезвонить) майл. [email protected] цена за 8 упаковок 1200 р. Описание Imagecure® XV501T-4 Screen является двухкомпонентной термоотверждаемой жидкой фотопроявляемой защитной паяльной маской, которая после сушки выпариванием образует пленку, обрабатываемую в водном растворе карбоната калия или натрия, или растворителе. Резист и отвердитель перед использованием должны быть тщательно смешаны: - для зеленого и белого цветов в соотношении 2: 1 вес/вес, - для остальных цветов, в т.ч. красного, синего и черного в соотношении 3: 1 вес/вес. Отвердитель должен добавляться к резисту. Для обеспечения полного смешения компонентов рекомендуется использовать механическое смешивание. Перед использованием Imagecure® обеспечить полную очистку всех медных поверхностей, отсутствие пятен и сушку. Imagecure® серии XV501T-4 может использоваться для любых типов вертикальных и горизонтальных установок сеткографической печати. Очень важна хорошая предварительная сушка покрытия. Экспонирование: Imagecure® XV501T-4 негативные и могут обрабатываться в любых рамах экспонирования при использовании легированных железом ртутных УФ ламп с длиной волны 300 – 400 нм. Появление: Imagecure® XV501T-4 легко проявляется в растворе карбоната калия или натрия. Рекомендуемая концентрация карбоната - 10 ± 2 г/л. Рабочий диапазон рН водного раствора карбоната: 11.3 – 10.8. Для обеспечения качества проявления рекомендуется не понижать pH раствора проявления ниже 10.8. Рекомендуемый диапазон температур 30 - 40ºC, оптимально 35 - 38ºC. УФ облучение: Перед окончательным отверждением может требоваться УФ облучение. Отверждение (окончательная сушка): Рекомендуемый цикл сушки 140 - 150ºC в течение 60 - 90 мин. Оптимально 60 мин при 150ºC. Время сушки следует считать с момента достижения в печи заданной температуры.

-

Как проверить на исправность TXB0108

aleshanoff опубликовал тема в Пайка и монтаж

Здравствуйте, товарищи. Объясните пожалуйста, как можно с помощью мультиметра или осциллографа проверить преобразователь уровня TXB0108 на исправность? -

core generator FFT 7.1 ISE Design Suite 14.7

aleshanoff опубликовал тема в В помощь начинающему

Здравствуйте, уважаемые товарищи. Реализую на ПЛИС БПФ. При создании IP-ядра выдает такие ворнинги. WARNING:sim - VHDL simulation file type 'Behavioral' is not valid for this core. Overriding with simulation file type 'Structural'. А при синтезе схемы No primary, secondary unit in the file "D:/XProject/input_4/ipcore_dir/FFT_512x8.vhd. Ignore this file from project file "D:/XProject/input_4/schema_input_vhdl.prj". Подкажите, пожалуйста, что делать? И происходит такая бодяга только с FFT 7.1 Core. Остальные IP-ядра норм симулируются -

VHDL грамматика

aleshanoff опубликовал тема в В помощь начинающему

Здравствуйте. Подскажите, пожалуйста, есть ли на VHDL автоматические конструкции присвоения значений выводам шины или необходимо прописывать каждый вывод отдельно? Например. Энному выводу присваиваем '0', а остальным '1'. read_fifo(n) <= '0'; read_fifo(not n) <='1'; Или всем выводам присвоить единицы, но ширина шины - это изменяемый параметр. например read_fifo <= "11111111"; Нужно чтобы количество единиц зависело от ширины шины и автоматически изменялось при изменении параметра. -

VHDL борьба с лишним импульсом

aleshanoff ответил aleshanoff тема в В помощь начинающему

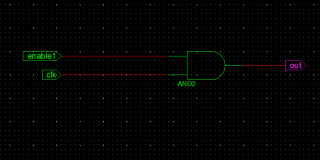

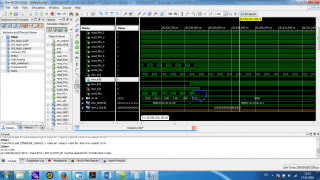

А как тогда правильно сделать сигнал? Мне нужно, чтобы в нужный момент из плис выходила последовательность импульсов на нужной частоте и нужной длительности. (для управления чтением и записью внешнего FIFO, например) и, к тому же, в счетчиках же есть вход разрешения.... При использовании такой конструкции (см рисунок): на выходе при симуляции проскакивали лишние импульсы в момент спада разрешающего сигнала, синхронного с фронтом клока(см первый рисунок в теме). а при моей - нет (см последний рис)! -

Ругается синтезатор ISE 14.7

aleshanoff ответил aleshanoff тема в В помощь начинающему

Итогом всех изысканий стал просто автомат на два состояния. Спасибо, iosifk. library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity vxod_automat_1 is Port ( clk : in STD_LOGIC; hf : in STD_LOGIC; stop : in STD_LOGIC; r : in STD_LOGIC; o : out STD_LOGIC); end vxod_automat_1; architecture Behavioral of vxod_automat_1 is type state_type is (st0, st1); signal state: state_type; begin state_proc: process (clk, r) begin if r='1' then state <= st0; elsif (rising_edge(clk)) then case state is when st0 => if (hf='1' and stop='0')then state <= st1; else state <= st0; end if; when st1 => if (hf='0' and stop='1') then state <= st0; else state <= st1; end if; when others => state <=st0; end case; end if; end process ; out_proc: process (state) begin case state is when st0=> o <= '0'; when st1=> o <= '1'; when others => o<= '0'; end case; end process ; end Behavioral; -

VHDL борьба с лишним импульсом

aleshanoff ответил aleshanoff тема в В помощь начинающему

решилась проблема с помощью этого кода library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity enable is Port ( en : in STD_LOGIC; clk : in STD_LOGIC; o : out STD_LOGIC); end enable; architecture Behavioral of enable is begin process (clk) begin if en='1' then o <= clk; else o<='0'; end if; end process; end Behavioral; -

VHDL борьба с лишним импульсом

aleshanoff ответил aleshanoff тема в В помощь начинающему

Код не писал, моделировал на схемотехническом уровне. Разрешающий сигнал со счетчика идет вместе с клоком на элемент И. После него такая фигня. В конце выходного сигнала проскакивает лишний импульс. -

VHDL борьба с лишним импульсом

aleshanoff ответил aleshanoff тема в В помощь начинающему

Но так и не получил ответа, уважаемые товарищи. Будут ли возникать в железе пики в конце сигналов и, если да, то как их избежать? Сигналы внутренние, синхронизированы. на элемент И подается разрешающий сигнал (xlxn431) и клок. на выходе при синхронизации в конце получаем незапланированный пик. -

VHDL борьба с лишним импульсом

aleshanoff ответил aleshanoff тема в В помощь начинающему

я еще не пробовал просто на нем. А так очень даже нравится))) -

VHDL борьба с лишним импульсом

aleshanoff ответил aleshanoff тема в В помощь начинающему

да