ArtoM23

Участник-

Постов

28 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о ArtoM23

-

Звание

Участник

- День рождения 23.12.1988

Контакты

-

ICQ

Array

Информация

-

Город

Array

Посетители профиля

1 622 просмотра профиля

-

Здравствуйте, коллеги. Ваши комменты почитал, интересен вопрос. У меня в системе АЦП ad9680 4 штуки и плис virtex 7 410t. Подключено 4 линии 10 Гбит. Стадии инициализации проходят, получаю данные из АЦП. Частота тактовая 1000 Мгц, Sysref 50 Мгц. При выборке 512 кб вижу "рваный" в одном месте синус, то есть сигнал теряет 4 отсчета в посылке, при этом счетчики ошибок встроенные в корку плис JESD не обновляются. То есть сигнал получен таким с АЦП, ошибок декодирования не было на линии. Прошу дать совет, что делать? rolleyes.gif

-

Подключаете программатор, открываете импакт. Конфигурацию можно вычитать из flash. Слева кнопка ReadBack

-

Исходя из опыта на плате ставится внешний датчик температуры, который опрашивается по i2c например. ИМХО System monitor лучше использовать только для ПЛИС. :rolleyes: Кстати а интересно, внешнее устройство находится у Вас на плате или это отдельное изделие?

-

Спс за ответ. Нашел готовое решение ise 14.7 Selectio wizard. Ребята из ксалинкса сделали все просто отлично, а главное понятно. Думаю сэкономит мое время, а главное поможет.

-

Связь 4 ПЛИС kintex 7 физ линиями на ПП

ArtoM23 опубликовал тема в Форумы по интерфейсам

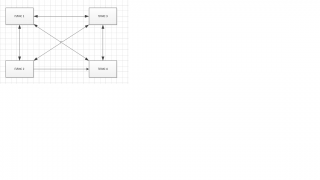

Здравствуйте! Есть плата на которой стоят 4 ПЛИС kintex7 с физическими связями через HP банки 32,33,34 как показано на рисунке ниже. Всего 48 линий. Необходимо передавать минимум 20 битные данные с 800 МГц на линию. То есть 1 связь должна пропускать 24*800 = 19200 Мбит/сек. Мой вариант организовать это с помощью ioserdes. Это логично, что вы думаете? -

CDCE62005 настройка по SPI

ArtoM23 ответил aosp тема в Схемотехника

Спс, разобрался. Надеюсь кто-то сэкономит часы, а в моем случае деньки ) Просто нужно соблюсти последовательность и ничего не забыть. 1) Прогружаем SPI регистры 1-8. 2) Проверяем LOCK. Если LOCK установлен, но на выходе частота не та, что ожидается переходим п.3. или даем команду на перекалибровку в соостветствии с cdce62005.pdf Если LOCK установлен, но на выходе постоянка, то проверьте согласование по входу опоры и обратно в п.1. 3) Даем инструкцию на запись EEPROM. 4) Вкл/выкл микросхему пин -PWDW. После этого проверяем частоту на выходе. По поводу программирования на 10 раз, это я как раз заходил в режим перекалибровки не изменяя при этом других регистров. -

CDCE62005 настройка по SPI

ArtoM23 ответил aosp тема в Схемотехника

Здравствуйте, подскажите мне пжл как вы решили данную проблему. Использую cdce62005.pdf и программу evalcdce62005.exe. Прогружаю 7 регистров без 8го. После ряда циклических прогрузок PLL входит в нужный режим. Как вы решили проблему, есть ли жесткий алгоритм прогрузки? :cranky: HELP, не удается запустить, знающие помогите!!! -

Что касается питания ПЛИС, у нас есть расхождение с рекомендацией. Последовательность активности питаний: VMGTAVTT и VMGTAVCC одновременно, VCCINT, VCCAUX, VCC0. - плисина и сигнальник подключены напрямую или через свич? ПЛИС и DSP подключены напрямую (точка-точка). - клоки рапиды тактируются у них от одного генератора, или от разных? Клоки рапиды и DSP и ПЛИС подключены к разным генераторам, точнее на dsp идет клок рапиды от PLL2 cdce62005 312.5 МГц. На ПЛИС клок рапиды можно завести двумя путями: - напрямую от генератора 125 Мгц - от pll0 cdce62005, пропустив через неё сигнал генератора 125 МГц. Пробовал эти два варианта. - в стандартной корке рапиды от ксайлинкса есть возможность принудительно сбросить линк и порт, вы пробовали так делать? Да, так делать пробовал, результат аналогичен. - посмотрите что в регистрах ошибки SRIO сигнальника прописано когда все плохо. В одном из регистров утановлен бит ошибки на прием данных. error decode 8b/10b. - есть ли уверенность, что программа в сигнальнике стартовала? Механизм конфигурирования DSP после подачи питания еще не отлажен. То есть я в chipscope смотрю, что DSP_RESET_STATISTIC в 1, а затем шью dsp вручную. - соответствует ли стартовая последовательность на 6678 даташиту? Здесь я не совсем понял, что вы имеете ввиду. Стартовая последовательность SRIO? Errata скачал. изучаю. Спасибо за мысли. у нас на плате revision1.) То есть у Вас также не было инициализации между ПЛИС и DSP по рапиде?

-

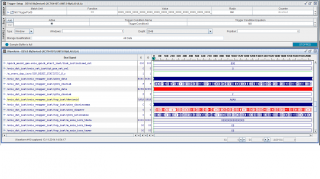

Здравствуйте! Используем самостоятельно изготовленную плату с установленной ПЛИС xc7k410t и DSP tms320c6678. На данном этапе идет отладка взаимодействия ПЛИС и DSP с использованием интерфейса SRIO gen 2 v1.7. Включением питания на плате управляет мк stm8. Сначала контроллер открывает питание на ПЛИС, затем ПЛИС конфигурируется и "дает" мк разрешение на включение питаний dsp. dsp включается в соответствии с документом TMDXEVM6678L_EVM_A102_1.pdf стр 4. Далее мк сообщает ПЛИС о том, что DSP включен и плис прогружает PLL1 и PLL2 необходимые для работы DSP (в своем изделии повторена схема на стр. 7). После чего, ПЛИС ожидает захвата pll1 и pll2, а затем сигналы сбросов dsp подтягиваются к единице в соответствии со схемой на стр.4. Как только DSP сброшен выставляется сигнал DSP_RESET_STATISTIC. Ну и наконец) Проблема в том, что инициализация порта SRIO в режиме 1gb/s 1x проходит от включения к включению платы. То есть, я могу запустить изделие, затем после прогрузки ПЛИС, вкл. DSP, после захвата PLL сконфигурировать DSP и в chipscope увидеть "работающий порт" или увидеть "нечто", что представлена на рисунке ниже. контуры питаний на плате были тщательно проверены, PLL-ки гарантированно всегда в захвате. Как думаете, в каком направлении копать? :cranky: Применительно к DSP хочу отметить, что если инициализация порта прошла успешно после включения, то разные режимы работы 4x 3.125gb/s, 4x 5gb/s, 1x 2gb/s, 1x 5gb/s работают адекватно, порты инициализируются.

-

Добрый день! Интересует как на Вашем предприятии с секретностью и присваивается ли сотрудникам форма допуска?

-

DDR3 MIG virtex6

ArtoM23 ответил bogaev_roman тема в Среды разработки - обсуждаем САПРы

Смотрите первоисточник mig 3.92. Пользовался им и вполне толково написано) Раздел user interface. К тому же используйте ModelSim и вы получите модель которая идет с коркой. Инструкция по запуску модели в том же ug 406. -

Проблема решена. :bb-offtopic: при передаче адреса в эвм необходимо отбрасывать два младших бита.

-

Форумчане, помогите :laughing:. Проблема обрела новую сторону. Изучил pg023. Открыл для себя "чудесный мир" интерфейсов этого ядра. Анализируя статус ошибок в chipscope из "Devise status register" выявил особенность. На шине регистрируется ошибка "fatal error". Согласно pg023 это может быть вызвано несоответствием длины передаваемых данных (полезной нагрузки) на шине pcie и в дескрипторе (заголовке tlp пакета). А также неправильным видом запроса. Подскажите в каком направлении копать? И интересно почему после выявлении ошибки система перестает регистрировать прерывания, а ядро pcie их якобы выдает по команде (msi_sent ='1'). Используемый драйвер, программа тестирования успешно использовался с отладочной платой virtex 6. Но там и ядро было без AXI).

-

Касательно стыковки seriallite/aurora. Модули seriallite в проекте не менялись. Произвел редактирование модулей aurora. Для virtex6 использовалась aurora 6.2. Параметры: - 2гб/сек с опорной частотой 125 МГц. - 1 линия. Параметры Seriallite: - 2гб/сек с опорной частотой 100 МГц. - 1 линия. Фактически были подогнаны параметры физических посылок aurora под интерфейс Seriallite. То есть в соответствии со спецификацией seriallite поправлены модули авроры: - standard_cc_module.vhd, - gtx.vhd, - sym_gen.vhd. Сравните файлы архиве mSimple_optica_altera_xilinx.rar.

-

Была похожая задача. Организовывали связь по оптике 25 метров. 6 плат Altera stratix 2 gx с SFP+ 2 gb с одной стороны и Xilinx Virtex 6 6 SFP+ с другой стороны. Связь осуществлялась протоколами serial lite/aurora. В стыковке serial lite и авроры могу помочь. Все сводится к редактированию модулей клоковой компенсации.