maxics

Участник-

Постов

287 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о maxics

-

Звание

Местный

Посетители профиля

4 466 просмотров профиля

-

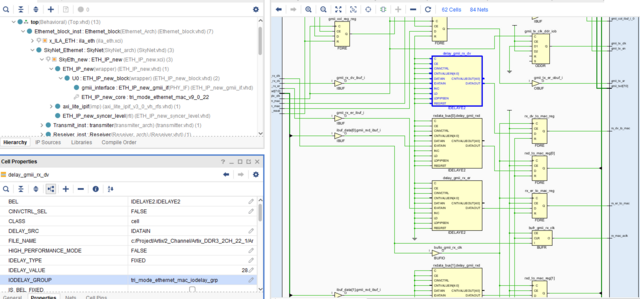

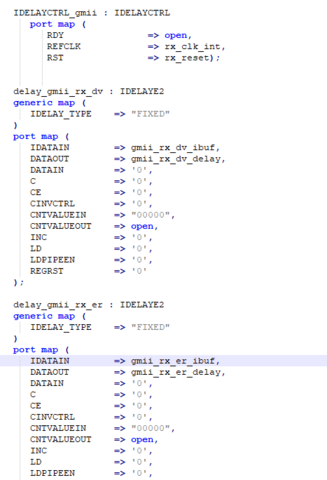

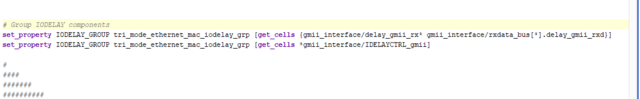

Сделал как вы сказали, примитивы IDELAYE2 находятся в группе tri_mode_ethernet_mac_iodelay_grp, при этом я не вижу IDELAYCTRL, хотя я его добавил: IDELAYCTRL_gmii : IDELAYCTRL port map ( RDY => open, REFCLK => rx_clk_int, RST => rx_reset); и прописал атрибуты: attribute IODELAY_GROUP : string; attribute IODELAY_GROUP of IDELAYCTRL_gmii: label is "tri_mode_ethernet_mac_iodelay_grp";

-

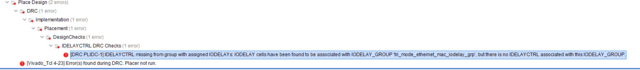

Вставил Idelayctrl И добавил строчку в xdc Всё равно выдаёт ошибку(( [DRC PLIDC-1] IDELAYCTRL missing from group with assigned IODELAYs: IODELAY cells have been found to be associated with IODELAY_GROUP 'tri_mode_ethernet_mac_iodelay_grp', but there is no IDELAYCTRL associated with this IODELAY_GROUP.

-

Это в XDC нужно прописывать? Каким образом?

-

В проекте работаю с коркой MIG DDR3 и Tri Mode Ethernet MAC(9.0). Перенёс проект из Vivado 18.2 в 22.1. Появилась такая ошибка, не могу понять в чём причина. Кто-нибудь сталкивался?

-

Нет, модуль покупной. Это Debug FSBL в консоль: Xilinx First Stage Boot Loader Release 2021.1 Jul 26 2024-17:07:46 Devcfg driver initialized Silicon Version 3.1 Boot mode is SD SD: rc= 0 SD Init Done Flash Base Address: 0xE0100000 Reboot status register: 0x60400000 Multiboot Register: 0x0000C000 Image Start Address: 0x00000000 Partition Header Offset:0x00000C80 Partition Count: 3 Partition Number: 1 Header Dump Image Word Len: 0x000940E0 Data Word Len: 0x000940E0 Partition Word Len:0x000940E0 Load Addr: 0x00000000 Exec Addr: 0x00000000 Partition Start: 0x000065D0 Partition Attr: 0x00000020 Partition Checksum Offset: 0x00000000 Section Count: 0x00000001 Checksum: 0xFFE3D51E Bitstream In FsblHookBeforeBitstreamDload function PCAP:StatusReg = 0x40000A30 PCAP:device ready PCAP:Clear done Level Shifter Value = 0xA Devcfg Status register = 0x40000A30 PCAP:Fabric is Initialized done PCAP register dump: PCAP CTRL 0xF8007000: 0x4C00E07F PCAP LOCK 0xF8007004: 0x0000001A PCAP CONFIG 0xF8007008: 0x00000508 PCAP ISR 0xF800700C: 0x0802000B PCAP IMR 0xF8007010: 0xFFFFFFFF PCAP STATUS 0xF8007014: 0x00000A30 PCAP DMA SRC ADDR 0xF8007018: 0x00100001 PCAP DMA DEST ADDR 0xF800701C: 0xFFFFFFFF PCAP DMA SRC LEN 0xF8007020: 0x000940E0 PCAP DMA DEST LEN 0xF8007024: 0x000940E0 PCAP ROM SHADOW CTRL 0xF8007028: 0xFFFFFFFF PCAP MBOOT 0xF800702C: 0x0000C000 PCAP SW ID 0xF8007030: 0x00000000 PCAP UNLOCK 0xF8007034: 0x757BDF0D PCAP MCTRL 0xF8007080: 0x30800100 DMA Done ! FPGA Done ! In FsblHookAfterBitstreamDload function Partition Number: 2 Header Dump Image Word Len: 0x00026004 Data Word Len: 0x00026004 Partition Word Len:0x00026004 Load Addr: 0x00100000 Exec Addr: 0x00100000 Partition Start: 0x0009A6B0 Partition Attr: 0x00000010 Partition Checksum Offset: 0x00000000 Section Count: 0x00000001 Checksum: 0xFFCF36D2 Application Handoff Address: 0x00100000 In FsblHookBeforeHandoff function SUCCESSFUL_HANDOFF FSBL Status = 0x1 Загружается всё верно вроде. Не могу понять откуда сбои, и почему через JTAG корректно всё работает?

-

В чём может быть проблема?

-

Использую в работе плату с ZYNQ-7000. На плате предусмотрена загрузка как по JTAG, так и через SD карту. В проекте использую DMA. Так вот наблюдаю следующую картину, если я загружаю PL и PS через JTAG, то проект работает штатно, но если я гружусь с SD, то вижу глюки при работе с DMA (зависание PS или неправильная работа). Для SD делаю BOOT.bin с помощью Fsbl (код в Fsbl не менял)

-

Запаял в параллель 316 кОм. Померял, ровно 5 кОм. Не помогло((

-

Схема: ETH.pdf

-

Сброс пробовал секунду держать, не помогает. Клок уже подан, потом ресет даю. Пробовал с рабочих плат снимать резонатор с конденсаторами, не помогло. Перепаивал конденсаторы на резонаторе в плюс и в минус, не помогло, Резистор ставил 470к, 1 М, 2М, 10М, не помогает((

-

Выявилась следующая проблема на платах с PHY 88E1111. Фишка подсоединена к ПЛИС. Работает в режиме 1G. На 10%-и всех плат не поднимается линк на холодную, т.е включаю плату, линка нет и не появится, даже если дергать ETH_Resetn. Плата прогревается, выключаю, потом включаю - линк поднимается. В чем может быть причина. Номиналы напряжений все в норме на холодную

-

Ещё вопрос. Если LAN кабель вставят в порт 1G, будет-ли установлен линк 1G без реконфигурации IP-ядра?

-

Спасибо за ответ. Посмотрел Realyek, использует интерфейс HSGMII. Он аналогичен SGMII? Проблем с подключением ПЛИС не будет?

-

С таким кто-нибудь работал : GPY211? Доступен, даташит без NDA. Вроде классический SGMII, который я планирую завести на GTP трансиверы Artix далее на 1/2.5G Ethernet ядро. Правильно я мыслю?

-

Посоветуйте PHY 2.5G

maxics опубликовал тема в Fast Ethernet/Gigabit Ethernet/FibreChannel

Планирую на Artix Xilinx поднять Ethernet 2.5G. Посоветуйте чип физического уровня для реализации данной задачи.