-

Постов

122 -

Зарегистрирован

-

Посещение

-

Победитель дней

1

Сообщения, опубликованные pavlovconst

-

-

Здравствуйте!

Делаю аппаратный контроллер (HMC) памяти DDR3 на CycloneV.

Создал два порта Avalon-MM по 32 бит - один для JTAG Debug Master, второй - для штатного (моего) контроллера.

Через JTAG Debug Master память пишется и читается, из чего делаю вывод, что временнЫе настройки чипов памяти я поставил правильные.

Через штатный контроллер могу питать в память, и единичные записи и берсты проходят. Но вот чтение поднять никак не получается.

Контроллер принимает 2 первых запроса по 8 слов, а на третьем поднимает waitrequest и больше его не опускает. Никогда. Сигнал readdatawalid вижу где-то вдалеке и только один.

Может кто-то сталкивался с таким? Что я делаю не так?

Обязательно ли логику мастера описывать в виде компонента QSYS, сейчас весь авалон у меня экспортирован из QSYS...

-

Нестабильность выставляется та же самая, меняются лишь множители и делители PLL.

Не влияет - судя по таймингу после разводки.

Подтверждаю.

Я тоже попробовал менять настройки PLL в проекте с непроходящими таймингами.

Я ожидал, что при увеличении джиттера на входе тайминг станет еще хуже.

Но получил точно такие же знеачения TNS. Странно...

-

Да, эксперименты подтверждают, что разницы нет.

Расскажите, как вы выяснили, что не влияет?

Когда мастер генерирует исходники PLL, он также создает файл с констрейнами для выходных сигналов.

Величина заявленной вами нестабильности на входе PLL повлияет на расчетную нестабильность выходов, а это, в свою очередь, повлияет на расчет времянки всех блоков, затактированных через PLL.

-

Еще не продано. Предлагайте вашу цену

-

Только вот это -

these 7 series components are only supported through a 7 series MIG generated design.These blocks are not documented for general use and must be used through MIG -

Извините, уже продано

-

-

Опубликовано · Изменено пользователем Кoнстантин · Пожаловаться

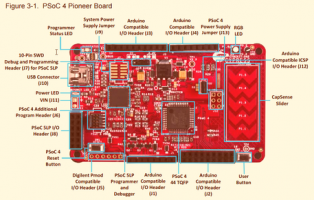

Производитель Cypress

Название CY8CKIT-042 PSoC 4 Pioneer Kit

На плате:

Микропроцессор ARM Cortex M0

USB-программатор

Емкостной датчик-слайдер

Разъемы ввода-вывода в стандарте Arduino

Страница на сайте производителя

http://www.cypress.com/documentation/devel...c-4-pioneer-kit

Фото моего комплекта - https://yadi.sk/d/jydFTvkXncda5

Цена 500р. (Петербург)

Доставку оплачивает покупатель

-

В статье приемник (только приемник) занимает 5000 ячеек из 22000. Можно легко найти ПЛИС в десятки и даже сотни раз более емкие, другой вопрос - сколько это стоит.

Напишите, что вы хотите сделать?

-

Существуют плисы со встроенными радио модулями до 1Ghz?

Вообще ПЛИС - это цифровое устройство, поэтому встроенного радио нет.

-

Осциллограф еще в продаже

-

-

По хорошему 2 триггера надо бы :)

А в военное время - до 16-и...

-

А вот тут поподробнее. Какие дополнительные констрейны нужно прописать? Ведь формально если мы указали тактовую на выходе до делителей всё остальное вычисляется. Хватит ли раскладчику одного таймспека на частоту или нужно ещё что-то?

Достаточно обконстрейнить быстрый клок. В общем-то и все.

У вас нет асинхронных проблем. Clock domain - всего один. Да, в нем есть еще сигнал, который меняет состояние каждый второй такт (вы его зовете медленным клоком) - ну и ОК. А еще есть внешний ресет. Да, это внешний асинхронный сигнал, его нужно синхронизировать - записать в регистр по клоку. А на выходе регистра будет он уже синхронным в этом клок домейне. ОСтальные расчеты оставьте технике.

-

Опубликовано · Изменено пользователем Кoнстантин · Пожаловаться

Напрмер банальное. Глобальный ресет приходит на триггеры не одновременно. И соответственно есть шанс что часть триггеров уже сработают а вторая половина ещё в ресете. Если схемотехнически не обеспечить правильный ресет то схема будет с особенностями. Причём конкретную раскладку можно отсимулить и увидеть эти особенности. Но со следующей всё придётся делать заново.То, что происходит в схеме между фронтами тактовой частоты - вас волновать по идее не должно. Вы же цифровым дизайном занимаетесь, а не аналоговым. Роутер постарается развести так, чтобы К СЛЕДУЮЩЕМУ фронту клока на выходе всех регистров был годный результат. Именно для этого пишутся констрейнты, в которых явно прописываются частоты и нестабильности клоков. Если времянка сошлась, схема БУДЕТ работать на этой частоте.

Чисто теоретически должно работать. А практически кто проконтролирует время сетап-холд? Или раскладчик поймёт всё правильно и я зря парюсь?Вот, это правильные слова! Нужно написать XDC constraints - и сетапы-холды будут проверены автоматически, и даже репорт будет генериться на каждую реинкарнацию дизайна.

-

мы можем начать считать быструю частоту в два разных момента времени

Я считаю, такого быть не может. Фронты не могут взяться ниоткуда. При делении частоты тем более.

Еще раз поясните, откуда берется исходный тактовый сигнал и каким образом вы его делите.

Даже если, допустим, медленная появляется из PLL и есть непредсказуемое время на ее раскачку, тогда сигнал locked можно использовать как enable для счетчиков, чтобы начать считать от одного момента во времени

Очень полезно воспользоваться симулятором

-

Опубликовано · Изменено пользователем Кoнстантин · Пожаловаться

Если вам нужно знать фазовые соотношения - то они же и так известны. Частоты отличаются ровно в два раза )

Считайте такты быстрой и сможете пересчитать в медленную делением на два. Медленную умножайте.

Каждый триггер на пути сигнала будут задерживать сигнал на один такт той частоты, которым он тактируется. Это можно учесть при отладке в симуляторе.

-

Время формирования нового сообщения может быть существенно меньше времени передачи этого сообщения через последовательный порт. И в этом случае FIFO позволяет записывать на одной скорости, а считывать на другой.

Я так и хочу. Где взять FIFO, в которую можно закинуть сразу все сообщение, и что делает FSM у FIFO на входе?

-

iosifk, Спасибо. Если можно, давайте обсудим в рамках форума.

Что делает FSM? Подсовывает байты подряд на вход FIFO? Тогда зачем нужна FIFO? если мы ее руками фактически уже сделали?

-

Здравствуйте!

Разбираюсь с написанием UART-а на Kintex-7. Есть вопрос по архитектуре.

Допустим, есть модуль трансмиттера

module uart_tx (clk,rst,tx_data,tx_data_valid,tx_data_ack,txd); output txd; input clk, rst; input [7:0] tx_data; input tx_data_valid; output tx_data_ack;

Он занимается выщелкиванием битов, с ним все понятно. Перед ним мне кажется правильным поставить очередь, которая занималась бы постепенной выдачей байтов, по одному. А на вход этой очереди хочется подавать сразу все сообщение. В идеале - переменной длины. Произошло некое событие - я сразу же в один такт помещаю в очередь, скажем, 18 байт, а дальше трансмиттер мееедленно их вычитывает. В FIFO генераторе можно сделать различную ширину входного и выходного портов, но только с отношением до 8:1. Не очень удобно.

Подскажите, я вообще в правильную сторону думаю? Как обычно решается эта задача?

-

Продам абсолютно новую отладочную плату, в заводской неоткрытой коробке

DE0-Nano Development and Education Board

Сайт производителя - http://www.terasic.com.tw/cgi-bin/page/arc...93&PartNo=1

Статьи на хабре с этой платой - http://habrahabr.ru/search/?q=de0-nano

Статьи в сообществе с этой платой - http://we.easyelectronics.ru/search/topics/?q=de0-nano

Характеристики:

ПЛИС Cyclone® IV EP4CE22F17C6N

Встроенный программатор-отладчик USB-Blaster

32MB SDRAM

2Kb I2C EEPROM

Two 40-pin Headers (GPIOs) provides 72 3.3V I/O pins

8 green LEDs

2 debounced push-buttons

4 dip switches

G-Sensor

ADI ADXL345, 3-axis accelerometer with high resolution (13-bit)

NS ADC128S022, 8-Channel, 12-bit A/D Converter

Цена 3500р. Я из Петербурга. Если надо, вышлю почтой по России.

Не работает чтение DDR3 на CycloneV

в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Опубликовано · Пожаловаться

Возможно, сигнал waitrequest не инвертированнный на самом деле (хотя суффикс "_n" намекает об обратном), и мне стоит ждать 6 тактов после первого запроса?