dinam

Свой-

Постов

1 625 -

Зарегистрирован

-

Посещение

Весь контент dinam

-

Всё присматриваюсь к TMC5160A. На мой взгляд самый продвинутый драйвер на сегодняшний день.

-

Выброс при включении DCDC TPS54340

dinam ответил DpInRock тема в В помощь начинающему

Я исходил из того, провод должен быть не толще, а иметь меньшую индуктивность. По крайней мере мне такие кабели помогли. И я бы так слепо не верил в непогрешимость TI. Имел дело с ОУ OPA354. Все режимы работы соответствовали datasheet, а на выходе что-то типа инверсии сигнала. -

Выброс при включении DCDC TPS54340

dinam ответил DpInRock тема в В помощь начинающему

DpInRock У меня питание от USB. Как вы уже писали, подобные импульсы проявляются, когда щуп осциллографа замыкаешь на землю щупа и касаешься этой замкнутой конструкцией общего провода в плате, например, корпуса разъёма USB. Сильно снизить эти импульсы позволяют подобные кабели с низкой индуктивностью. Поэтому я делаю вывод, что это наведенные импульсы и реально их в устройстве нет. P.S. Кабель с USB разъёмом позволяет течь паразитным токам мимо моего устройства. Моё устройство запитываю от USB хаба, который располагается рядом с осциллографом. Эти кабелем соединяю осциллограф и USB хаб. -

Выброс при включении DCDC TPS54340

dinam ответил DpInRock тема в В помощь начинающему

Я кажется понял в чем у вас дело. При подсоединении земли на щупе к плате у вас замыкается контур. И какие-то токи начинают течь через землю щупа осциллографа. Пружинка не спасает. В моем случае сильно уменьшить такой импульс позволяют подобные кабели. Один конец подключается к осциллографу, а другой к вашей плате. И большая часть этих паразитных токов начинают течь через эти дополнительные кабели. Откуда появляются эти токи я до конца не разобрался, но иногда на подобное натыкаюсь когда плата подключена по USB к компьютеру. -

Выброс при включении DCDC TPS54340

dinam ответил DpInRock тема в В помощь начинающему

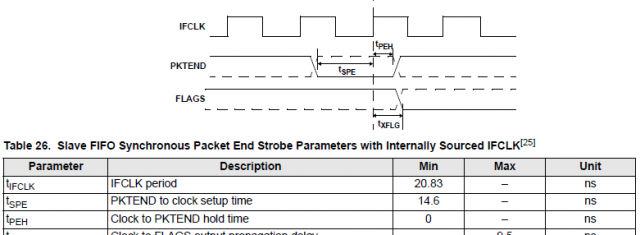

Да нет ничего непонятного. Вы нарушили требования datasheeta. В котором конкретно прописаны типы диэлетрика входного конденсатора и его минимальная емкость. И даже прописано что это не номинальная емкость конденсатора, а та что осталась при приложении к нему вашего входного напряжения. Такую конкретику я вижу совсем не часто. Даже больше скажу, с некоторых пор я перестал себя считать грамотнее разработчиков микросхем. И если в datasheet приведен пример разводки, то стараюсь следовать ему по максимуму. Например, не менять размеры конденсаторов, сторону их размещения и расстояние до микросхемы. -

А я вот вас не понял. Чего вы хотели сказать? Сначала, я сказал, что это стандартный подход, например для FPGA. Если вы не поняли, то это можно и на мк распространить, если есть необходимость. Потом я задал конкретный вопрос на следующую фразу: И до сих пор хочу понять какие конденсаторы народ считает лишними.

-

Понятно, по существу дела сказать нечего.

-

А я вот не понял. Скажем есть пять напряжений питания FPGA. Используется пять независимых стабилизаторов. Перед каждым стоит керамика и после каждого керамика, местоположение (в непосредственной близости и на той же стороне) и номиналы которых прописаны в datasheet. Т.е. минимум 10 конденсаторов, необходимых для корректной работы самих стабилизаторов. Плюс россыпь конденсаторов, необходимых для обеспечения нужного импеданса каждого выходного напряжения. Какие конденсаторы вы повыкидывали?

-

Да на самом деле это стандартный подход. Я, например, пользуюсь PDN design tool для того чтобы понять сколько и каких конденсаторов надо использовать.

-

Ставите микросхемку для зарядки и балансировки суперконденсаторов, например https://www.analog.com/en/parametricsearch/11413. Идете на DigiKey, выбираете суперконденсаторы. При их подборе автоматически получается скорее всего комбинированная схема соединения.

-

Вы так и не озвучили задачу. Почему 1-2 конденсатора не решают вашу задачу? Не хватает тока? Напряжения? Емкости?

-

С FX2 по крайней мере для меня было очень удобно заливать прошивку в FPGA через USART в синхронном режиме. Самый мелкий CycloneV загружается около 1 сек. Сейчас смотрю на FT600/602 и не представляю как так же красиво конфигурировать CycloneV.

-

Не знаю с каким интерфейсом нужна вам камера. Из сенсоров могу посоветовать MT9M001C12STM. Наверное самый дешевый для такого размера, простой параллельный интерфейс.

- 20 ответов

-

- фотоматрица

- зеркального фотоаппарата

-

(и ещё 1 )

C тегом:

-

to Sergey_Bekrenyov То ли не понял вашу идею, то ли не понял как её реализовать. Вы предлагаете способ уменьшить Clock delay, которая у меня порядка 5 нс? Если не сложно, можете чуть подробнее? Сделал по спадающему такту. Все получилось.

-

Товарищу надо не растянуть изображение, а сфокусировать на маленькую матрицу.

- 20 ответов

-

- фотоматрица

- зеркального фотоаппарата

-

(и ещё 1 )

C тегом:

-

В наших задачах, чем большей точности удасться добиться, без существенного усложнения/удорожания железа, тем лучше. Ну и да, обычно мы работаем с отраженным светом лазера. Кстати, если напрямую лазером засветить, то и матрицу можно сжечь.

- 20 ответов

-

- фотоматрица

- зеркального фотоаппарата

-

(и ещё 1 )

C тегом:

-

Я тоже не понял зачем ставить матовое стекло, так что не переживайте .

- 20 ответов

-

- фотоматрица

- зеркального фотоаппарата

-

(и ещё 1 )

C тегом:

-

Адресно к пикселям обращаться нельзя. У КМОП матриц есть понятие ROI(Region Of Interest). Про сенсоры CCD я думаю вам стоит забыть по вышеописанным причинам, и смириться потерей денег из-за покупки icx453. Я не знаю какой интерфейс используется между Ардуино и камерой. Поэтому конкретную матрицу посоветовать не могу. Но знаю, что цена матрицы сильно определяется её размером. И поэтому если разрешения существующей камеры хватает, то может попробовать применить другой (большой) объектив?

- 20 ответов

-

- фотоматрица

- зеркального фотоаппарата

-

(и ещё 1 )

C тегом:

-

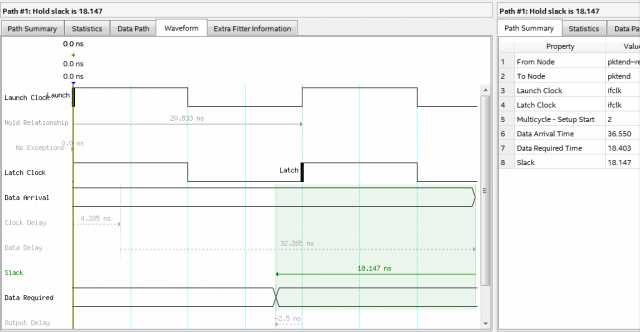

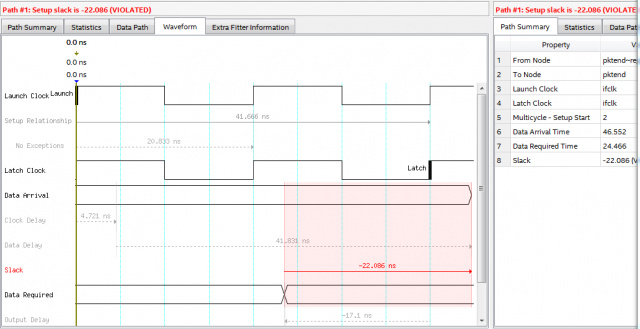

Ну на самом деле реально все работает в железе, и вроде стабильно. Но захотелось сделать правильно, а не методом научного тыка, и убрать красные слаки. По поводу лучше вводить разброс реальных значений - знаю, для начала хотел не так жестко задать.

-

Это не самый "плохой" сигнал есть и tsu=18.7 нс, чип CY7C68013A. На полтакта это сделать по спадающему фронту? Если да, то надо почитать как правильно это сделать и констрейны прописать.

-

Я немного другое вижу. Во первых, тактовая FPGA немного задержана, относительно тактовой приёмника , поэтому для приёмника данные должны прийти во втором такте. Data Arrival Time у setup оказалось таким большим, что оно уже залезло на третий такт. Т.е. если не использовать set_multicycle_path, то с output register, наносекунд 6 не хватает, насколько я помню. Если использовать set_multicycle_path, то сразу перепрыгиваем на третий такт. А промежуточного значения не получается.

-

Тактовую выдает сам приемник сигнала pktend. Приёмник выдает 48 МГц 3,3 В, а банк FPGA питается от 1,5 В. Поэтому используется преобразователь уровней.

-

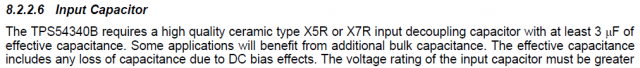

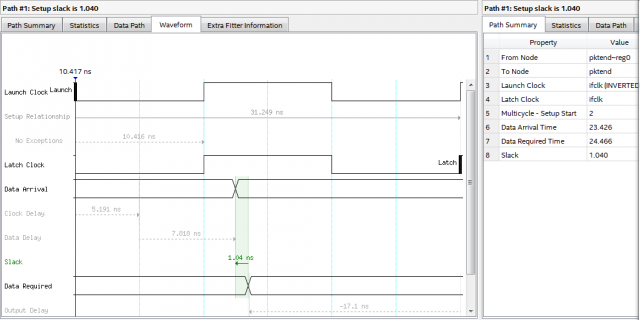

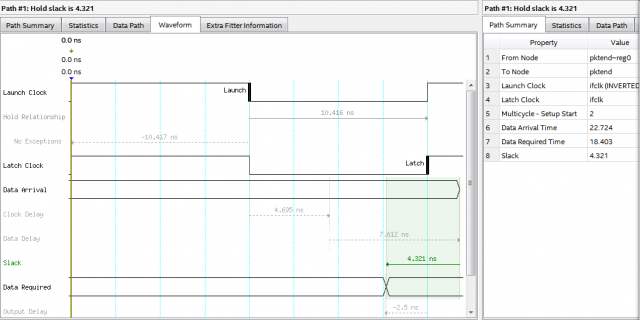

Навеяло соседним топиком с set_multycycle_path. Есть выход, один из многих, у которого при правильных на мой взгляд констрейнах они не выполняются. create_clock -name {ifclk} -period 20.834 -waveform { 0.000 10.417 } [get_ports {ifclk}] set_output_delay -add_delay -max -clock [get_clocks {ifclk}] [expr 14.600 + 2.500] [get_ports {pktend}] set_output_delay -add_delay -min -clock [get_clocks {ifclk}] [expr 0 + 2.500] [get_ports {pktend}] # при такой записи (set_multycycle_path -setup N и без -hold [N-1]) фиттер должен сделать так, чтобы самый длинный путь был не больше T*N, а короткий не короче T*[N-1] set_multicycle_path -setup -start -to [get_keepers {pktend}] 2 Даже с использованием output register, констрейн по setup не выполняется. Решил применить set_multycycle_path, чтобы pktend сдвинуть на такт. Опять не помогло. Да и разбег между Data Arrival Time у setup и hold стал слишком большой 46.552-36.550=10,002 нс. А у меня должно быть не более 20.834-14.6=6,234 нс. FPGA-CycloneV. Используется преобразователь уровней, поэтому появилась задержка в приходе тактовой на FPGA 2.5 нс. Также не могу понять значение clock delay нормально или великовато? Тактовая ifclk заведена на спец вход и является Global Clock. Провести ifclk через pll и сдвинуть по фазе не могу, уже две pll питаются от этого входа.

-

Я за драйвер ШД, сделанном на A4989. Можете поиском воспользоваться на этом форуме, и почитать, каких результатов я на этой микросхеме добивался.

-

В свое время задался как подобрать диоды Шоттки для мостовой схемы, чтобы шунтировать медленные диоды в полевых транзисторах. Много моделировал в LTspice. Для моей схемы наиболее оптимальные оказались RBR2MM60A, RBR2L60A. Подбирал по минимальному всплеску на шунте, вставленный в минус напряжения питания.