-

Постов

2 917 -

Зарегистрирован

-

Посещение

-

Победитель дней

2

GenaSPB стал победителем дня 2 июня 2023

GenaSPB имел наиболее популярный контент!

Репутация

11 ХорошийИнформация о GenaSPB

-

Звание

Гуру

- День рождения 02.03.1964

Контакты

-

Сайт

Array

-

ICQ

Array

Информация

-

Город

Array

-

Как же оно у китайцев работало...или они в dts того образа предлагали допиливать? Так как я понимаю dts на этапе подготовки образа используется.

-

А может кто подсказать, тут нашло DSI дисплей? Что надо набрать, чтобы что-то на дисплей вывелось? logfile.log

-

2C/2D на соей плате не откликается... что есть - я написал Для инита вот тут есть linux_kernel_for_d1/drivers/video/fbdev/sunxi/disp2/disp/lcd/tft08006.c at 5703a18aa3ca12829027b0b20cd197e9741c4c0f · rvboards/linux_kernel_for_d1 (github.com) tdjastrzebski/ICN6211-Configurator: ICN6211 Configurator (github.com) Но как добраться до... Пока ищу образ

-

tft08006 ICN6211 ICN8205 Architecture Speccification (aw-ol.com) Правда, результат диагностики не бъётся с i2c адресами этого чипа: // addr8bit=0x70, addr7bit=0x38 // addr8bit=0x8A, addr7bit=0x45 готовый образ не включает преобразователь подсветки. может что-то и покзывает в темноте... upd: перемычка помогла с подсветкой - но не показывает

-

Отсюда скачать образ может кто-нибудь? https://whycan.com/t_7566.html upd: скачал

-

Судя по ответам, mipi dsi давно и уверенно готовят? Живой исходник есть?

-

Да конкретный.. как на расбери. Waveshare 5". Судя по всему, его точно все знают... таеие разьемы под 2 lane на многих моедвл sbc стоят

-

Да конкретный.. как на расбери. Waveshare 5". Да вообще любой 800 480

-

Да конкретный.. как на расбери. Waveshare 5" Ну выход из sleep он врожде стандартизирован. Может какой-то generic 800x480 2 lane?

-

Lvds проверено. Mipi dsi пока нет. Кстати, может есть у кого-нибудь образ под манго пи т113 с выводом на mipi-dsi? I2C с модуля отвечает - тач и еще какой-то чип

-

Сделал переходники для подключения к 40-ногому разъему MangoPI пары видов дисплеев: LVDS (одно и двух-канальных, выходной разъем - 2 мм шаг двухрядный) и блока mipi-dsi интерфейса от RaspberyPI. Джамперы для возможной подачи питания 3.3 на тестируемый дисплей не от MangoPI.

-

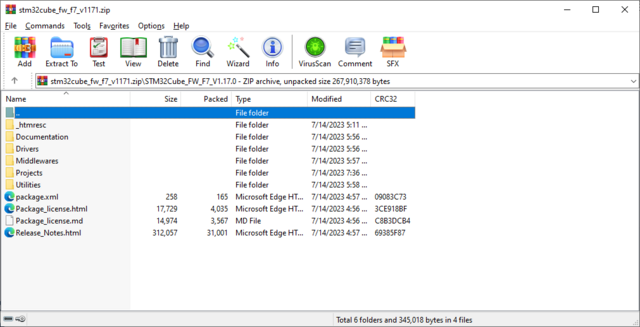

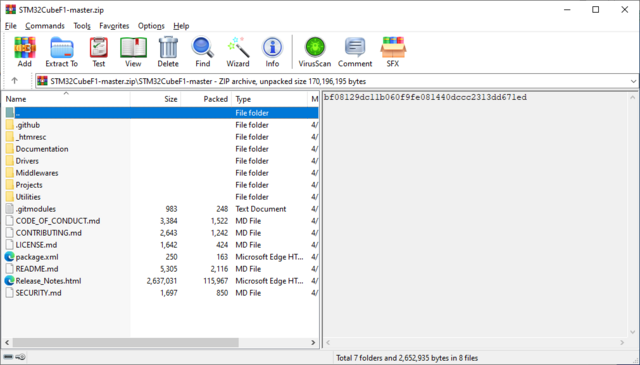

https://github.com/STMicroelectronics Тут, кажется

-

Где подтяжки (pull-up) на входах CS ADExxxx? Аналоговый комутатор переключает - CS хранит на своей ёмкости состояние.

-

Подскажите по маркировке

GenaSPB ответил whale тема в В помощь начинающему

корпус бы подсказали