andk

-

Постов

215 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные andk

-

-

7 часов назад, makc сказал:

Это неважно, патч не зависит от версии, на сколько мне известно. Генератор лицензии тем более.

Патчи универсальны. Если бы они не работали, то среда бы просто не запустилась. Проблема скорее всего не в патче, а в ошибке в самой среде. Попробуйте оттранслировать какой-либо простой тестовый проект на настройках по-умолчанию.

Хм. Вручную удалил каталог impl и проект развёлся... Чудо.

Дальше пока не смотрел. Если чудеса продолжатся, отпишусь.

Лечил с помощью "gwlicgen-win+lin_1.0.2.7z"

Попробовать повторить с "gwlicgen-win+lin_1.0.3.7z" ?

Как бы узнать, чем они отличаются..

-

4 часа назад, makc сказал:

/pub/FPGA/_Gоwin_/Сrасks

Да нет, с глазами всё нормально..

gmdlicgen-1.0.7z - не взлетает

gwlicgen-win+lin_1.0.3.7z - перелечивает, IDE просто падает после разводки, видимо на этапе создания прошивки.

В любом раскладе, эти файлы датированы 05.2022, то есть явно раньше появления версии 1.9.8.10

Екзешники уже отличаются от тех, которые они пытаются пролечить.

А, не сказал что ищу под Win.. Может в этом дело?

-

11 часов назад, makc сказал:

Существует и лежит в известном месте.

Кхм. Что-то у меня с глазами.. Можете пальцем показать?

-

Подскажите, пожалуйста - а лекарство для версии 1.9.8.10 существует?

-

Программатор в этой версии работает с Tang Nano 9K без бубнов! Йес!

Про симулятор ничё не понял - на панели нажимаешь кнопку - перекидывает на сайт https://metrics.ca и чё дальше делать - непонятно...

По приметам - облачный симулятор.

To be continue..

Нашёл:

Contact our team to start your evaluation:

Такое себе..

-

Double kill! Вы знали! :)

-

Я откатил программатор на предыдущюю версию. 1.9.8.06 работает нормально. -1 не работает вообще.

-

Да, вы абсолютно правы.

Я разобрался после разглядывания каждого иероглифа в РАБОЧЕМ примере.. :)

Имена входных и выходных портов для PSRAM интерфейса должны быть идентичны:

.O_psram_ck(O_psram_ck_o), //output [1:0] O_psram_ck

.O_psram_ck_n(O_psram_ck_n_o), //output [1:0] O_psram_ck_n

.IO_psram_dq(IO_psram_dq_io), //inout [15:0] IO_psram_dq

.IO_psram_rwds(IO_psram_rwds_io), //inout [1:0] IO_psram_rwds

.O_psram_cs_n(O_psram_cs_n_o), //output [1:0] O_psram_cs_n

.O_psram_reset_n(O_psram_reset_n_o), //output [1:0] O_psram_reset_n

Это по умолчанию генерит китайский волшебник версии 1.9.8.06 - не работает!А это рабочий вариант:

.O_psram_ck(O_psram_ck),

.O_psram_ck_n(O_psram_ck_n),

.O_psram_cs_n(O_psram_cs_n),

.O_psram_reset_n(O_psram_reset_n),

.IO_psram_dq(IO_psram_dq),

.IO_psram_rwds(IO_psram_rwds)

Все остальные сигналы можно переименовывать как угодно. КЕТАЙ - сила! :)

-

Скажите, а кто-нибудь поборол внутреннюю PSRAM в GW1NR-9?

Что-то у меня ничего не получается...

Синтез нормально(без ошибок и варнингов),

А разводка сначала сыплет варнингами типа:

WARN (PA1001) : Dangling net 'DF_d[0]'(source:'dq_iodelay_gen0[0].[0].iodelay') in module '~psram_wd.PSRAM_Memory_Interface_HS_Top' has no destination

А потом ошибки типа:ERROR (PR2067) : Instance 'VideoPsRam/u_psram_top/u_psram_wd/cs_iobuf_gen[0].cs_obuf' in hclk tree must have constraint

Где эти constraint найти/прочитать?

Такое ощущение, что разводчик не знает что с этим компонентом делать.

Может у кого есть рабочий пример?

Китайский пример пробовал - ничего не понял..:( я не настоящий китаец..

Ну и да, у китайских примеров другие камни, просто так не поменяешь. (по крайней мере мне запросто не удалось)

-

Стр. 2-5

If you use bank 1A for ADC, you cannot use the bank for GPIO.

Обсуждение было в Altera ADC core

Автор: justontime, 25 сентября 2018 в Системы на ПЛИС - System on a Programmable Chip (SoPC)

-

Epson? Abracon? Golledge? Ecsxtal? да много их.

Частота выглядит не стандартной, видимо придётся программировать нужную вам. (не должно быть проблемой)

Другое дело, нужно выяснить требуемые рабочие параметры (стабильность, джиттер, диапазон рабочих температур, и т.п.) - это может быть очень важно.

Если чисто попробовать, можно заказать Epson что-то типа sg8002 и в заказе указать необходимую частоту. Многие продавцы имеют программаторы для них.

-

Вещь старинная, цены немалой... :)

Хотелось бы, конечно, выставить цену как на mouser, но вряд ли найдутся желающие :)

Ждём того, кому действительно нужно... поторгуемся.. недолго

-

-

Читать раздел "Intel MAX 10 Device Feature Options"

То же есть в документе "m10_overview.pdf" на 5 странице :)

-

Качество питания на памяти смотрели? Они очень прожорливые..

-

19 часов назад, _pv сказал:

если фронты дрожжат на +-25% от периода (чтобы метод декодирования с задержкой на 1.5 такта перестал работать нормально), то это явно не у приёмника проблемы.

Да, фронты дрожат, но к сожалению, чаще всего решение этой проблемы падает на приёмник...

В 31.07.2019 в 21:20, _pv сказал:без х8/х16 частоты, и ФАПЧей для восстановления клоков, есть ещё рабоче-крестьянские методы с задержкой на 1.5 такта.

http://ww1.microchip.com/downloads/en/appnotes/01470a.pdf

То, что описано у микрочипов - это частный случай, не описывающий процедуры стартовой синхронизации и выбора режима передачи на линии.

Опять, топикстартер где-то затаился, и не рассказывает, что ему действительно нужно и с какой реализацией протокола он имеет дело.

Посему что-то толковое подсказать не представляется возможным.

-

Позвольте я вставлю свои 5 копеек

Ваш вопрос очень сильно завязан на качество и тип(дифференциальный или одиночный) входного сигнала.

Если вход одиночный и чистенький - без дребезга, без искажений фаз и т.п.,

То ответ Вам дал dxp.

В противном случае (реальная жизнь, кхе-кхе) нужно отслеживать:

- разницу скоростей и/или джиттер - до +-25% от идеального синхросигнала

- дребезг

- фазовые искажения

- еще какую-нибудь бяку типа режима передачи в синхро бите (запрос-ответ)

Кроме как счетчиками (несколькими) не решить.

В реале хватает частоты х8-х16 от входной.

Еще хороший вариант - применить специализированные микросхемы приемопередатчиков.

Это снимет много головных болей

Data Delay Devices, HOLT INTEGRATED CIRCUITS к примеру.

-

-

И всё таки, настоятельно рекомендую вдумчиво покурить сей документ...

К примеру про ваш вопрос враги не скрывают истину:

Стр. 2-5

If you use bank 1A for ADC, you cannot use the bank for GPIO.

:)

-

Гхм. Подробный вопрос - подробный ответ.

Ну конечно кто-нибудь знает.

https://www.intel.com/content/dam/www/progr...10-adc-15.1.pdf

Просмотрите, там совсем немного - 60 страниц с картинками.

-

-

-

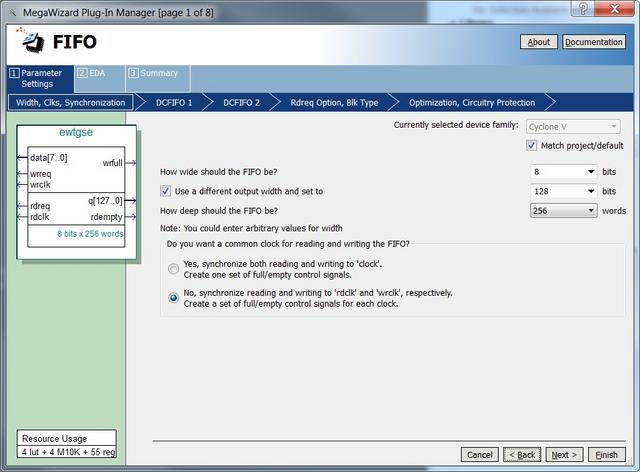

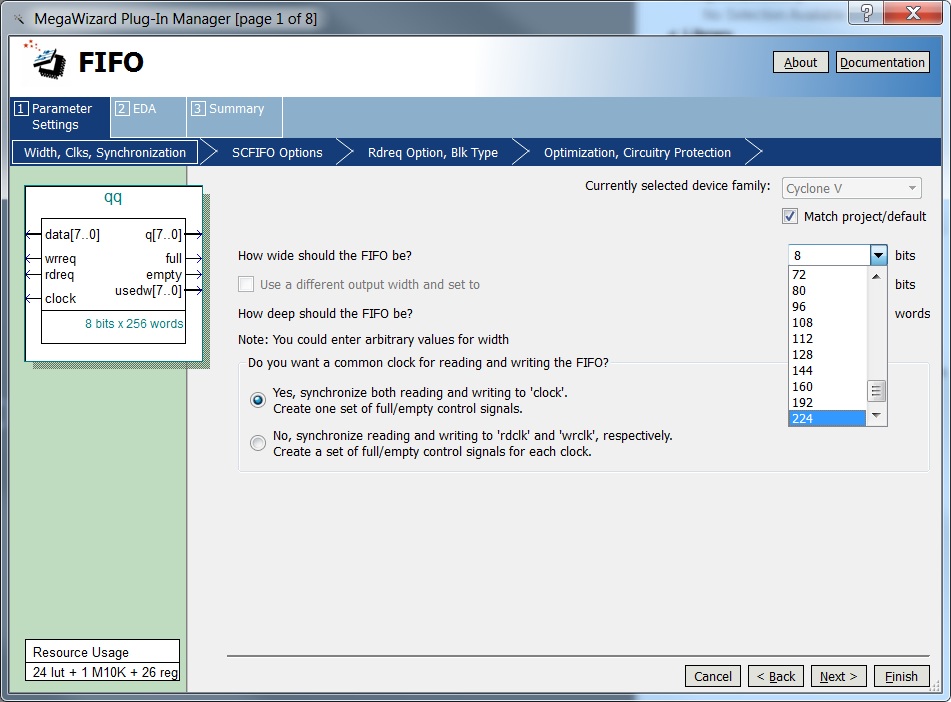

Эээ.. Что вы имели ввиду под словом "единица"?

В версии 18:

Разрядность данных - от 1 до 256.

Глубина - от 4 и до конца памяти (ну или триггеров).

Вообще, не плохо бы знать про какой камень идёт речь.

В приаттаченой картинке скриншот.

Если имеется ввиду разрядность 13*8=104 бита, возьмите ближайшее значение - 108.

-

Приветствую Всех!

Diamond 3.10

У меня сложилось субьективное мнение что LSE синтезирует лучше чем Synplify, макс. частота выше, разницы по LUTах нет. Правда девайс забит только на 40%.

А какой опыт у Вас?

Такая же фигня. Проект на LA4128, занято ~90%.

Ещё понравилось в LSE - человечески понятные текстовые конфиги.

(Ну это субъективно, конечно).

Настройка платы xc7z020clg400-2

в Работаем с ПЛИС, области применения, выбор

Опубликовано · Пожаловаться

По порядку (с учётом своего опыта)

Задача или решение? Если есть решение, то в чём проблема конкретно?

Если задача - то это другой вопрос, и однозначно ни кто не ответит, нужно разбираться с каждой проблемой по мере поступления.

Какая? Много наштамповала братская Китайская промышленность, не считая остального мира.

От Китайцев нужна только схема. Ну может ещё габаритно - присоединительные размеры.

Всё остальное - Xilinx.

Опыт появится сразу после рещения проблем 🙂

Если время и желание есть - всё сделается.

Учебников по программированию FPGA навалом, на любом языке этой планеты(про экскимосов, правда, не очень уверен).

Вам в Xilinx. Не нужно мучить себя китайским.

Озон - маленький филиал Али.

ПО у нас теперь всё под санкциями, поэтому Вам к пиратам. Они добрые. 🙂

На форуме множество крутых спецов по FPGA и в том числе по Xilix. Будут конкретные вопросы - кто-нибудь ответит.

НО: Чтение документации и практические занятия - на Вас.

Подсказать что-то конкретное без представления о задаче, ТЗ, сроках и прочем организационном вряд ли возможно. На этой планете экстрасенсорные способности населения близки к нулю.

Поэтому:

1. Читайте документацию.

2. Пробуйте.

3. Если возникла проблема - спрашивайте конкретно.