zvs

Свой-

Постов

209 -

Зарегистрирован

-

Посещение

Весь контент zvs

-

Все. Разобрался. Если кому интересно: http://telesys.ru/wwwboards/fpga/263/messages/17989.shtml

-

(Альтеровское название кита - PCI-DEVKIT-2C35) Подскажите пожалуйста, что там за буферы на PCI стоят? Судя по каринке с сайта там на 32-битной половине платы стоят три 16-битных буфера (как-то для PCI Master'а маловато)и совершенно не видно никакой резисторной обвязки, как если бы это были рекомендуемые Альтерой SN74CBTD3384 от TI? Заранее спасибо!!! :)

-

Перевернутый ГОСТовский шрифт

zvs ответил zvs тема в Документация

Блин, интересно без меня развилась ветка :) - всем спасибо! Да, я имел в виду именно шрифты GostA и GostB выковырянные из "Компаса". Сам проблему решил с помошью программки Font Creator (версию не помню). В триале работает 30 дней. Шрифты получаются полноценные. -

HOSTID=000000000000 - т.е 12 нулей - столько сколько и должно быть циферок в MAC-адресе.

-

Насчет Мах 7000 - точно враки... На практике куда больше, хотя то что они гарпнтируют - это то, что они гарантируют, а там как фишка ляжет... По поводу Мах2 - был на семинаре в Ворнеже - дядечка русским по белому обещал 100 раз. Но вот как заметил уважаемый vetal, галка configure спасет ее от преждевременной гибели.

-

Quartus 5.0 - Cyclon

zvs ответил Jcs тема в Среды разработки - обсуждаем САПРы

Признайтесь, работаете в схематике? Если так, то тут два варианта: 1) сгенерировать себе "лошадку" с помощью мегавизарда, как и советуют; 2) не люблю я пользоваться мегавизардом (ну не люблю и все), поэтому читайте туманный хелп на altsyncram, и из списка параметров поудаляйте все, что связано с портом, который вы не будете использовать. -

Посоветуйте осциллограф

zvs ответил zvs тема в Метрология, датчики, измерительная техника

Вот, наконец определились с осциллом - 54642D от Agilent... Даже начальство обещало денежку дать... Граждане, подскажите пожалуйста у кого можно помотреть прайс на это (и другие) Агилентовское Чудо?? -

Ну вот... я случайно вернулся к этому посту и обнаружил, что он так и остался заброшенным. Исправляюсь. Указанная выше конструкция с generate работать отказалась - все компилируется, но RTL Viewer показывает какую-то глупость! (q4.1 sp2) ну и в результате работает вообще никак. По поводу заявления уважаемого v_mirgorodsky: "Potomu ya bi primenil LPM_COMPARE megafunction ili postavil bi "if" v tekste (v teorii, Quartus dostatochno umniy chtobi zamenit' "if" na LPM_COMPARE)." Не знаю, заменяет ли он конструкцию if именно на LPM_COMPARE, но RTL Viewer показывает именно ту картинку, которая мне была нужна - что-то очень похожее на примитив and8 из схематика. Самое забавное, что если if написать с else, т.е. SUBDESIGN test_gen ( a[7..0] : INPUT; b : OUTPUT; ) BEGIN IF a[] == b"10111111" THEN b = VCC; ELSE b = GND; END IF; END; Получается вот такая забавная вещь :) (в присоединенном изображении)

-

Сравнение двух сигналов

zvs ответил zvs тема в Работаем с ПЛИС, области применения, выбор

Вот это примерно то, что я хотел услышать, спасибо. Только не могли бы вы сослать меня на источник, откуда вы выяснили, что "это хороший критерий работоспособности системы"? -

Сравнение двух сигналов

zvs ответил zvs тема в Работаем с ПЛИС, области применения, выбор

Так и сделаю, спасибо! -

Сравнение двух сигналов

zvs ответил zvs тема в Работаем с ПЛИС, области применения, выбор

Сравнение не в реальном времени, и по всей видимости склонюсь к корреляции. Сейчас листаю "Цифровую обработку сигналов" от Айфичера. Только у него в этом вопросе как-то туговато с переходом к практике... Может посоветуете что-нибудь другое? -

Сравнение двух сигналов

zvs опубликовал тема в Работаем с ПЛИС, области применения, выбор

Прошу прощения за воможный оффтоп, но куда правильно запостить мой вопрос я так и не нашел. Стоит задача сравнения двух сигналов. Цифровые отсчеты одного ищ них хранятся в ПЛИС, второй получается посредством операций ЦАП-АЦП этих цифровых отсчетов и возвращением полученного цифрового сигнала обратно в ПЛИС. Ну если смотреть ширше - задача стоит в определении работоспособности этих АЦП и ЦАП. Может кто уже сталкивался с такой задачей? Направьте пожалуйста лопату, а то я даже как-то теряюсь в каком направлении копать. Заранее спасибо. -

С днем спецухи 2007 - "Радиотехника"!

zvs ответил 3.14 тема в Встречи и поздравления

Странно :unsure: , по-моему, все выпускники РГРТА\РРТИ в курсе, когда отмечается день их специальности. <{POST_SNAPBACK}> Выпускники ТРТУ тоже в курсе ;) -

Разводка питания на QFP микросхемах

zvs ответил zvs тема в Работаем с трассировкой

Кстати, вдогонку еще вопрос. Большие полигоны (земля, питание) на некоторых платах, которые я видел сделаны "сеткой". Насколько мне объяснили, это делается для того, чтобы плату "не повело" когда на верхнем слое заливки почти нет, а нижний практически полностью залит землей. Подскажите пожалуйста, насколько это верно, и стоит ли делать сетчатую заливку во внутренних слоях (для того-же питания, например). -

Разводка питания на QFP микросхемах

zvs ответил zvs тема в Работаем с трассировкой

На самом деле у меня 4 слоя. Всем спасибо, мне полегчало :) -

Разводка питания на QFP микросхемах

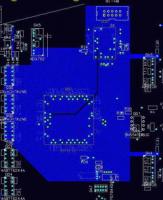

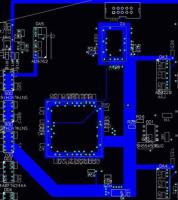

zvs опубликовал тема в Работаем с трассировкой

Вот есть у меня два варианта разводки, никак не могу склониться в пользу одного из них. Есит микросхема ПЛИС, к ней ППЗУ, буферы, АЦП. Все питается одним и тем-же напряжением I\O. Собственно вопрос: как лучше развести это питание? 1) накрыть все одним полигоном (Copper Pour): рис.1 2) провести к каждому отдельные линии (тем же самым Copper Pour токма потоньше) рис.2 Заранее спасибо. -

А что за микросхему применили? И каковы длины кабелей: от ЛПТ до буфера и от буфера до платы? Кстати, схема загрузки была не совсем стандартная - заказчик потребовал сделать циклону внешнюю перезагрузку и я не нашел ничего умнее :unsure: , чем решить этот вопрос внешним дерганьем за nCONFIG.

-

Понятно... Как видно случай тяжелый. Расскажу что было. На самом деле на EPC4 я совершенно напрасно качу бочку. Виноват был самодельный байтбластер, собранный по Альтеровской схеме, и на питание которого не повесили ни одного конденсатора. 0,1 мкФ по питанию спас "отца русской демократии". Ну, кстати симптомы были еще такие^ на другой платке (EPC2+FLEX10K) когда тыкал осциллографом на ногу "ТСК" - пзушка шилась, но верификацию проходить отказывалась, а без осцилла Q4 рассказывал что в упор не видит цепочки jtag.

-

PCI ядра

zvs ответил admin тема в Работаем с ПЛИС, области применения, выбор

А можно поподробнее по поводу ухищрений??? -

Есть кольцо JTAG: ByteBlasterMV - EPC4 - EP1C12 - ByteBlasterMV При программировании EPC4 все программится, но verify не проходит. При examine читается из EPC4 одно и то-же. Если сравнивать то что писалось и то что прочиталось - несовпадение данных наблюдается от записи к записи. Постоянным остается только то, что ошибка в последнем бите слова: было x01 стало x00 или было х41 стало [40/ Может, кто сталкивался, подскажите в чем проблема..

-

АЦП умирают стоя

zvs ответил zvs тема в Цифровые схемы, высокоскоростные ЦС

На самом деле абсолютно напрасно поднял панику. При ближайшем рассотрении оказалось, что все живы, кроме UARTа, который передавал данные с АЦП в ПК. Он тихо плюнул на последний бит и просто отказался его передавать на 921600... При снижении скорости передачи ему полегчало. Самое интересное, что до этого в течении месяца эту заразу все устраивало :( -

АЦП умирают стоя

zvs ответил zvs тема в Цифровые схемы, высокоскоростные ЦС

Значит так. Нога АЦП с ногой ПЛИС (куда собственно шина в выхода АЦП заводится) прозваниваются (Так что похоже нога не отвалилась). Сопротивление ноги относительно аналоговой земли точно-такое-же как и у соседних (Так что похоже на землю не нагрузил). Отогнуть ножку попробую. Только есть у меня подозрение, что я ей маленькую частоту дискретизации задал в своих отладочных целях. В датащите этого рекомендовали избегать. В понедельник расскажусь чем кончилось ;) -

АЦП умирают стоя

zvs опубликовал тема в Цифровые схемы, высокоскоростные ЦС

Есть АЦП AD9220 и что-то с ним не то - в выходной шине данных 9-й бит вечно в нуле, даже если 10-й, 11й и 12й реагируют на изменение входного синусоидального сигнала. Первое предположение - что он помер. Но может ли он умереть так.. частично? Может кто сталкивался с чем подобным - поделитесь, пожалуйста. -

2 разнотипные платы

zvs ответил Maestro тема в PS-Electro

Действительно, а почему не скажете? Мы блин вот у них (PS-electro) все время заказываем и ничего, довольны :) А вы хорошее место прячете. Нет бы тем людям клиентов добавить... -

А можно ссылочку на то что 200 МГц при температурах ниже нуля эта зараза все-таки захватит?