Вася0

Участник-

Постов

11 -

Зарегистрирован

-

Посещение

Весь контент Вася0

-

NIOS II Processor Booting Methods in MAX 10 Devices pdf страница 22 там написано как сгенерировать pof

-

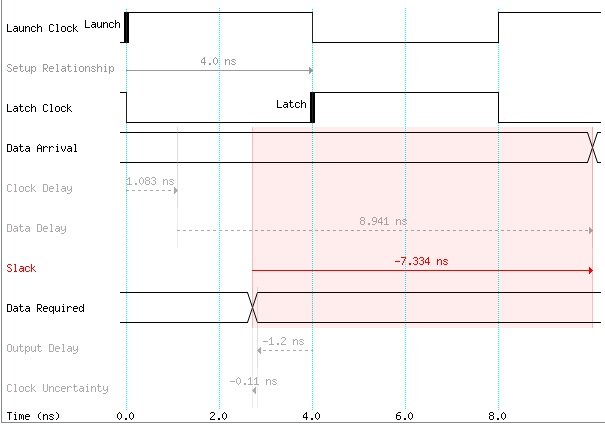

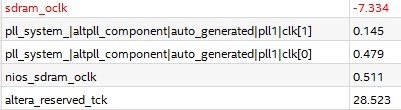

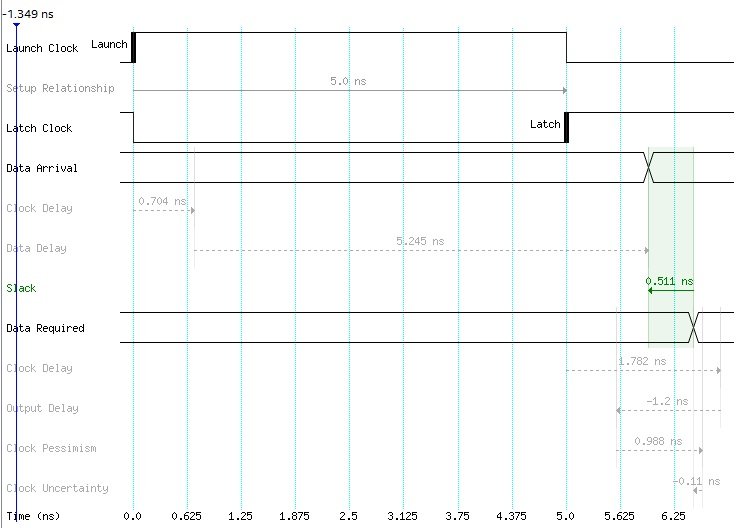

Здравствуйте, пишу свой первый проект на ПЛИС (verilog, max10), проект создаю в учебных целях. Создал систему в Qsys: nios, память(sdram), Jtag, и самописный компонент. Внутри самописного компонента, с просторов интернета контроллер памяти sdram(отдельно от памяти nios), счетчик и DCFIFO для передачи из счетчика на sdram. Nios запускает счетчик, тот в считает до оперделенного числа, и записывает в FIFO, оттуда контроллер sdram забирает данные и пишет в память. Nios и счетчик работают на 100Мгц, sdram и память на 125Мгц, FIFO двухклоковое на запись 100 Мгц на чтение 125 Мгц. На симуляции все работает отлично но в железе появляются проблемы констрейнов. В assigment поставил sdram выводам fast IO, клоки сделал Global Clock. Sdram для Nios работет timequest не ругается, а в моем компоненте постоянно ошибки памяти и я не могу понять почему такие большие слаки. Память микрон MT48LC16M16A2. На nios память микрон MT48LC4M32B2. Констрейны nios sdram Констрейны контроллера Общая картина: Клок Nios sdram Sdram внутри компонента. Не могу понять причину почему sdram внутри моего компонента так отличается от sdram используемого nios. Уже 2 недели бьюсь, может кто-то подскажет? Исходник компонента прилагаю. src.sv

-

Если dual image то в cfm 1 и 2 хранится pof, который вы генерируете совмещая 2 sof в quartus, по сути это 2 сжатых sof, но чем сжаты я не нашёл. Можно прочитать cfm и сравнить с pof. И самое главное в cfm байты перевернуты.

-

У фифо есть сброс это не выход? А если в хранить данные в 128битном регистре и через мультиплексор подавать на Авалон по byteenable в случае если адрес совпадает с предыдущим, какие минусы в таком подходе?

-

Здравствуйте, пытаюсь соединить мастера с шиной 32 бита и слейв с шириной 128, мастер только читает. Подключены через pipeline bridge, скажите можно ли так настроить bridge чтобы на 4 чтения мастера приходилось 1 чтение из слейва, в симуляции по 4 чтения в слэйве пока мастер всю шину пройдёт,неужели в width adapter нет никакого fifo который решает эту проблему?

-

Во всех примерах 100 MHz, наверное вы правы, пока оставлю как в примерах, спасибо за комментарии.

-

Просто в pdf Nios Benchmarks сказано max10 nios fmax 150 MHz. Я создаю простую систему пока только Ниос и память,но даже 140MHz не преодолеть.

-

Кэш данных отключил тк не нашёл как создать некешируемую область память для sgdma. Что такое ТСМ? Не подскажете по максимально скорости nios на 100МГц работает, а 167 нет, проект простой только Nios и onchipram.

-

Nios на частоте 167 МГц

Вася0 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Добрый вечер, сощдай простой проект на Max10. В qsys Nios на onchip mem и jtag, в главном файле pll 50->167. Отрицательные слаки внутри nios. Разве у Ниос есть предельная частота? И что за модели в timequest, в fast все нормально, а в других setup slack ~2.4. -

Здравствуйте, система на MAX10 с использованием Nios, на Nios рабтает FreeRTOS. Использую TCP/IP стек FreeRTOS. Nios на 50 MHz входной частоты давал скорость пеердачи по TCP 10 Мбит, с оптимизациями O2 (без них ~5-6). Увеличил частоту Nios до 100 MHz, скорость выросла до 12 Мбит(с оптимизациями). TSE и SGDMA работают на частоте Nios. Памяти много, 16MB sdram, 100MHz. Видел пример альтеры по ускорению Ethernet, система у них работает на 100 MHz, и без оптимизаций выдает скорость ~22 Мбита, а с оптимизациями от 50 до 80 МБит. Не могу понять где узкое место и почему увеличивая тактовую частоту в 2 раза такой маленький прирост. Может кто-то сталкивался или посоветует куда копать?

.jpeg.f7b1e179647bde5de7da37a1be73326c.jpeg)