-

Постов

126 -

Зарегистрирован

-

Посещение

Весь контент uzzzer

-

Малые токи (порядка E-9) в Multisim 14.3

uzzzer опубликовал тема в Вопросы аналоговой техники

Доброго дня, коллеги! Столкнулся в Мультисиме со следующим косяком (или я тупо чего то не понимаю): при измерение токов порядка 10-9 система врет причем значительно, а именно, там где 2 нА, амперметр показывает 3 нА (!!!), при этом, если измерять токи мА и мкА, то все в норме. Что это??? Design4.ms14 -

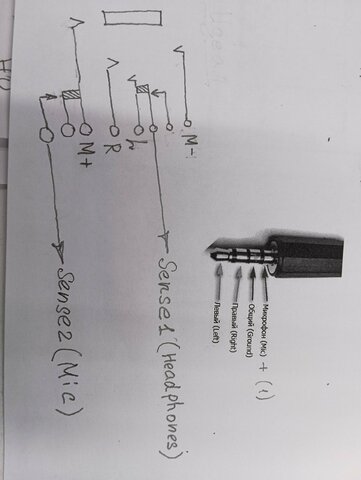

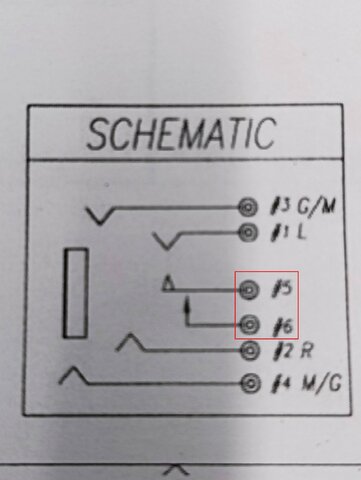

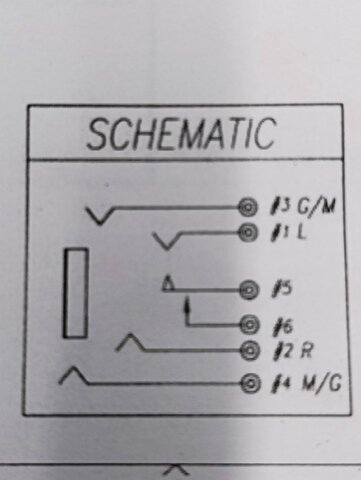

Спасибо большое! Кое чего прояснилось. Но я забыл уточнить, что и чем замыкается в комбинированном разъеме HD Audio? Я запутался именно в этих сенсорах. На разъеме, который я прикрепил, L(1) замыкает контакты (5) и (6) (SENSE). Вот примерно, что мне нужно:

-

Спасибо большое! Но к сожалению нужного разъема я не нашел((( Мне нужен разъем со схемой, которую я прикрепил: С выводами 5 и 6 (обведены красным).

-

Помогите найти комбинированный разъем (Mic+R+L)

uzzzer опубликовал тема в Вопросы аналоговой техники

Доброго Вечера, коллеги! Помогите найти комбинированный разъем, которые обычно устанавливаются в материнских платах ноутбуков, планшетов, смартфонов и т.д. Схему разъема и фото штекера прилагаю. Нужен точный партнамбер. -

Многоканальный проект

uzzzer ответил uzzzer тема в Altium Designer, DXP, Protel

Все. Спасибо. Разобрался сам. Короче в метке цепи HPS_DDR3_ADDR[0...14], была допущена опечатка: вместо "0..14" написал "0...14". Тупо моя не внимательность. -

Многоканальный проект

uzzzer ответил uzzzer тема в Altium Designer, DXP, Protel

Нет. У меня изначально слишком много повторяющихся кусков схемы. Проект изначально иерархический. Можно сделать с помощью портов по одному сигналу(тут все нормально именуется), но слишком громоздко. Просто интересен вопрос еще почему шина на топе в приоритете, а локальные сигналы не именуются в соответствии с ней? Пробовал Flat, но все тоже самое... -

Многоканальный проект

uzzzer ответил uzzzer тема в Altium Designer, DXP, Protel

ФГ - функциональная группа. А "по человечески" это как например? -

Многоканальный проект

uzzzer опубликовал тема в Altium Designer, DXP, Protel

Добрый день, коллеги! У меня схема, состоит из двух ФГ. Канал DDR3(А1) и канал с ПЛИС (куда я подключаю память, А2). Локальные имена цепей, объединенных в шину, А1: DDR3_ADDR0,DDR3_ADDR1...DDR3_ADDR14 и в А2: HPS_DDR3_ADDR0,HPS_DDR3_ADDR1...HPS_DDR3_ADDR14. Соединяю ФГ шиной DDR3_ADDR[0...14] и получаю ошибку в А2 "Net HPS_DDR3_ADDR0 has only one pin". Иными словами А2 игнорирует соединение двух ФГ. Хотя порту в А2 все таки присваивается имя соединяющей А1 и А2 шины... Настройки проекта у меня такие: -

2018 Вопросы начинающих

uzzzer ответил Sanchosd тема в Altium Designer, DXP, Protel

Вот я и имел в виду как написать скрипт. С помощью какой функции можно создать сетку в редакторе PCBLib? -

2018 Вопросы начинающих

uzzzer ответил Sanchosd тема в Altium Designer, DXP, Protel

А как в редакторе корпусов (PCBLib) добавить новую сетку с помощью скрипта? И как с помощью скрипта поменять в библиотеке схематик путь к библиотеке PCBLib(для всех компонентов)? -

А ссылочки не осталось на проект по переводу контроллера VIC068A?

-

Ну Слава Богу ! Все заработало:) После вашего совета: Прошла полная компиляция. Сгенерились две корки: \PCIe2VME\16z091-01_src\Source\x1\Hard_IP_x1.qip и \PCIe2VME\16z091-01_src\Source\x4\Hard_IP_x4.qip и бинарники PCIe2VME\Synthesis\fpga_files\16A025-00_03_15.bin с PCIe2VME\Synthesis\fpga_files\16A025-00_03_15.hex Спасибо вам большее ! Вот к стати страница с этим проектом: https://ohwr.org/project/pcie-vme-bridge/wikis/home

-

У меня Quartus 15.1, не могу найти каталог /intelFPGA/16.0/ip/altera

-

Попробовал вот что вышло:

-

Ну это я уже догадался:))) Вот, что за PCIe2VME\16z091-01_src\Source\x4\Hard_IP_x4.vhd и почему, там может все быть закоментино?

-

Если закоментить строки в gen_ip_cores.tcl: #source ../16z091-01_src/Source/x4/x4.tcl #source ../16z091-01_src/Source/x1/x1.tcl То, компиляция стартует, но потом все равно вылетает с той же ошибкой. Но qip в \PCIe2VME\Synthesis нет. Если все оставить как есть, то компиляция глохнет на:

-

А как это сделать? Извиняюсь, может глупый вопрос... Вот еще, собственно и код на который ругается Квартус: Немного напрягает конструкция для компонента: Разве так можно определять компонент?

-

Quartus: Проблема с компиляцией "work".

uzzzer опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый вечер ! Помогите, пожалуйста с компиляцией проекта, компилятор ругается: Удалил из проекта все файлы, добавил заново, но ошибка повторяется. Согласно readme все должно работать. файл проекта: \PCIe2VME\Synthesis\A25_top.qpf PCIe2VME.zip -

VME64x(Помогите с реализацией)

uzzzer ответил uzzzer тема в Форумы по интерфейсам

Контроллер есть, нужно сделать его реверс. Покупать, опять, заказчик не хочет, начальство упирается, что, своих денег нет и что "закладки там могут быть, нужно свое делать". Проблема еще и в том, что платы залачены и на микросхемах наклейки наклеены. -

VME64x(Помогите с реализацией)

uzzzer ответил uzzzer тема в Форумы по интерфейсам

Вот именно, что древние, и снятые с производства уже давно. Сейчас VPX активно продвигается и что VME пока помирать не собирается никого не касается, бизнес, и ничего личного. Да, я находил описания этих микросхем и еще были VIC068A-GC, но они тоже сняты с производства, есть в стоках, но думаю искать бессмысленно. Я пытался обращать за помощью, но либо требовали деньги, на что заказчик ответил отказом, либо никто ничего не помнит. В общем те, кто что то знает, держат это при себе. Правда, конечно кое чего за эти два дня я прояснил, благодаря примерам, но этого не достаточно, так как слишком большой объем информации. Да собственно у меня задача стоит в сопряжении GPIO ARM с VME, если у кого есть что то подобное, то буду рад информации, вообще буду рад любой информации, так как сейчас нахожусь тупо в ступоре. -

VME64x(Помогите с реализацией)

uzzzer ответил uzzzer тема в Форумы по интерфейсам

Процессор со встроенным контроллером VME? А линейка какая? О существовании VME, можно так сказать узнал месяц назад, а с мотороловскими процессорами не имел дело вообще. В литературе по VME говорится всю дорогу о 68000, но это как я понимаю слишком уж древний. Современные есть ? А то гуглю все поиск выдает мне процессорные модули на моторолловских процессорах. И прошу простить мне такие глупые вопросы, я действительно первый раз с этим сталкиваюсь. -

VME64x(Помогите с реализацией)

uzzzer ответил uzzzer тема в Форумы по интерфейсам

Хотелось бы конкретную реализацию с ARM (SM32 как пример),та система, что у меня есть, как раз на STM32F3.Сама логика Master реализована на ПЛИС, так, что полный реверс не получается. Мне бы конкретный пример для Master, Arbiter и Slave. Просто посмотреть как люди это делают:) UPD: А это серьезный проект, большее спасибо! -

VME64x(Помогите с реализацией)

uzzzer ответил uzzzer тема в Форумы по интерфейсам

Спасибо большее ! Но это все равно немного не то:(