squli

Участник-

Постов

18 -

Зарегистрирован

-

Посещение

Весь контент squli

-

Ошибка при измерениях АЦП

squli ответил squli тема в Вопросы аналоговой техники

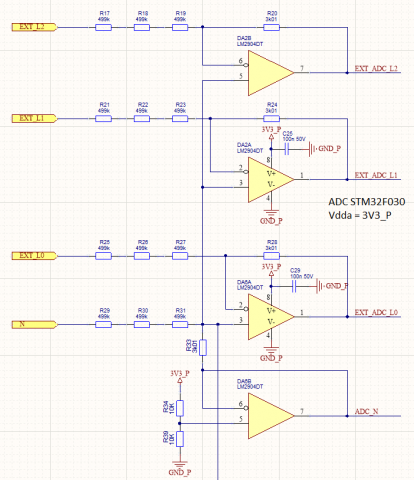

Благодарю за помощь! Нижний провод идет на такой же сдвоенный операционник как и сверху, там ещё два входа линий. У мультиметра предел стоит максимальный - 750В, выше никак. На каждый вход ставить варистор выходит накладно, может быть есть какие-нибудь ещё варианты? Накаливания пока не нашёл, ищу. Подключил светодиодную, светит, греется, но измерять стало сильно хуже. Я заметил, что верхний полупериод синуса после оцифровки имеет обрезанный верх и использую только нижний полупериод, полагая, что всё симметрично. Не может ли в этом быть проблемы? Правильно ли я понимаю, что ОУ должен был быть rail-to-rail? Вторую часть не понял. Входное - это 230 В со щитка через диммеры, нейтраль у них общая и идёт напрямую со щитка. Проблема в том, что на ней могут быть 1500В? Резисторы стоят 1206, от остального стоит развязка в уарте, по которому передаются измеренные значения. Это не счетчик, мне бы только проверить, что измерения не врут больше чем на 5-10% с диммером надо измерять тоже на отсечке пол полупериода. - можно ли чуть подробнее? спасибо! -

Ошибка при измерениях АЦП

squli опубликовал тема в Вопросы аналоговой техники

Добрый день! Есть вот такая схема для измерения переменного напряжения 180-250 В. Цепи EXT_ADC_LX и ADC_N идут на АЦП STM32F030 c Vdda = 3V3_P. Я считаю RMS значение. Пока напряжение для теста беру прямо из розетки - всё ок, показания агилентовского мультиметра совпадают с рассчитанными. А вот когда начинаю диммером уменьшать напряжение - значения с АПЦ примерно на 20В выше, чем измеренные мультиметром при отключении платы. При этом стоит подключить мультиметр ко входу платы - значения, рассчитанные с АЦП становятся теми же, что и на мультиметре. Вроде бы не похоже на ошибку в программе, скорее параллельно подключенный мультиметр меняет входное сопротивление платы и она перестаёт врать? В документации на мультиметр сказано, что входное сопротивление у него 1МОм. Я пробовал просто допаять резистор между линией и нейтралью - не помогает. Подскажите пожалуйста есть ли в схеме ошибка? В прошивке вроде бы нет ошибок, а измеряет всё равно не правильно. Благодарю -

Документы ТП в ОКР

squli ответил squli тема в Документация

добрый вечер, спасибо! все уже близится к завершению, перечнь уже согласован, подписан. если кому-нибудь будет полезно :) таблица в моем посте нормальная, код документа только нужно добавить, очень помогает пока не выучишь. столбец с порядковыми номерами записей в таблице противоречит ГОСТ 2.105-95, никто даже читать не будет. изделие в целом состоит из блоков, блоки состоят из узлов, а узлы из деталей. Кто к чему относится действительно следует из схемы деления, вместо "прибора" у меня "блок". ГОСТ 2.902-2005 сейчас действует, а не -68, я его нашел, он снимает кучу вопросов, в нем есть список требований по которым ПЗ будет проверять разработанную РКД, и следовательно, список еще кучи бумаг, которые нужно будет оформить в дополнение к перечню. еще раз, большое спасибо за помощь! -

Документы ТП в ОКР

squli ответил squli тема в Документация

Добрый вечер! да вопрос был как оформить, но вроде разобрался, хотя за пример буду очень признателен. шапка у перечня вроде такая, но вот откуда брать как моё изделие делится на узлы и блоки я не понимаю, это из схемы деления должно следовать или откуда? спасибо! -

Документы ТП в ОКР

squli опубликовал тема в Документация

Добрый день, надо сделать документы технического проекта, в ведомости исполнения помимо прочих есть следующий - "перечень (комплектность) конструкторской документации на изделие" про него в по ГОСТ РВ 15.203-2001 сказано следующее: ГОСТ РВ 2.902 у меня есть только 68 года, из него как выглядит этот перечень мне до конца не ясно. Мое понимание такое: По ГОСТ 2.102 я пишу список всех документов которые мне необходимо разработать - всех спцефикаций, чертежей, паспортов и т.д. называю его номенклатурой и прикладываю к перечню. Потом делаю сам перечень, типа такого: спецификация - разрабатывается, не согласуется ... схема деления - разрабатывается, согласуется с ПЗ на этапе ТП программа обеспечения надежности - разрабатывается, согласуется с ПЗ на этапе ТП ... руководство эксплуатации - разрабатывается, согласуется с ПЗ на этапе изготовления ОО и т.д. т.е. перечисляю типы документов и согласует их или нет, и когда, если согласуют. в конце этапа РКД по номенклатуре буду предъявлять ПЗ документы, он будет по перечню смотреть, что он согласует, что просто наличествует. кто делал такие вещи, подскажите плз. Спасибо! -

Добрый вечер! Имеется желание разобраться с ethernet в STM32F107. Сделана плата по схеме на картинке: http://smotr.im/7Ukj К плате взят пример LwIP в нем исправлены только части, касающиеся распиновки MII интерфейса, закомменчен LCD, сделан вывод дебажных сообщений по SWO, убран DHCP и включен вывод отладочных сообщений. резет RTL к единице, пробовал в конец ETH_Init дописывать ETH_Start, не помогает, вроде бы все. Подключаю плату к компу, комп видит непонятную сеть, скорость определяет, пинга нет. На разъеме езернета на плате горит линк, мигает нужный (100 или 10). айди ртл считывается верно, в регистрах (нулевом и первом) все как и планировалось, только в регистре, считающем принятые пакеты - 0. В STM не попадаю в функцию разбора принятого пакета вообще. На RX и ТX клоки по 25 МГц, на MDIO вроде данные, когда конфигурируется ртлка. разъем с трансформатором проверил со всех сторон вроде. питание от усб. в настройках компа статический айпи и маска, ничего больше. вайршекер видит только пакеты от компа. все многочисленные темы с RTL8201BL и не только, прочитаны не по разу уже. :)) в примере: http://www.st.com/internet/com/SOFTWARE_RE...WARE/an3102.zip должна ли пинговаться плата? да и в общем, как завтавить все это работать? спасибо!

-

не подключается к проекту STM32_ETH_Driver

squli ответил squli тема в ARM, 32bit

неа, не помогает. в настройках убирал галку browse information, окно с ошибкой не появляется, но в stm32_eth.c по прежнему не работают #include "stm32_eth.h" и др., хотя пути к папкам с ними правильные. с остальными драйверами все нормально, только с stm32_eth что-то не то :( -

не подключается к проекту STM32_ETH_Driver

squli опубликовал тема в ARM, 32bit

хочу подключить к проекту драйвер ethernet (stm32_eth.c и stm32_eth.h) (стандартной переферии нормально подключил) добавляю в проект файл .с, дописываю в настройках папку, где файл .h при сборке проекта все время ошибка, скриншот внизу. пробовал пересоздать проект с нуля, все тоже, пробовал переименовать файлы, убрал только чтение... дописывал .с в другой файл, тогда окна с ошибкой нет, но все равно .h не подключаются, хотя пути в настройках к ним нормальные. не понимаю в чем причина :05: спасибо! -

STM32F107RBT6 попадает в бесконечный цикл,

squli ответил squli тема в ARM, 32bit

BOOT0 через резистор на землю помогло, не думал, что она по умолчанию в высоком уровне. всем спасибо! -

STM32F107RBT6 попадает в бесконечный цикл,

squli ответил squli тема в ARM, 32bit

нога BOOT0 никуда не подключена, на ней меряется 0.9-1 В. (Standard IO input low level voltage maximum: 0.28*(VDD-2 V)+0.8 V = 1.16) если перепрошивки по уарту не планируются его её можно через резистор на землю? -

STM32F107RBT6 попадает в бесконечный цикл,

squli опубликовал тема в ARM, 32bit

Добрый вечер, суть проблемы - свежеспаяная плата со свежим контроллером один раз прошилась, помигала светодиодом, и дальше шиться отказывается. На плату допаял 2 последовательных резистора в дифпару USB (до этого USB не был подключен). сейчас отпаял обратно. jlink - keil, в деассемблере ходит по кругу около адреса 0x1FFFE23E, я особо не знаток, но ассемблерные команды выглядят несколько бессвязно. 0x1FFFE1E4 69A8 LDR r0,[r5,#0x18] 0x1FFFE1E6 2801 CMP r0,#0x01 0x1FFFE1E8 D124 BNE 0x1FFFE234 0x1FFFE1EA F8D80008 LDR r0,[r8,#0x08] 0x1FFFE1EE F0100F40 TST r0,#0x40 0x1FFFE1F2 D01F BEQ 0x1FFFE234 0x1FFFE1F4 2005 MOVS r0,#0x05 0x1FFFE1F6 6020 STR r0,[r4,#0x00] 0x1FFFE1F8 F8CDB000 STR r11,[sp,#0x00] 0x1FFFE1FC E002 B 0x1FFFE204 0x1FFFE1FE 9800 LDR r0,[sp,#0x00] 0x1FFFE200 1E40 SUBS r0,r0,#1 0x1FFFE202 9000 STR r0,[sp,#0x00] 0x1FFFE204 F8D80008 LDR r0,[r8,#0x08] 0x1FFFE208 F0100F40 TST r0,#0x40 0x1FFFE20C D002 BEQ 0x1FFFE214 0x1FFFE20E 9800 LDR r0,[sp,#0x00] 0x1FFFE210 2800 CMP r0,#0x00 0x1FFFE212 D1F4 BNE 0x1FFFE1FE 0x1FFFE214 9800 LDR r0,[sp,#0x00] 0x1FFFE216 B138 CBZ r0,0x1FFFE228 0x1FFFE218 6928 LDR r0,[r5,#0x10] 0x1FFFE21A B928 CBNZ r0,0x1FFFE228 0x1FFFE21C 68A0 LDR r0,[r4,#0x08] 0x1FFFE21E F5C02000 RSB r0,r0,#0x80000 0x1FFFE222 60E8 STR r0,[r5,#0x0C] 0x1FFFE224 6868 LDR r0,[r5,#0x04] 0x1FFFE226 E7C4 B 0x1FFFE1B2 0x1FFFE228 2000 MOVS r0,#0x00 0x1FFFE22A 61A8 STR r0,[r5,#0x18] 0x1FFFE22C 6020 STR r0,[r4,#0x00] 0x1FFFE22E 60A0 STR r0,[r4,#0x08] 0x1FFFE230 F8C4A004 STR r10,[r4,#0x04] 0x1FFFE234 69E8 LDR r0,[r5,#0x1C] 0x1FFFE236 2801 CMP r0,#0x01 0x1FFFE238 D106 BNE 0x1FFFE248 0x1FFFE23A F8D90000 LDR r0,[r9,#0x00] 0x1FFFE23E F0100F20 TST r0,#0x20 0x1FFFE242 D001 BEQ 0x1FFFE248 0x1FFFE244 2002 MOVS r0,#0x02 кто виноват, что делать? спасибо! -

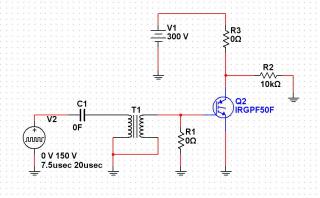

Добрый вечер, Есть схема: на входе импульсы большой амлитуды (пусть 100В, хочется понять принцип), 50кГц, питание 400 В на выходе хочется импульсы ~400В. Как рассчитать трансформатор и прочее? в даташите дан заряд затвора, нужно посчитать Ig(min) = Qg * f. потом посчитать Ig(max) = dU / Rg. dU от -15 В до 15, чтобы побыстрее включался-выключался. Rg = R1, так? Дальше считать для Ig среднего какого-то? или брать Ig(max?) Зная Ug, Uвходное найти число витков. Из Ig = Vmax / (2*pi*f*L2), найти L2. Зная число витков и Ig найти ток в первой обмотке и её идуктивность? конденсатор для ненасыщения трансформатора? его считать, чтобы на 50кГц был резонанс? потом выбирать феррит, тип намотки и марку проволоки? я только учусь, первый десяток выдачи гугла уже прочитал, где-то что-то не понимаю. Спасибо.

-

вобщем, я так понял: если нужно сделать: полноценный сборочный чертеж, я делаю в альтиуме brd файл, его передаю в солид, но на сгенеренном чертеже нету позиционных обозначений, для них потом, для пробы, слой шелкографии сохраняю в dxf и вставляю в солидовскую модель, так? ничего пока не поулчается. да и шелкография не совсем то, что нужно. пока вижу так: мех. слой в библиотеке - "=designator" с галкой про конверт спешл стринг, этот слой и переностить через dxf на модель, другой. мех слой - контур компонента третий - контур для 3-х мерной отрисовки. мoжно ли как-нибудь проще? модель платы с компонентами для конструктора тогда нужно сохранять как степ-модель (в брд разъемы из красивых желтеньких становятся серыми прямоугольниками) и все? модельку для презентаций, чтобы все было красиво - сдлеать степ, потом через принтскрин из 3d альтиума перенести и копать про PhotoWorks-надписи? там будет и шелкография и дорожки и виасы все и т.д.? в чем фича экспорта в egis? хотел посмотреть, да все виснет намертво. спасибо!

-

для шага 1мм я поступил следущим образом: 1. сквозные отверстия выводились от центра по диагоналям в разные стороны, поэтому остался крестообразный промежуток 2. от двух соседних падов земли и питания делалось одно переходное отверстие 3. места получилось вполне достаточно. все работает, нареканий нет. и вопрос: при минимуме свободного места, можно ли ставить емкости вокруг БГА друг над другом, чтобы два кондесатора подключались через одно переходное отверстие?

-

Как в Altium сделать...

squli ответил Uladzimir тема в Altium Designer, DXP, Protel

добрый вечер, есть библиотека уго, в которую собрана куча компоентов с разным шагом выводов и их длиной (часть в метрической, часть в дюймовой). Из-за этого нарисовать нормальную схему не получается, можно ли где-нибудь глобально изменить настройки библиотеки? хочется, чтобы как при импорте - задать расстояние между выводами и оно во всей библиотеке будет одинаковым. спасибо. -

Altium для новых начинающих

squli ответил Uladzimir тема в Altium Designer, DXP, Protel

" 2 раздел правил Plane/polygon connect style Для Via указать Direct connect " а как? напишите плз. строку querry, которая описывает переходные отверстия. и если не сложно, пару строк как управлять типами переходных отверстий. т.е. в оркаде было via1, via2, ... и каждому задаешь параметры какие нужны, какой тип используется по умолчанию и т.д. а в альтиуме это никак не могу реализовать. спасибо! -

Altium для новых начинающих

squli ответил Uladzimir тема в Altium Designer, DXP, Protel

добрый вечер, есть 2 вопроса по АД: 1. Какой в Альтиуме аналог z-index для полигонов, т.е. хочу нарисовать один полигон, поверх него другой, еще поверх третий и задать кто выше, кто ниже. не понимаю как. 2. Как убрать термобарьер у переходных отверстий. спасибо -

добрый день, название корявое получилось, извините. orcad 16.2 суть дела: есть схема из 5 блоков (микросхема-обвес), есть готовая плата. стоит задача заменить один/несколько блоков. естественно с нуля все делать не хочется. есть ли возможность как-то ассоциировать части схемы в кэптче с частями готовой платы в лэйауте? чтобы удалить один блок из кэпчи, нарисовать там другой, и его компоненты добавились к старому макс-файлу. заранее спасибо. надеюсь внятно изложил.