sybirman

Участник*-

Постов

26 -

Зарегистрирован

-

Посещение

Весь контент sybirman

-

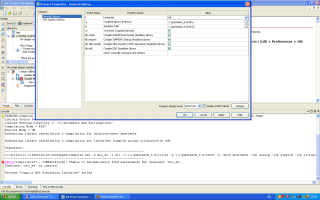

приветствую. решил снести ISE 10.1 и установить 11.3. Установил ISE 11.3 и QuestaSim 6.5. Таблетками их вылечил. Далее решил скомпилировать библиотеки хилых для квесты. Делал все как для 10.1. При попытке скомпилировать - получил ошибку. Скриншот прикреплен. Я не понимаю что он от меня хочет, вроде бы все пути прописаны правильно. Помогите разобраться. проблему решил. снес нахрен квесту и поставил моделсим 6.5. в данный момент идет компиляции и пока что ошибок нет. кстати в свойствах проекта (там где надо выбрать используемый симулятор), нету квесты, есть только моделсим и другие. получается что для квести в принципе нельзя скомпилить библиотеки для 11.3 версии ISE?

-

Как найти сопростивление

sybirman опубликовал тема в В помощь начинающему

Решаю задачки. Столкнулся вот с такой. Как найти полное сопротивление: Вот если бы не было R4, то тут все легко: Rtotal = R2 + [ R1 || (R3 + R5) ] все портит R4. Дайте, пожалуйста, подсказку как вычислить .... resistor.bmp -

ищу книгу

sybirman опубликовал тема в Образование в области электроники

http://www.amazon.com/exec/obidos/tg/detai...ER&v=glance Есть ли на форуме обладатели электронной версии данной книги? Прошу поделиться, если не жалко :) -

тех процесс

sybirman опубликовал тема в В помощь начинающему

Что имеется ввиду, когда говорят технолог. процесс 90 нм, 180 нм, 45 нано? это размер какого-нибудь стандартного элемента И или ИЛИ? -спасибо -

3 вопроса

sybirman опубликовал тема в Языки проектирования на ПЛИС (FPGA)

специалисты, поделитесь знаниями плиз ... 1) какие пути решения проблемы в 4м вопросе вообще существуют? 4 вопрос 2) тот же сайт, но вопрос 8. делитель на 5. module dv5 ( clk, rst, dv5 ); input clk; input rst; output dv5; reg [2:0] q; wire b; reg b_d1; always @(posedge clk or posedge rst) begin if (rst) q <= 3'b000; else if (q[2]) q <= 3'b000; else q <= q + 1; end assign b = ~|q[2:1]; always @(negedge clk or posedge rst) begin if (rst) b_d1 <= 1'b0; else b_d1 <= b; end assign dv5 = b | b_d1; endmodule сделал, работает. есть ли способ более простой? 3) 12 вопрос. буфер - нужен для задержки. а для чего обратная связь? -thanks -

Стивен Кочан

sybirman опубликовал тема в Программирование

Друзья, есть ли в природе электронная версия книги (бесплатная, на англ желательно)? Уж, очень не хочется покупать. Programming in C by Kochan, Stephen -

прошивка фпга

sybirman опубликовал тема в Работаем с ПЛИС, области применения, выбор

1) подскажите, почему после выключения питания, прошивка в фпга слетает? 2) и как сделать так, чтобы прошивка оставалась там (пока я сам не захочу ее сменить) ? и еще один вопросик. У кого есть данный кит - поясните, плиз, смысл этой таблицы - Table 4-1: Spartan-3E Configuration Mode Jumper Settings (Header J30 in Figure 4-2), я не понимаю. -спасибо -

Продаю Xilinx Parallel Cable IV (купил 1.5 года назад в www.xilinx.ru , ни разу не использовал) http://www.plis.ru/page.php?id=106 Санкт-Петербург

-

а я даже и не изучал документ документ, просто открыл, смотрю команды есть, все в цвете. вот решил и поделиться :)

-

OVM обновился

sybirman ответил des00 тема в Методы и средства верификации ПЛИС/ASIC

заказал книгу на амазоне, как прийдет , постараюсь отсканить и поделиться , если конечно кто-нибудь не опередит меня :) -

OVM обновился

sybirman ответил des00 тема в Методы и средства верификации ПЛИС/ASIC

я был на этом сайте www.ovmworld.com вот как раз по ссылке OVM Book открывается страница с книгой Step-by-Step Functional Verification with SystemVerilog and OVM а документы пдф из ovm-2.0.zip по содержанию, не соответвуют содержанию книги, поэтому и попросил поделиться ... -

OVM обновился

sybirman ответил des00 тема в Методы и средства верификации ПЛИС/ASIC

“Step-by-Step Functional Verification with SystemVerilog and OVM” если кто-нибудь встречал в электр виде, поделитесь плиз -

uart rx

sybirman ответил sybirman тема в Языки проектирования на ПЛИС (FPGA)

разобрался. идею понял. спасибо в этом примере, по-сути старт условие else if (!rxd1 && rxd2) clk1x_enable <= 1'b1; это и есть задний фронт на rxd, потом начинается анализ принятых битов no_bits_rcvd. я примерно так же и хотел сделаьть -

uart rx

sybirman опубликовал тема в Языки проектирования на ПЛИС (FPGA)

есть UART Tx с конфигурацией ( 1 start bit, 8 data bits, parity bit, 1 stop bit, 9600 baudrate) на AT91SAM7S64 хочу сделать аппартный уарт приемник для данного прд на 3м спартане как и что делать понятно, кроме опредления старт бита. нужен совет. кроме перепада ( 1 --> 0 ) на RxD, хочу добавить условие, что до этого было принято 11 бит (start+8data+parity+stop), т.е. assign start = (~rdx_2d & rxd_3d) & (capture_ct == 11); корректно ли это? (все это исключительно для самообразования) -

CPSR

sybirman ответил sybirman тема в В помощь начинающему

т.е. этот постфикс указыват, на какие биты возможно воздействие? -

CPSR

sybirman опубликовал тема в В помощь начинающему

продолжаю разбираться, с арм ассемблерром. появились пара вопросов: почему не используют CPSR, а например CPSR_c вот здесь: ; Enter Abort Mode and set its Stack Pointer MSR CPSR_c, #Mode_ABT:OR:I_Bit:OR:F_Bit MOV SP, R0 SUB R0, R0, #ABT_Stack_Size нашел ответ на ....arm.com т.е. NZCV гарантированно не будут изменены? а, например, CPSR_f в каком случае используектся? -

что-то я совсем запутался. если происходит запрет irq, то как же тогда происходит выполнение; __irq void IRQ_Handler (void) { IO0CLR=1<<10; T0TCR = 1; EXTINT=2; VICVectAddr=0; }; это кусок кода из архива в первом посте. P.S. если нужно, то можно перенести тему в раздел для новичков, а то неудобно как-то, такие вопросы задавать в этом разделе :)

-

скажите, а в каком месте в стартапе (архив в начале темы) происходит разрешение IRQ прерывания? код из стартапa: I_Bit EQU 0x80 ; when I bit is set, IRQ is disabled ; Enter IRQ Mode and set its Stack Pointer MSR CPSR_c, #Mode_IRQ:OR:I_Bit:OR:F_Bit правильно ли я понял, что в предыдущей строчке, происходит установка режима IRQ и битов I & F. если да, то получается что прерывания запрещены ? (вот здесь я скорее всего ошибаюсь) поясните, пожалуйста. и еще вопрос, есть ли различие в фунциональности у предыдущей команды и следующими? MRS r0, cpsr ORR r0, r0, #I_Bit:OR:F_Bit;disable IRQ and FIQ interrupts MSR cpsr_c, r0 11111111 для чего нужны 2 верхние команды, если можно было как в стартапе - сделать одной? MSR CPSR_c, #Mode_IRQ:OR:I_Bit:OR:F_Bit