-

Постов

23 -

Зарегистрирован

-

Посещение

Весь контент labfab

-

разработка плат/платы

labfab ответил labfab тема в Предлагаю работу

немного переформулирую , видимо меня не со всем поняли) речь идет о схеме аналогичной усилителю SKHI 71 для Sixpack IGBT -

разработка плат/платы

labfab опубликовал тема в Предлагаю работу

Доброго времени суток г. Санкт-Петербург, но по большому счет это не важно. Ищу исполнителя пока лишь на разовый заказ. Есть схема IGBT усилитела , разработана мной, как замена IGBT усилителя от Semikron В деталях: - соблюсти UL нормы, понимание этих норм, 440V, макс. возможное напряжение DC Link 850V, без заливки - схема на базе Cadence OrCAD 16.6 - разводка также должна быть на базе Cadennce PCB Editor 16.6 - возможное решение - две платы с двухсторонней разводкой - основные компоненты не подлежат пересмотру, так как имеются в налиции в больших обьёмах, такие как оптроны и трансформаторы От вас жду: - по возможности улучшеную схему, предложения - разводку печатной платы, чтобы ее можно было отдать в производство - список элементов, техническая документация Предложения и вопросы на почту faber точка gbr собака gmail com Спасибо. -

Вопрос о НОВЫХ закромах

labfab ответил LeonY тема в FTP-серверы

есть возможность войти, или уже отключили я пробывал, но не смог к сожалению войти -

Среда разработки для XC886

labfab опубликовал тема в Все остальные микроконтроллеры

Уважаемые Форумчане мне в ближайшем времени предстоит написать небольшую программку для XC886. Вот хотелось бы спросить знающих, где бы мне раздобыть компилятор и отладчика, к примеру кейл. Имею также DAP miniWiggler JTAG, думал отлаживать через него. можно было также и под Codeblocks писать, только где бы вот раздобыть тот же нормальный gnu/gcc компилятор и как по шустрому правильнопоставить. )) Думал начать с ексампла и там двигаться дальше. Программка в принципе простая: просто принимает протоколы и пишет через на узлы. Сейчас просто проблема, где бы мне раздобыть соответствующую среду разработки. )) Помогите пожалуйста, если есть возможность. -

а как тут редактируются посты ?! я проблему решил уже, добавил просто на соответственные Footprints еще один слой. что то так и не на шел под это дело подходящий слой :angry2: взял первый попавшийся слой No_Probe_Top и нарисовал там по центру Glue Dots :rolleyes: и потом просто вывел как отдельный слой GLUE_BOT_LAYER и отправил, производитель доволен и от меня отстал. :twak: возможно есть какое другое решение этой проблемы, более элегантное, к примеру там через скрипт. :krapula:

-

Добрый день, А не подскажите, как можно из Layout PCB Designer вытащить метки под клей, для к примеру Bottom Layer. Ну вроде Glue Dots кличут. :-) У меня на нижней стороне платы, только птичий корм. Так производитель желает его приклеить и все за раз поджарить :-) Экономщики. Насколько я знаю в Eagle есть для этого Glue Bottom Layer. Мой производитель ленится и просит меня прислать ему, эти координаты / метки. Вот я и думаю, как бы мне это культурно организовать. Надеюсь что кто либо, тоже сталкивался с такой бедой. :-) А я почему то раньше думал, что их из Placed Component Report берут.

-

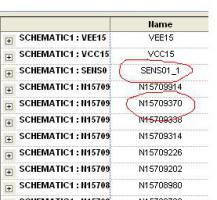

Привет форумчане )) еще вопросик, почему не получается заменить имя wire/net с помощью capture editor properties имя редактируется но не перенимается (( думаю через мож через .UPD файл попробывать )) в таком формате )) "{Net Name}" "Net Name" ... oldName newName через Net Alias , Name меняется но во первых на схеме высвечивается что не хотелось бы )) а во вторых хотелось бы автоматизировать весь этот процесс, так как в excel удобнее редактировать (macro можно запустить и т.д.) )) сейчас у меня Net Names в таком формате N123456 хотелось бы например SCHEMATICBLOCK_NETNUMBER ))

-

все надоело )) отредактировал с помощью modify lib а через заменил имя pad a ))))) ))))) СПАСИБО )) точно, во я гоню, пора в выходной, а то так и перегрется можно )))

-

Добрый день спасибо за совет, работает только для этого пришлось поменять лицензию на orcad capture 16.5 с allegro design, с allegro не шло (( видимо лиц. сервер гонит )) но есть проблемка и другая не могу редактировать .dra symbols хотел сделать padstack -> replase жму pad в ожидании что откроется окошечко с pads, но программа вылетает с ошибкой )) и пишет allegro_P00316.5_AllegroMiniDump.dmp и apd_P00316.5_AllegroMiniDump.dmp кто нитбудь тут padstack -> replase делал. нет, не всегда вылетает иногда пишет E- Symbol and Pin must be '*' when replace = old. help посмотрел )) Tools - Padstack - Replace Options Tab for the replace padstack Command Old Padstack Identifies the padstack that is to be replaced. New Padstack Identifies the name of the new padstack. If this padstack does not already exist in the design, it is loaded. Choose your padstack library. и как же это сделать? )) в командной строке не работает (( пишу replace padstack окошко не открывается (( а вот refresh padstack работает )) думал обхитрить софт )) загрузил .dra в .brd и заменил там pads и потом сделал extrakt symbols но.. symbol перенимает старые pads (((((=

-

Уважаемые коллеги )) до недавнего времени я работал с orcad 15.7 Ну вот тут решил перейти на allegro spb16.5 )) незнаю не пожалею ли )) Программу установил, вроде бы все удачно, но у меня проблема в том что между design cis и pcb editor нету связи. В версии до етого если я выбирал какой либо part в layout то в схеме capture выделялся, а сейчас нет (( И вообще через какой механизм происходит передача данных между design cis и pcb editor я редко делаю платы, но нет нет приходится хотелось бы понять что и как ))

-

не помню о предупреждениях - :wassat: На всякий отмечаюсь. :laughing:

-

Дорогие Пользователи, :smile3046: У меня возникла также проблема. Я имею только Allegro PCB Router 6U 210 лицензию Необходимы бы лицензии: SPTADV Allegro PCB Router ADV option 210 Allegro PCB Router ADV option L SPTDFM Allegro PCB Router DFM option 210 Allegro PCB Router DFM option L SPTHP Allegro PCB Router HP option 210 Allegro PCB Router HP option L Кто бы мог мне подсказать, где бы мне "бедному" это раздобыть? Аллегро PCB Router Версия 15.2.1 с OrCAD 10.3 имеется, Нужен мне только лицензионный файл или надо грузить весь Аллегро заново? Спасибо за заботу. :rolleyes:

-

Мы исползуем готовую микросхемку от Аналог Деваис (там в Application Note все хорошо расписано) -сигнал возбуждения 10кГц. (зависит от применяемого датчика) с микросхемы, толко мы его есче через аудио-усилитель пропускаем и на датчик. -вычисления угла черес полученный синус и косинус с датчика тож там же просчитывается, угол готов (12 бит) а вычисления угла уж больно много мороки, мы пробовали тож два АЦП к синусы и косинусу и черес Xilinx - CPLD вычисляли - в итоги не получалось ничего, тогда шеф наш сказал, что нам ето не надо- 3 месядца коту под хвост. :)

-

регулятор усилителя

labfab ответил labfab тема в Вопросы аналоговой техники

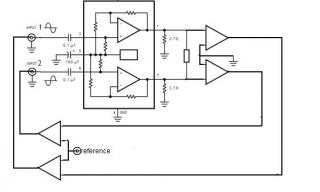

спасибо за ответ, схема на рисунки - принципиальная, то что она не работет ето факт, я просто хочу расмотреть варианты, или найти что либо похожее - если имеется у кого нибудь. :) ну да я думаю, что етот вариант надо б проверить, мож уже кто похожее делал или литературку знает, как ето умные луди делают - хотелось бы посмотреть, например схемки для управления управляемого усилителя в забисимости от ref, можно принципиально :) или как/где схемку для итилигентного детектора "слепить/раздобыть", что б тот в зависимости от входного наприжения управляемым усилителем правильно управлял? ето уж слишком сложно будет, такое точно не пойдет. :) боиюсь из за фильтра и ШУМ цепь будет слишком большая и возможны сильные искожения/перемещения в фазе и AD2S1200 будет выдовать ошибки, или я ошибаясь? Насколко я знаю, там время между входяшим сигналом (к. примеру синус) на датчик (ресолвер) и выходящими с датчика (синус и косинус) четко определенно. или я чего то не допонял? -

регулятор усилителя

labfab ответил labfab тема в Вопросы аналоговой техники

ето я имел ввиду, хотел написать 90 а получилось 180 :) при 180 вода кипит. ну в кратце надо б что на выходе было стабильное наприжение в районе Vpp = 15В +- 3%. на первом входе стерео усилителя приходит напряжение где то около 0,5В-0,8В синус, оно как раз то плавает (температура, толеранц, и другие нехорошии факторы) на втором входе стерео усилителя приходит напряжение тоже где то около 0,5В-0,8В косинус, в основном 1:1 идентично с первым входом, только сдвинуто. :) короче говоря исполсуется как Bridge Mode Application насчет AD8330 надо подумать, но боюсь не подойдет такой вариант. да и неохото уж слишком схему менять, все таки она работает, если подогнать делитель на входное наприжения. :) да, что то вроде этого, но без дорогих IC желательно.. :) да частота сигналов где то от 10kHz до 20кHz, не более. -

спасибо за столь быстрый ответ, я еще уснуть не успел ;-) в описании ошибся схема делит или можно сказать умножает входной сигнал на 4: а в таком варианте на 2: reg a_emu, b_emu; always @ (negedge nB_res or negedge RESET ) begin if (~RESET) a_emu <= 0; else a_emu <= ~A_res ^ b_emu; end always @ (posedge nB_res or negedge RESET ) begin if (~RESET) b_emu <= 0; else b_emu <= ~A_res ^ a_emu; end nB_res - не клок ето, а сигнал от датчика, используется толко в етом модуле как клок. :) вот я и думаию можь лутше на глобальный клок перейти, или смысла нет ?!. а насчет списка чувствительности процесса сразу не определил (спасибо), и в VHDL по другому асинхроный ресет выглядит. хотя там тож список чувствительности имеется. построение мне там больще нравится. здесь уж болно скользко.

-

регулятор усилителя

labfab опубликовал тема в Вопросы аналоговой техники

ишу схему или литературу: надо б соорудить регулятор усилителя (к примеру для LM4752) воозможно ли вообще такое! см. рисунок или мож кто что нить другое уже испробованое на практике подскажет. к сожалению в аналоговой течники новичок, так что много во не знаю или еще не сталкивался. :) мне надо регулировать входное наприжение усилителя в зависимости от выхода. входные сигналы идентичны толко на 180° сдвинуты т.е синус и косинус -

pls., оцените Verilog - код

labfab опубликовал тема в Языки проектирования на ПЛИС (FPGA)

привет, кто разбирается в Verilog, помогите оценить следуиющий код: reg a_emu, b_emu; always @ (posedge nB_res or negedge RESET ) begin if (~RESET) a_emu <= 0; else a_emu <= ~A_res ^ b_emu; end always @ (posedge nB_res or negedge RESET ) begin if (~RESET) b_emu <= 0; else b_emu <= ~A_res ^ a_emu; end какой здесь RESET - сигнал будет - синхроный или асинхроный? (мне что то ето условие (posedge nB_res or negedge RESET) не по душе, и стоит перед if (~RESET) ) во вторых мне не нравится что идет такт на сигнал nB_res. (ето дигитальный сигнал датчика ротора (вроде с AD2S1200)) должен сказать, что на практике код работает, но мне надо бы оценить его стабилность. в третьих, как мне кажеться, что с таким кодом возможны не учтеные состояния выходяшего сигнала, см. выделеное 1) always @ (posedge nB_res or negedge RESET ) begin if (~RESET) a_emu <= 0; else a_emu <= ~A_res ^ b_emu; end 2) always @ (posedge nB_res or negedge RESET ) begin if (~RESET) b_emu <= 0; else b_emu <= ~A_res ^ a_emu; end в первом процессе генерируется сигнал, а во втором он уже используется !!!, но как мне кажется ведь процессы работают параллельно или я заблуждаюсь?! или что-то не допонимаю... -

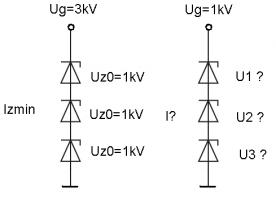

тож занимаюсь с недавних пор - IGBT и SCALE трейбером, особенно управлением IGBT с помощьюConcept - SCALE трейбера. Существуют ли готовые схемы, мож кто разробатывал ? в особености управление 3.3кВ IGBT у меня есть один вариант, но не проверен на практике. хотелось бы поиметь что то более стабилное. :) и еще вопрос на засыпку, какое напряжение будет на Z - диодах?! (см. рисунок) делится напрежение ровно, на каждай диод по 1/3 Ug? на каждом диоде по 333V ? (справа) предполагаемое напряжение Z - диода Uz0 = 1kV, Izmin что будет если напряжение на диодах меняется и не достигает минимального Uz0? существует ли какая либо зависимость? (формулы и т.д.)