Поиск

Показаны результаты для тегов 'virtex-7'.

-

Компания AMD Xilinx официально объявила о продлении поддержки всех ПЛИС 7 серии и адаптивных СнК до 2035 года. Это включает все классы скорости и температуры для ассортимента СнК Zynq ®-7000 , а также ПЛИС Kintex®-7 и Virtex®-7. Подробнее

-

- zynq-7000

- kintex ultrascale

- (и ещё 4 )

-

Ошибки при работе с DDR3

SVerilog опубликовал тема в Работаем с ПЛИС, области применения, выбор

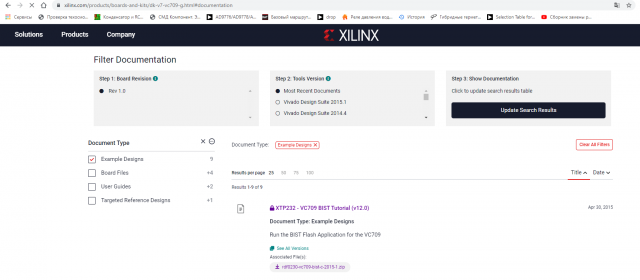

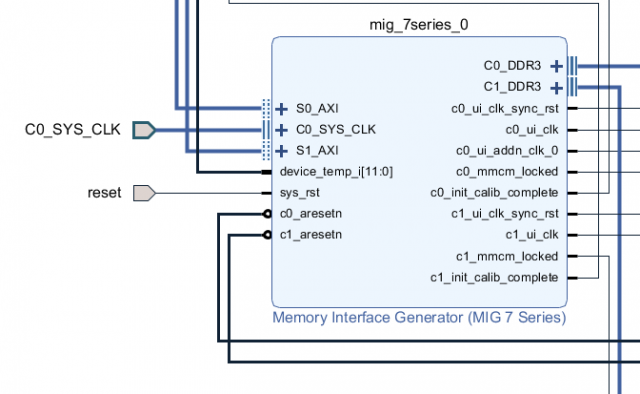

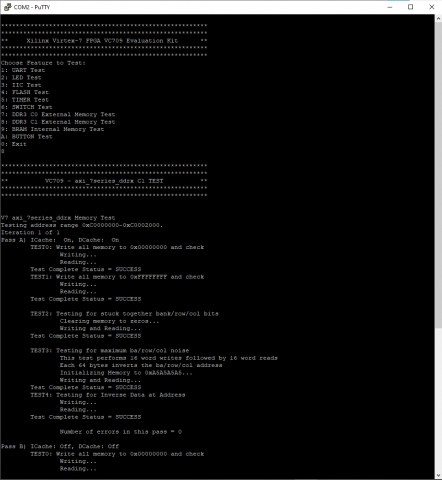

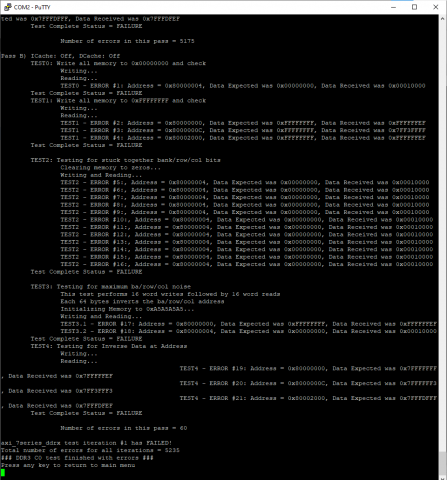

День добрый Имеется плата от Xilinx – VC709. На борту 7ой Виртекс к которому подключены две планки DD3 по 4Гб каждая. Также имеется проект самотестирования платы - так называемый BIST (XTP232) - (проверка платы – что загораются светодиодики, нажимаются кнопочки и пр) – выложен на сайте Xilinx: (https://www.xilinx.com/products/boards-and-kits/dk-v7-vc709-g.html#documentation) Так как планки памяти две, то в block design есть двухканальный mig7: Так вот при тестировании канала C1 тесты успешно проходят: , при тестировании канала C0 тесты не проходят: При этом я просто заливаю немодифицированный bitelf из архива с проектом. Если же скомпилировать проект под vivado 2018.3 то канал C1 также проходит, а канал C0 не проходит, но немного по другому (меняются адреса ошибок) Код проверки каналов для MicroBlaze идентичен для обоих каналов : выполняется вызов функций hello_mem_c0() или hello_mem_c1() Для канала C0: для канала C1: Планки памяти менял местами – результат не меняется (в канале C0 ошибки). Конечно очень подозрительно что немодифицированный bitelf тестирует с ошибками - наводит на подозрения о неисправности... Ранее с памятью DDR не работал, но возможно кто-нибудь сталкивался с чем то подобным, куда копать подскажите пожалуйста- 5 ответов

-

- memory test

- ddr3

-

(и ещё 3 )

C тегом:

-

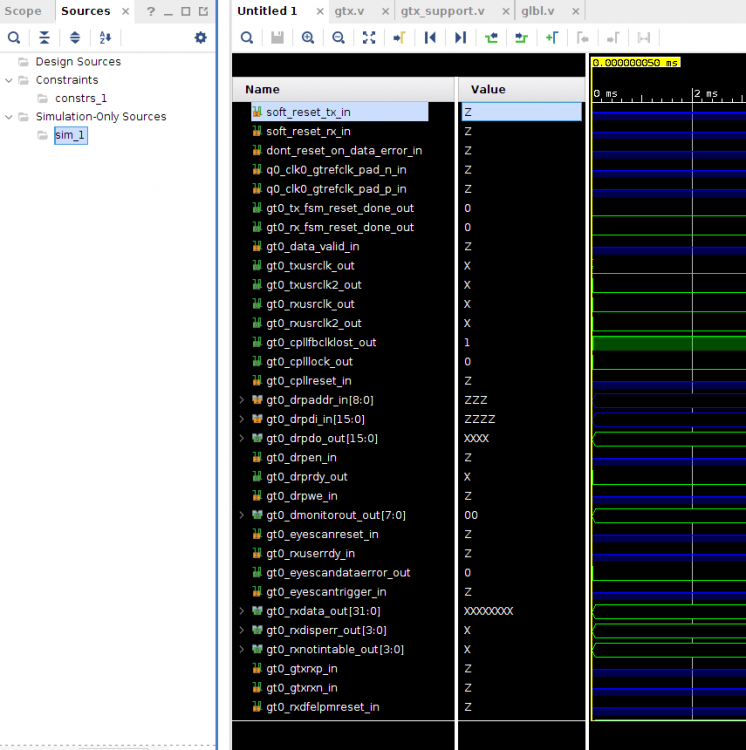

Пока валяется плата с Virtex-7, осваиваю трансиверы GTX. Возникли такие проблемы: 1) Симуляция, которую создает визард, оказывается нерабочей. Решил дописать в скрипт, который оно сгенерировало, опцию вывода в GUI (xsim --gui) и увидел, что всё висит в Z, исходные файлы отсутствуют, непонятно что там top-модуль. Прилагаю картину того что я вижу. Причем, подобные нелепые файлы симуляции вижу и у других сим-скриптов, созданных Vivado 2018 для других IP-ядер. Что я всё время делаю не так, что выходят нерабочие симуляционные проекты? 2) Читаю документацию ug476_7Series_Transceivers.pdf и там всё что касается начальной инициализации, процедуры сброса. Даю 1 такт cpllreset, но ничего не происходит. Играясь с разными комбинациями сбросов, коих там куча, удалось увидеть cplllock, но в симуляторе видно, что через некоторое время он молча сбрасывается в lost. Кто может привести пример процедуры сброса или вкратце описать ее словами и примерными цифрами таймингов? Вот работала бы симуляция, я бы увидел в ней что и как правильно делать. Но не работает ни моя, ни "визардная" симуляция на базе xsim. Такты в симуляции подаю P/N 125 МГц, как и требуется согласно моим настройкам. И есть еще один вариант - на симуляцию GTX трансиверов полагаться нельзя? И тогда я брошу эти безнадежные попытки и сразу попробую поработать с этим на железе, отлаживая через чипскоп или даже просто uart.