Поиск

Показаны результаты для тегов 'register'.

-

Тема выделена из темы https://electronix.ru/forum/topic/173971-ne-vsegda-srabatyvaet-uslovie/ Будьте добры, уточните, пожалуйста, откуда вы добыли информацию о "100-200пс" для выхода триггера из метастабильного состояния в Xilinx 7-Series ?

- 35 ответов

-

- метастабильность

- metastability

- (и ещё 5 )

-

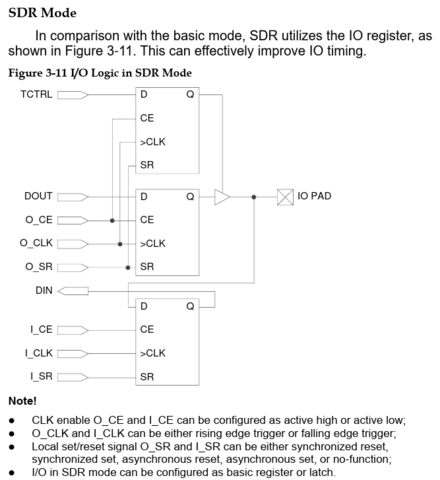

Доброго времени суток всем участникам, В даташите на GW2A (DS102-2.6E) приведена следующая иллюстрация регистров ячейки ввода-вывода в режиме SDR: Т.е. выглядит всё так, как будто бы есть два независимых входа тактовых сигналов: O_CLK и I_CLK. При этом попытка упаковать в ячейку ввода-вывода двух триггеров, тактируемых различными тактовыми сигналами, приводит к выдаче ошибки на этапе PnR: ERROR (CT1094) : 'dut_inst/out_q2_0_s0' can't be placed according to constraint У кого-нибудь получилось упаковать два подобных триггера в одну ячейку? Или может быть есть место, где описана невозможность подобной упаковки?

-

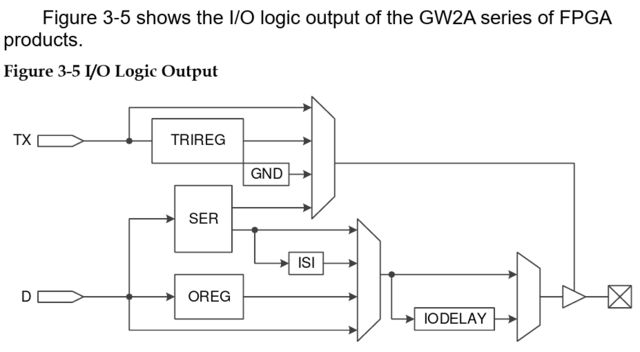

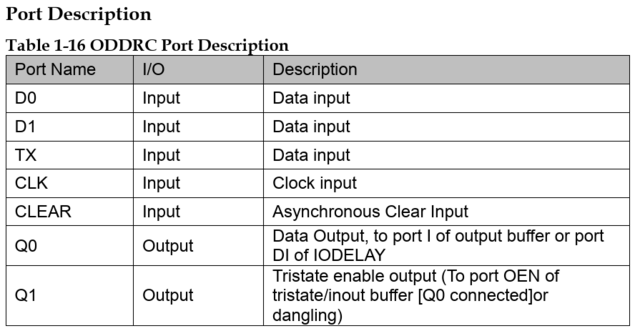

Доброго времени суток всем участникам, Попытавшись разместить выходные регистры данных и управления OEN в ячейках ввода/вывода у Gowin GW2A (используется Gowin_V1.9.9Beta-1 и пробовал Gowin_V1.9.8.11) я столкнулся с рядом проблем: Отсутствуют констрейнты, которые бы позволяли на уровне исходника на Verilog говорить среде, что синтезируемый триггер (регистр) необходимо разместить во встроенном в ячейку ВВ триггере. В описании архитектуры GW2A приводится следующая иллюстрация: Но при этом в библиотеке примитивов отсутствуют соответствующие примитивы для OREG/TRIREG. Есть, правда ODDR, но к нему есть свои вопросы и о них ниже. Для режима SDR ниже приводится более детальная иллюстрация структуры ячейки: При этом для входов сброса есть следующее примечание: "Local set/reset signal O_SR and I_SR can be either synchronized reset, synchronized set, asynchronous reset, asynchronous set, or no-function;". Т.е. должны поддерживаться все возможные режимы сброса (вполне ожидаемо, на первый взгляд). Однако из-за отсутствия в библиотеке соответствующих примитивов на практике в этом убедиться затруднительно. При этом у приведенных в описании архитектуры триггеров для режима DDR вход сброса отсутствует. С другой стороны в документе "Gowin FPGA Primitive User Guide", где казалось бы должны были быть описаны указанные в описании архитектуры элементы (триггеры) есть только описание регистров DDR: Причём, что очень странно, в описании портов ODDRC, для входа CLEAR указана поддержка только асинхронного режима: После выполнения PnR с настройками размещения регистров в IOB в результатах бэканнотации (нетлист, генерируемый после PnR) у триггеров, которые я считал должны были быть размещены в ячейках ВВ, я вижу инстанцирование DFFR с очень подозрительным недокументированным аттрибутом: (*gowin_io_reg = "FALSE" *) DFFR ... Найти описание этого gowin_io_reg я нигде не смог, гугл про него не знает. Как можно проконтролировать, какие регистры попали в триггера ячеек ВВ, а какие нет? Ни в одном репорте этих данных нет. Собственно вопрос: какие есть варианты управления размещением триггеров для надежного их размещения в ячейках ВВ? Пока в голову приходит только один вариант: явно инстанцировать ODDRC в режиме SDR (подавать на оба входа один и тот же сигнал) и полагаться на него. Но это выглядит крайне кривой затеей, т.к. исходя из описания архитектуры должны быть возможности как минимум использовать синхронных сброс триггеров в ячейках ВВ. PS: Похоже, что та же проблема и с входными регистрами (триггерами). Однако с ними всё-таки немного проще и, надеюсь, решение для выходов будет вполне применимо и для входов. PPS: Выяснилось, что для размещения регистров управления третьим состоянием выходов в ячейках ВВ важна полярность. Т.е. если активный уровень сигнала управления будет 1, то между этим регистром и входом OEN на буфере ВВ синтезатор добавит инвертор и это не позволит PnR разместить соответствующий триггер в ячейке ВВ. Поэтому необходимо учитывать эту особенность и правильно выбирать активный уровень этих сигналов в проекте (должен быть active-low).

-

LVDS данные с КМОП-матрицы

Klayton опубликовал тема в от ТТЛ до LVDS здесь

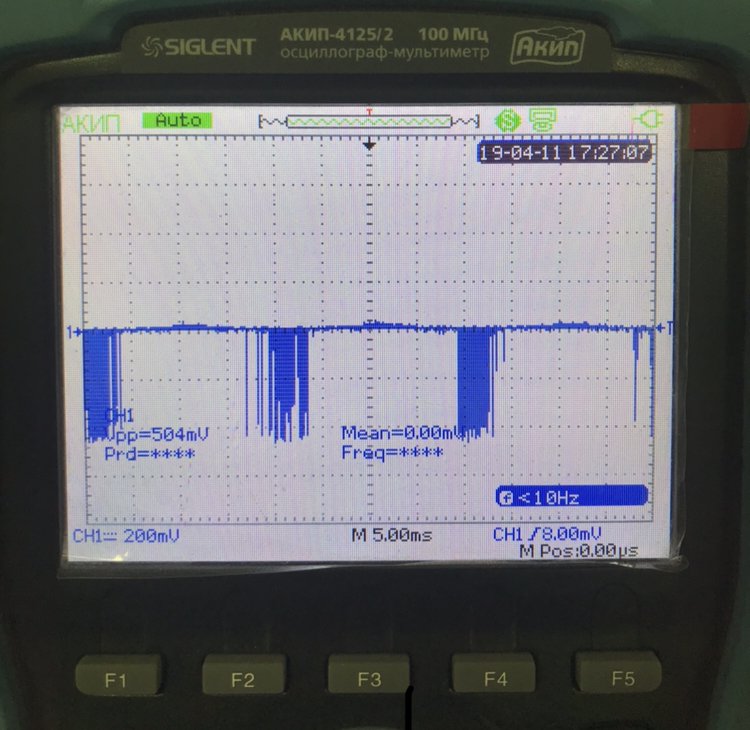

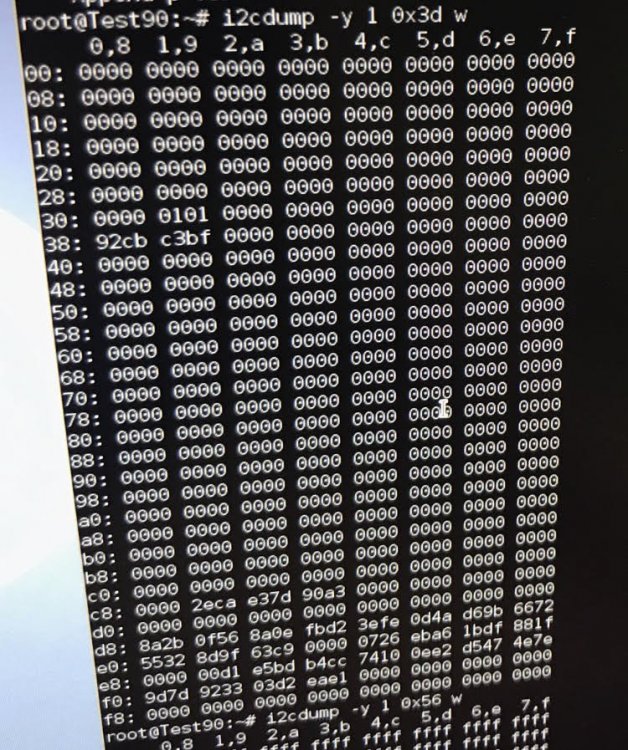

Всем привет! Имеется отладочная плата с сенсором MT9v124. При подаче питания на выходе LVDS следующий непонятный сигнал (см. Прикрепленные) . Сигнал снимался с линий LVDS относительно друг друга. Причем переключение на плате джмапера Standby mode никаких изменений не вызывает. Ток потребления 10 мА (который по всей видимости потребляет только кварц, потому что при его отключении ток падает до 0). Возможно требуется прописать в регистр матрицы какую-то команду через I2C, чтоб она "завелась"? Описание регистров (удобнее всего смотреть в браузере internet explore) и считанные данные с регистров матрицы на плате тоже прикрепляю. MT9V124-REV2.xsdat EVBUM2468-D.PDF MT9V124-D-1101616.pdf