Поиск

Показаны результаты для тегов 'microblaze'.

-

Собираем MicroBlaze (на русском)

KeisN13 опубликовал тема в Обучающие видео-материалы и обмен опытом

Сборка софт процессора MicroBlaze от Xilinx на русском в пошаговом режиме с огромным количеством картинок в нескольких частях: Разработка процессорной системы на базе софт-процессора MicroBlaze в среде Xilinx Vivado IDE/HLx. Часть 1. Разработка процессорной системы на базе софт-процессора MicroBlaze в среде Xilinx Vivado IDE/HLx. Часть 2. Программирование загрузочной FLASH для запуска MicroBlaze Подключение подсистемы памяти к MicroBlaze (MIG 7 Series)- 16 ответов

-

- microblaze

- arty

-

(и ещё 2 )

C тегом:

-

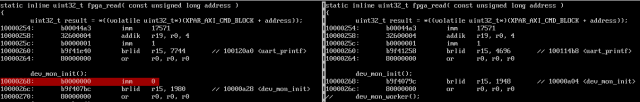

Всем привет! Обнаружилась одна очень неприятная ошибка в поведении линкера для microblaze (mb-ld), по крайней мере для Vivado 2019.2 (на других еще не проверял). Выражается она в неправильном вычислении линкером смещений упакованных структур, содержащихся внутри не упакованных. Так это проявилось у меня. При этом изменение порядка полей в структуре (сначала неупакованные данные, потом упакованные структуры) на первый взгляд убирает проблему, но пока гарантий нет никаких.Эта ошибка достаточно коварна, т.к. на её появление влияет также порядок вызова функций в программе. В моём случае добавления в начало main() вызова функции, использующего эти данные, устраняет ошибку обращения конкретно к этой структуре. Судя по наблюдаемому поведению линкера, проблема заключается в удалении из результирующего ELF "ненужных" команд imm 0, но без последующей коррекции смещений. Нашел сходный баг, которому уже 10 лет и он по-прежнему без движения. В нем описывается данное поведение только для исходников на ассемблере, но в моем случае то же самое наблюдается и для исходников на C/C++. Слева результат objdump после компиляции с --no-relax, справа с опцией --relax: Как видно, была удалена та самая команда imm 0. Поскольку при использовании для линковки mb-gcc опция --relax включена по-умолчанию, то такое поведение может внезапно выйти боком в самый неожиданный момент. Минус отключения relax - возрастание размера прошивки, но по-моему обычно стабильность важнее. Тем более что проверить, что именно ваш проект не подвержен этой ошибке можно только длительным тестированием и то гарантии в результате дать практически невозможно. Кто-нибудь еще сталкивался с подобной проблемой? Может быть я что-то упускаю и есть другой путь обхода этой проблемы?

- 18 ответов

-

- mb-gcc

- microblaze

-

(и ещё 4 )

C тегом:

-

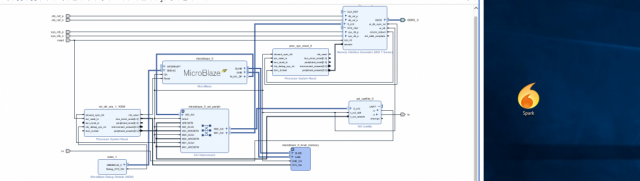

В двух словах. Во-первых, это мой первый опыт с Zynq, во-вторых, не могу уловить суть работы с потоковой шиной AXI-Stream. Или не понимаю сообщений от тайминг-аналайзера. Теперь подробней... Перед собственно запуском АЦП, наслушавшись как в Zynq все быстро и удобно, посмотрев несколько видео, и почитав несколько статей, создал простой проект, где Microblaze для конфигурирования в будущем АЦП и ЦАП, а ARM уже для работы с данными. Есть общая память между Zynq и Microblaze, есть общая периферия. Частота работа с периферией 50 Мгц. Раньше делал со стороны ARM 100 МГц, сейчас сделал поменьше. Не уверен, что выходную частоту процессорного ядра можно использовать в FPGA безболезненно, поэтому пропустил на всякий случай клок через Clock-wizard. Создал пару кастомных компонентов куда в дальнейшем перекочует работа с АЦП и ЦАП соответственно. И для проверки "скелета" все соединил и собрал. Сообщения про времянки уверяют меня, что ничего не работает. Пробовал вставлять регистры, вставил двухклоковую FIFO, опустил частоту работы с портом HP до смешных значений. Увеличил разрядность с 32 до 64 разрядов, завел два выхода в компоненте и использовал сразу два порта HP, помня рекомендацию Xilinx, что подключать нужно к портам через один, т.е. к 0 и 2 или к 1 и 3. Можно услышать от опытных людей критику по структуре проекта в целом и рекомендации по констрейнам? Я так понял, что как и для спартан-6 констрейны нужно прописывать только ко входной частоте, а производные клоки просчитываются автоматически. Тут также? Проект размещу по ссылке, т.к. его размер превышает ограничение в 5 Мб: EK-Z7-ZC702-G_Zynq_MB

- 19 ответов

-

- zynq

- microblaze

- (и ещё 4 )

-

MicroBlaze + DDR3

Drakonof опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Всем привет, подскажите пожалуйста, как правильно подключить ddr к microScale? Задача для многих простая, но боюсь что я подвис. Дело в том что проц удержеваеться в ресете при дэбаге в SDK. Использую отладку, но при создание проекта абстрагировался от нее и выбрал просто плисину. Vivado 2018.3 Artix 7 Constraint file: set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design] set_property BITSTREAM.CONFIG.UNUSEDPIN Pullup [current_design] set_property CFGBVS VCCO [current_design] set_property CONFIG_VOLTAGE 3.3 [current_design] set_property PACKAGE_PIN P6 [get_ports {reset}] set_property IOSTANDARD SSTL15 [get_ports {reset}] set_property PACKAGE_PIN U19 [get_ports {tx}] set_property IOSTANDARD LVCMOS18 [get_ports {tx}] set_property PACKAGE_PIN T19 [get_ports {rx}] set_property IOSTANDARD LVCMOS18 [get_ports {rx}]- 14 ответов

-

- xilinx

- microblaze

-

(и ещё 1 )

C тегом: