Поиск

Показаны результаты для тегов 'bf561'.

-

Написал и отладил работу по SPI и UART для BF561 отдельно по каждой периферии. Попробовал вместе - не работает. Работает или одна или вторая периферия в зависимости от порядка инициализации. В начале отключил ядро А и начал проверять на какой вектор можно посадить прерывание SPI. Для этого написал макросы типа такого: Работают вектора EVT_IVG10, 11, 12, 14. Не работате 15-ый, а 13 у меня под watchdog. Для UART пробовал 8 и 10 вектора. До этого ПО работало только с прерываниями по PPI и SPORT которые расположены по умолчанию на EVT_IVG8 и EVT_IVG9. В документации не нашел что регистры SICB_IMASK0 и pSICB_IAR3 доступны только в режиме супервизора. Неработоспособность проявляется в отсутсвии хотя-бы одного вызова прерывания. Дополнение Прочитал документацию, стало понятно, что процессор находится в режиме супервизора. Вызов прерывания 15 рекомендуемым методом перехода на пользовательскую программу. При старте программы IPEND как раз показывает что прерывание 15 отложено. То есть ничего не мешает программированию любых регистров, а прерывания конфликтуют.

-

Понадобилось запустить UART с возможностью отработки таймаута по приему. В самом UART такой вариант отсутсвует. Пробовал с помощью обычного таймера. Но в нем счетчик без возможности записи со стороны процессора. Корректно перезапускать не получилось. Более менее получилось с Watchdog. Вот так описал прерывание #define WDTPERIOD 10000 EX_INTERRUPT_HANDLER (Watchdog_ISR) { *pWDOGB_CNT = WDTPERIOD; *pFIO0_FLAG_T = DBG_PIN; // toggle asm("ssync;"); } Вот так настраиваю сам Watchdog: void WDOGinit (void) { // Запрет сторожевого таймера: *pWDOGB_CTL = WDDIS; ssync(); // Инициализация счетчика: *pWDOGB_CNT = WDTPERIOD; ssync(); register_handler(ik_ivg13, Watchdog_ISR); /* Note that if the general-purpose interrupt option is selected, the System Interrupt Mask register (SIC_IMASK) should be appropriately configured to unmask that interrupt. */ // Table 4-7. Peripheral Interrupt Source Reset State //Watchdog Timer interrupt - 59 - IVG13 - SIC_IMASK1 == 27 // разрешение логической 1 *pSICB_IMASK1 |= SIC_MASK(27);\ // Разрешение сторожевого таймера, генерировать обычное прерывание // при срабатывании сторожевого таймера: *pWDOGB_CTL = WDEN | WDEV_GPI; // 0x0FF0 | 0x0004 ssync(); *pWDOGB_STAT = 0; } Реально удалось загрузить на лету и прошить работающую версию с WDTPERIOD = 1000. На выходе видно частоту чуть больше 2МГц. Как только поменяю значение на другое - или нет сигнала на выходе или остается "старый" или отваливается эмулятор. В сети нашел примеры для BF-60x : adi_int_InstallHandler(INTR_WDOG1_EXP, wdtISR, NULL, true); _wdtDisable(); _wdtSetTimeout(wdtPeriod); _wdtEnable(); Но таких функций в примерах в моем VDSP нет. "INTR_WDOG1_EXP" - ни одной ссылки в Интернете. Понятно, что с порядком обращения к регистрам проблема, но как найти?

-

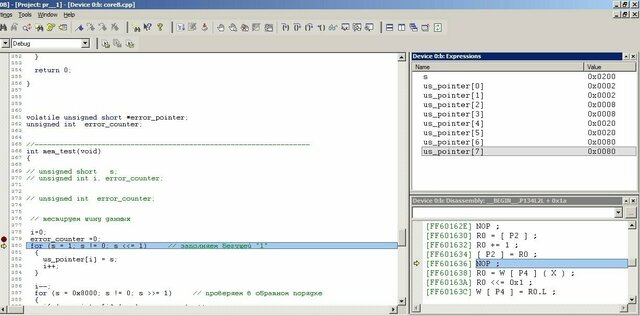

Использовали плату BF561 с одним модулем памяти на 64 мегабайта 16 бит. Для нее был написан простенький тест памяти. Сейчас плату переразвели на 2 микросхемы памяти. В результате получили те же 64 мегабайта, но шина данных 32 бита. Залил старую программу - ростейший тест с бекущей "1" по шине данных не идет. Заполняет память как на картинке. Взял документ EE-326 "Blackfin® Processor and SDRAM Technology" Перепроверил схему на соответствие рекомендациям - все соответствует. Поискал информацию, как переключить шину 16 на 32 - не нашел. Есть рекомендации по настройке линкера, при размещении данных в SDRAM. Но в тестирующей программе размещение данных/кода в SDRAM не используется. Вот функция инициализации SDRAM контроллера void sdram_config() { unsigned int mem_SDRRC; unsigned int mem_SDGCTL = SCTLE | CL_3 | TRAS_6 | TRP_3 | TRCD_3 | TWR_2 | PSS | FBBRW | 0x80000000; // calculating EBIU_SDRRC double t_ref = 64 * 1e-3; double sclk = ((double) get_sclk()); // Hz unsigned int row_number = 13; unsigned short t_ras = (mem_SDGCTL >> 6) & 0xF; unsigned short t_rp = (mem_SDGCTL >> 11) & 0x7; mem_SDRRC = (sclk * t_ref) / (1 << row_number) - (t_ras + t_rp); // disable SDRAM Bank0 *pEBIU_SDGCTL &= 0xFFFFFFFE; *pEBIU_SDRRC = mem_SDRRC; *pEBIU_SDBCTL = EB0_E | EB0_SZ_64 | EB0_CAW_10; *pEBIU_SDGCTL = mem_SDGCTL; } Ну и извечных два вопроса: Кто виноват, что делать?