Поиск

Показаны результаты для тегов 'altlvds_rx'.

-

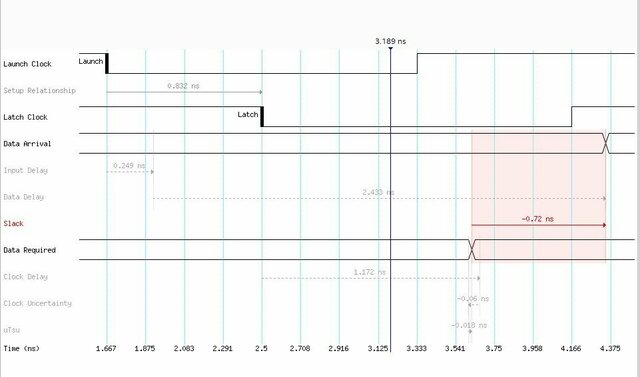

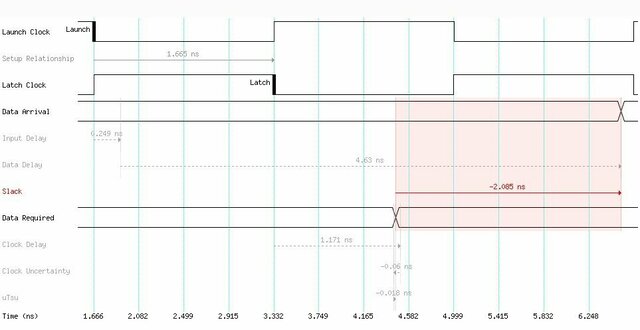

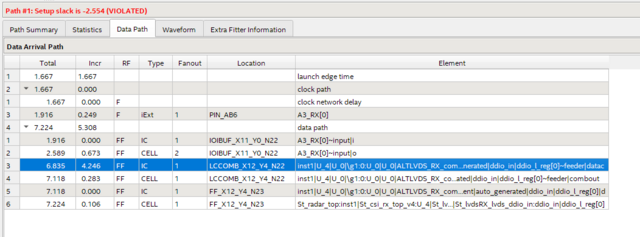

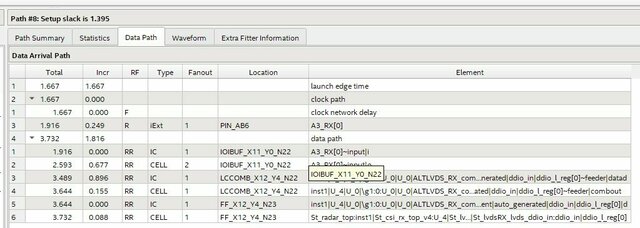

Добрый день! В проекте есть приемник CSI2 на частоте на частоте 300 МГц, 600 Мбит/с в режиме ДДР соответственно. Для приема используется блок altlvds_rx c десериализацией 8. Входной клок заведен на отдельную PLL, и c[0] используется чтобы латчить входные данные. Данные center-aligned, задержки прописаны по методичке ddr-timing-cookbook. В PLL ставлю нулевую задержку. Собираю, смотрю тайминги Слак по setup. Напрашивается добавить фазы в PLL. Добавляю 90гр и смотрю опять Фаза накрутилась, но квартус зачем-то навалил и задержки по данным. Сперва решил, что он куда-то регистры разместил далеко, залокейтил их как в первой сборке, но оказалось он впихнул на вход комбинационную логику которая делает DOUT = DIN и тупо добавляет задержки данных. Ставил 120гр фазы, квартус уменьшает задержку комбинационной логики, фазы PLL хватает чтоб слак по setup убрать, но теперь надо бороться с холдом... ок, вижу что там нужно вписать теперь мультицикл, так как фронт вылез за launch, вписываю, собираю - он опять увеличил комбинационную задержку так что и по сетапу прослакано... Можно ли сделать так, чтобы квартус не довавлял/убавлял по свой прихоти эту комбинационную логику пустую? Или я что то не так трактую? Вот таблицы DataPath из репорта до и после добавления мультицикла. +3.5 нс на ровном месте Я не специалист по заданию ограничений но может как-то это решается? Если нет, то каким путем нужно идти, чтобы добиться сходимости таймингов? PS Проект достался по наследству, он как-то работал в железе до тех пор пока не потребовалось сделать пару изменений. После сборки данные перестали приниматься. Оказалось нет входных констрейнов. Я немного слышал о ПЛИС и решил, что смогу быстренько подчинить, а он как уж на сковороде

- 11 ответов

-

- intel

- cyclone 10 lp

-

(и ещё 1 )

C тегом: