polyvyannyy

Участник-

Постов

34 -

Зарегистрирован

-

Посещение

Весь контент polyvyannyy

-

Ремонт платы с ПЛИС

polyvyannyy опубликовал тема в Работаем с ПЛИС, области применения, выбор

Всем привет! Кто подскажет, какие компании в Москве могут выполнить диагностику и, при необходимости, ремонт отладочной платы с ПЛИС? -

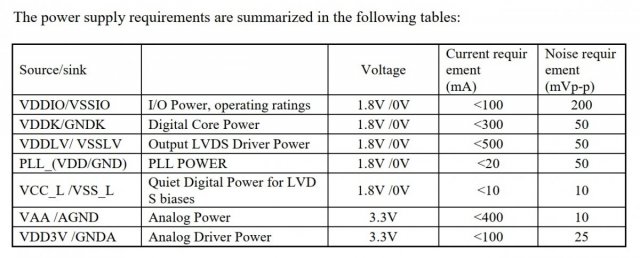

в пдф есть вот такая табличка Смотрел осциллом все питающие напряжения... по всем напряжениям шум пик-ту-пик идет более чем 200мВ. И более того присутствуют периодические тычки. Если плис не прошита шум такой же, а вот тычков нет.

-

Сегодня буду проверять. А есть вообще допустимые пределы шумов по питанию?

-

Проблема с периодичными полосами(как на картинке в самом первом посте) решена. Эта проблема возникала из-за работы сенсора не на максимальной частоте кадров. Перевел в режим максимальной частоты кадров. Ситуация изменилась.Теперь периодические полосы ушли. Появились теперь просто горизонтальные полосы. Прикрепил файл HS1048_max_exp.bmp

-

Да. У нас тоже адски греется. У нас не одна горизонтальная полоса, а много. Они повторяются с детерминированным периодом. Сейчас появилось подозрение, что сенсор выдает такой результат при частоте кадров вдвое меньшей от максимума. Буду пробовать завести на максимум

-

Не помогает. Полосы всё равно есть

-

RGB Не совсем понял, что именно перепутано?полярности на приемнике?

-

В pdf на сенсор есть вот такая строчка "If the shutter line visible, the position of PD_n inside the row need to be adjusted". Но из контекста совершенно не понятно про какую "row" идет речь. Как я понимаю, сигнал PD_n определяет время, в течение которого идет накопление заряда в пикселе. Но этот сигнал(для прикрепленного кадра) задан уровнем на протяжении чтения всего кадра, то есть по всем "row".

-

Высокоскоростной сенсор LUX13HS

polyvyannyy опубликовал тема в Работаем с ПЛИС, области применения, выбор

Всем привет! Может кто-нибудь проконсультровать по этому сенсору? Получил изображение, но на нем явно видны полосы. Не особо понятно, что с ними делать. Кто имеет опыт работы с подобными сенсорами ну или кто в принципе знает решение, подскажите, что делать? Прикрепил файл с картинкой HS63_28082019.bmp -

В общем, проблема до конца не решена. Но подобрал рабочий вариант. Все работает при режиме записи берстом порциями по 32 слова. В таком режиме можно считывать совершенно любым куском (конечно же, в пределах максимальной длины берста)

-

А можно ссылку на документ, где это написано?

-

Всем привет! Текущая проблема не решена. Все притормозилось, так как проект с памятью ушел на некторое время на второй план. Но сейчас произошло воскрешение проекта) итак, что удалось выяснить дополнительно... 1. Если я пишу в режимер burst порциями по 16 слов и записываю всю память (на шину авлон выставляю адреса соответственно 0, 16, 32, 48, 64....и тд), а после записи всей памяти начинаю такими же порциями считывать, то все работает замечательно. 2. Если я пишу один пакет данных размером 64 слова и потом его сразу считываю, то все работатет. 3. Если я записываю всю память порциями по 64 слова, а после начинаю считывать, то не работает (нет ответа на самую первую команду чтения) Пока нет понимания как это все работает.

-

Хмм, очень даже похоже. Вы решили эту проблему? Нет. Посылка однозначно меньше размером

-

У меня в системе один Slave-контроллер памяти. Но я попробовал Ваш вариант. Все равно зависает.

-

Intel Arria V + DDR3

polyvyannyy опубликовал тема в Работаем с ПЛИС, области применения, выбор

Всем привет! Столкнулся с проблемой работы с памятью DDR3. Суть в следующем...использую софтовое ядро от Альтеры DDR3 SDRAM Controller with UniPHY и ПЛИС Arria V. При включении питания платы успешно проходит как инициализация так и каллибровка памяти. Данные пишу в режиме burst по 83 слова. При считывании данных нормально выгружается часть данных, а после контроллер перестает выдавать данные. Порция выгружаемых данных может быть разная.Я из логики формирую на шине Avalon-MM команду на чтение, а контроллер просто не отвечает на неё. (сигнал waitrequest при формировании команд записи и чтения учитывается и отслеживается) Кто имеет хороший опыт работы с контроллером DDR3 и памятью подскажите или посоветуйте, что еще посмотреть. -

Здравствуйте! Вот и я столкнулся сейчас с проблемой. Все вроде настраиваю как полагается, прописываю все пути. Но при попытке закомитить любое изменение приводит к сообщению "Commit failed. Invalid repository.". Дальше этого двинуться не удается.

-

HDL Designer + SVN

polyvyannyy опубликовал тема в Среды разработки - обсуждаем САПРы

Всем привет! Есть на форуме те, кто активно пользуется HDL Designer'ом с запущенной в нем системой контроля версий SVN? -

Младший разработчик FPGA

polyvyannyy ответил polina_hr тема в Предлагаю работу

Добрый день, Полина! Удаленка возможна? -

А если ПЛИС инициирует запись в хост, как узнать какой адрес вставлять в заголовок TLP посылки?

-

Спасибо большое за столь развернутые ответы. Теперь буду приводить мысли в порядок и пробовать)Уверен, будут еще вопросы ;)

-

Спасибо за ссылку!Буду изучать.

-

PCIe

polyvyannyy ответил polyvyannyy тема в Работаем с ПЛИС, области применения, выбор

Версия была 16.0 Standard edition. В версии 17.0 все разводится. Спасибо -

PCIe and FPGA

polyvyannyy опубликовал тема в Работаем с ПЛИС, области применения, выбор

Всем привет, уважаемые форумчане! Возникла необходимость поднять на девборде PCIe 3x8. Референсный дизайн загружен и все работает. Но теперь нужно сделать прием и отправку своих данных с/на хост. И вот тут то возникла куча вопросов и непониманий. Информации по теории PCIe полно, но никак не удается найти конкретики относительно ПЛИС...какой именно у меня должен быть порядок действий со стороны ПЛИС, чтобы организовать чтение/запись данных в ОЗУ хоста? таблица дискрипторов...кто её формирует, где она хранится?В голове каша и нет четкого понимания. Прошу помощи у опытных в данной теме людей. За любые ссылки, проекты, которые можно взять за основу, буду благодарен. -

PCIe

polyvyannyy опубликовал тема в Работаем с ПЛИС, области применения, выбор

Всем привет! Столкнулись со следующей проблемой при разводке референсного дизайна от Альтеры. Имеетcя борда (TR10a-HL на Arria 10). Вместе с ней идет диск с разными исходниками, референсными дизайнами, доками и т.д. Берем референсный дизайн для PCIe Gen3 8links и пытаемся развести в Quartus 16.1.2. На что на этапе Fitter получаем ошибку следующего содержания " Error (15653): The Fitter cannot find a legal configuration for the following atoms. Update any outdated transceiver PHY IP cores, correct any illegal pin assignments, and then recompile your design. Error (15744): In atom 'ep_g3x8_avmm256_integrated:u0|ep_g3x8_avmm256_integrated_altera_pcie_a10_hip _161_ccwlwii:dut|altpcie_a10_hip_pipen1b:altpcie_a10_hip_pipen1b|altpcie_a10_hip_ pllnphy:g_xcvr.altpcie_a10_hip_pllnphy|phy_g3x8:g_xcvr.g_phy_g3x8.phy_g3x8|ep_g3x 8_avmm256_integrated_altera_xcvr_native_a10_161_eskpmsy:phy_g3x8|twentynm_xcvr_na tive:g_xcvr_native_insts[0].twentynm_xcvr_native_inst|twentynm_xcvr_native_rev_20 nm5:twentynm_xcvr_native_inst|twentynm_pma_rev_20nm5:inst_twentynm_pma|gen_twenty nm_hssi_pma_rx_sd.inst_twentynm_hssi_pma_rx_sd' " Возможно, кто-нибудь сталкивался с подобной проблемой и сможет подсказать в каком направлкении двинуться? -

Посмотрел RTL после синтеза. Проверил все управляющие сигналы QSFP и выяснил, что именно LPMODE был объявлен как входной)) (криворучка я)