RedHeadIvan

-

Постов

136 -

Зарегистрирован

Сообщения, опубликованные RedHeadIvan

-

-

09.11.2020 в 12:48, Aner сказал:

Может там у вас уже нелинейности выходных каскадов генераторов задействованы.

21 час назад, Prostograf сказал:при суммировании двух сигналов генератора напрямую без аттенюаторов по выходам каждого генератора интермод возрастал

Кажется, причина была как раз в этом. Аттенюаторы не использовал, и без развязки получилось грязновато... Разнес частоты совсем на края фильтра, добавил еще один такой же, стало повеселее. Вряд ли получится еще лучше подавить, так что придется сделать вывод, что усилитель даташиту соответствует адекватно. Аттенюаторы добавить это хорошая мысль, но тогда придется наддать мощности с генераторов, а это уже их собственные нелинейности задерет. Не знаю, что лучше. В любом случае спасибо, что обратили на этот аспект внимание, мне было не очевидно)

11.11.2020 в 04:39, soldat_shveyk сказал:проверьте уровень собственных нелинейностей АЦП

Там по документации регламентируется около -70 дБ SFDR, на правду похожде. уровень с усилителем был заметно выше, поэтому нелинейности АЦП задвинули на второй план

09.11.2020 в 18:44, MW_Юрий сказал:Все это вылезать до условий измерения разработчика невозможно

Увы. Видимо, даже хорошие приборы и кабели (по крайней мере с моей точки зрения) не так хороши, чтобы быть близко к характеристикам тестового стенда(

10.11.2020 в 16:30, rfserg сказал:Усиление на борде соответствует даташиту? Был похожий вариант - не "балунили" балуны, кривая АЧХ, ошибка распиновки в балунах.

Да, тут все хорошо. Промеряли, проверяли

-

-

-

11 часов назад, Aner сказал:

Правильно пишут, ... "пролаз" или "просачивание" сигнала. Сам наблюдал не раз. А у того мех фильтра ну самое лучшее до 30...50dB. Фильтры и лучше 90dB бывают, но не в тех мех. реализациях и не на тех частотах. Просто посмотрите сколько пролазит с кабеля того вашего векторника или анализатора.

А можно немного поподробнее про 30...50? Ведь векторник - вполне объективная вещь, разве нет?

И пролаз имеется в виду в контексте паразитного излучения самого кабеля, то что, например, через оплетку лезет? Получается, можно улучшить результат экранировкой платы усилка?

-

1 минуту назад, MW_Юрий сказал:

Измеряете не правильно. подавление -90 ничем не измерите, самообман. Фильтр неэкранированный, пролазы гарантированы и вообще фильтр -90 не реализуем

измерял и на векторнике цепей, и на анализаторе сигналов, все ок. я же не с потолка цифру взял) фильтр, если что, отдельным модулем, вот типа такого, только модель другая. с даташитом цифры +- сходятся

а вообще фильтры и лучше 90 бывают, если аккуратно сделать и измерить)

-

Коллеги, здравствуйте!

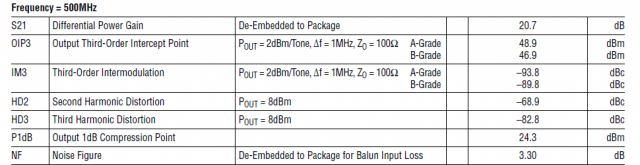

Делаю входной каскад для АЦП, решили использовать усилок LTC6430-20

Подключил оценочную плату к плате с АЦП - высоковат уровень 2 и 3 гармоник, порядка -60 дБн (частота 300 МГц), в даташите обещают значительно лучшие цифры (-75, -77 для 2 и 3 соответственно)

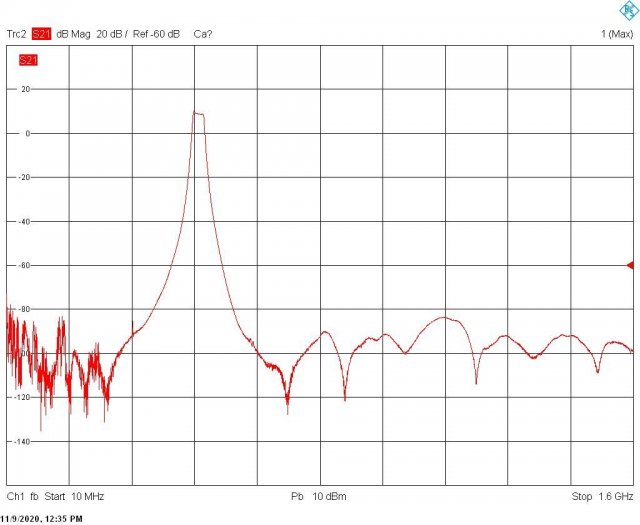

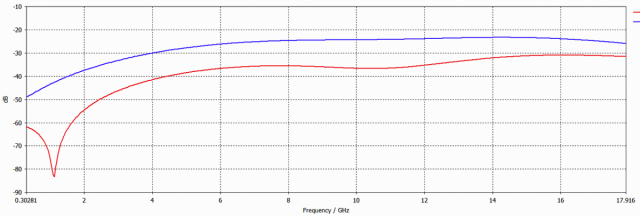

Открыл мануал на борду, там методика измерения IM3 приведена: подаем на вход 500 МГц и 501 МГц с мощностями на анализаторе 2 дБм на тон, должны видеть комбинашку третьего порядка на уровне -98 дБн. Я намерил вот такое:

Сигнал с генератора вычищен полосовым фильтром с подавлением 90+ дБ. Пробовал лабораторный источник питания и схему с линейным стабилизатором, разницы не увидел.

Усилок сам по себе дифференциальный, поэтому измеряю с балунами на входе и выходе (запаяны на самой плате изначально)

Откуда может быть такая разница? Может кто-то уже имел дело с данным усилителем? Больше 40 дБ ума не приложу как набежало

-

При создании футпринта можно воспользоваться слоем Component Value, я думаю

-

34 минуты назад, falling_stone сказал:

Извините, вопрос, возможно, не в тему, а можно ли вместо пьедестала использовать теардроп? По идее, пьедестал уменьшает импеданс линии, на последнем участке перед подключением к виа, теардроп должен делать то же самое.

Ну тирдроп это скорее про технологичность, потому что это небольшой участок, но в целом ход мыслей правильный.

На практике вот так предметно не поясню и графиков не приведу, но видел чужой проект, на 10 ГБит, кажется, где делали почти под прямым углом уширение линии раза в три. Внутри антипада. И вроде как всё успешно работает

Можете ещё глянуть у Интела AN766, кажется. Там были рассуждения на тему, да и в целом полезный документ

-

30 минут назад, EvilWrecker сказал:

Теперь понятно -а отличить потом влияние фанаута и антипада от остального сможете?

Вообще я планирую просто все насквозь промерить, из того же ADS получить S-параметры платы-переходника и попробовать их вычесть из измерений. В Матлабе, например. На максимально достоверные параметры не претендую, но получить графики, близкие к даташиту, будет успехом.

34 минуты назад, EvilWrecker сказал:А есть в более крупном масштабе? Какой размер отверстия/пада, антипада и трассы

Антипад 1,2

-

18 минут назад, EvilWrecker сказал:

Обмер кабеля? Ничего не понял, можно подробнее и что там отыгрывают выступы?

Ну есть, например, скоростной кабель от Samtec. В даташите графики есть, а S-параметров нет. Соответственно берем векторный анализатор, делаем плату для тестов с разъемами, и измеряем.

Выступ я рассматриваю тупо как опорный слой, который не режется антипадом, и по логике как раз импеданс будет получше. Какие там уже начинаются отношения между падом и телом переходного, и на что будет влиять ширина пада - понятия не имею, слава численным методам.

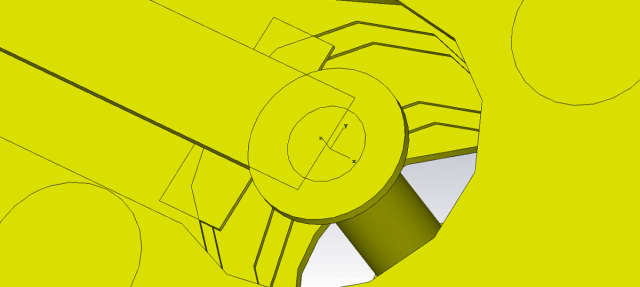

24 минуты назад, EvilWrecker сказал:Что касается графиков- вы можете показать саму геометрии антипада с трассами, в изометрии?

Их есть у меня

26 минут назад, EvilWrecker сказал:Метод прост донельзя- грубо говоря, считается пад с учетом только земляных плейнов, на других слоях условно нет меди и начинаете подгонять антипад. Когда числа получены хорошие, делаете уже антипад на других слоях и смотрите с какого расстояния начнется влияние на ранее полученные результаты, далее выбираете нужный запас и в общем-то все

Метод научного тыка, де факто. Рисуем параметрическое 3D и пущай его колбасит в разные стороны

-

1 час назад, EvilWrecker сказал:

И заметно разницу с и без выступа? Я таких случаев для 10гбит еще не встречал

А есть пример?

А есть пример?

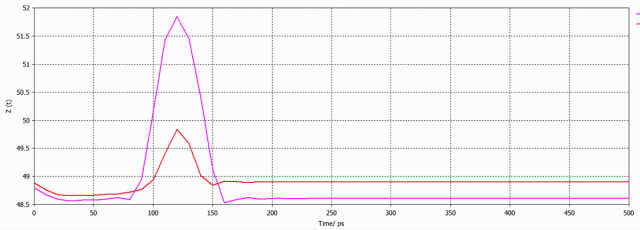

Для задачи обмера High-Speed кабеля очень даже кстати. И для СВЧ линий в SE формате тоже, собственно вот ее графики

Красные графики - с пьедесталом.

Не совсем соответствует Интеловскому аппноуту, но там и задача другая решается.

1 час назад, EvilWrecker сказал:Самый дубовый из стартовых примеров- есть поверье, что на полигонах питания надо резать антипады не просто сильно, а с числами типа 2мм(причем в произвольном дизайне), что конечно же неправда ни разу. Зато можно сделать антипад таким как надо- не раздутым и не слишком малым, практически прозрачным- что хорошо как с точки зрения маржи по отклонению импеденса как такового, так и занимаемого места на плате, тем более если это непосредственно около разъемов или около/под бга.

А какой-нибудь ресурс на тему есть? Было бы любопытно почитать, потому что тот же Интел говорит как раз по крупные антипады.

41 минуту назад, def_rain сказал:Быстрый вопрос:

Как продублировать дорожку которая идет от одного thru pin до другого thru pin на разных слоях ?

PCB Editor не дает этого сделать, он просто перерисовывает эту дорожку удаляя её с предыдущего слоя.

PS Делать с помощью shape не предлагать.

Спасибо!

А скопировать сегменты трассировки с помощью snap vertex и snap to pin не получается? Так же проверьте галку Replace Etch

-

45 минут назад, EvilWrecker сказал:

В ViaDesigner от ADS хоть и нет этого, но далее это все при наличии желания можно сделать в Layout. Но мне интересно- вы для каких скоростей считаете это?

Обычно закладываемся на 10 ГБит

47 минут назад, EvilWrecker сказал:Почему в принципе?Не какие-то, а самые что ни на есть важнейшие.

Если S-параметры в порядке, то TDR, на мой взгляд, не обязателен

-

7 минут назад, Flood сказал:

Спасибо за отклик! Измерительные порты подключаются непосредственно к переходной структуре, или к дорожкам на некотором расстоянии от него?

безусловно какую-то длину диффпары надо отрисовать, по крайней мере так точно будет видна корректная структура поля и для тополога так очевиднее

9 минут назад, Flood сказал:Результатом моделирования являются S-параметры структуры? Можно ли получить TDR-график, показывающий место изменения импеданса, или это не особо полезно?

да, в первую очередь S-параметры. TDR можно получить постобработкой S-параметров или еще отдельно сделать монитор, но это долго. в принципе по TDR можно какие-то косяки увидеть

12 минут назад, Flood сказал:Можно пример, о чем речь?

-

7 минут назад, Flood сказал:

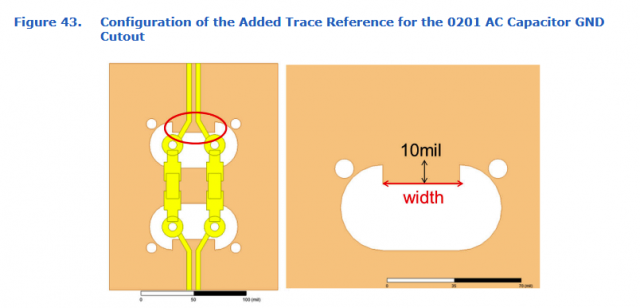

Подскажите по более простой ситуации: в чем можно промоделировать следующие высокоскоростные структуры, а также какие модели для этого нужны:

- переходные на дифф. паре с общим антипадом;

- вырезы под проходным конденсатором/парой конденсаторов;

- вырезы под SMD пинами разъема, антипады вокруг TH пинов разъема.

Понимаю, что ответов более одного, особенно насчет применяемого софта. Хотел бы услышать мнения тех, кто реально это моделирует, а не просто знает по рекламе, что это делается в SystemSI.

Особенно интересно, есть ли решения с параметризуемыми размерами геометрии падов / антипадов / вырезов для оптимизационного поиска?

В принципе есть в ADS и HyperLynx для дифф пар инструменты расчета, можно условно прикинуть что куда. Но там все +- стандартно, и, например, опорный пьедестал в антипаде не сделать.

Я подобные вещи рисую в CST, но это может быть не самой простой работой с точки зрения 3D, если мало опыта

Вырезы тоже там же можно рисовать, в принципе

-

40 минут назад, Zurabob сказал:

сли частота сигнала более 2ГГц, то простая IBIS модель источника сигнала не подойдет.

Желательно будет достать модель с эквализацией канала. (нужны будут AMI блоки управления формой сигнала)

И хорошо, если будет толковое описание по настройке AMI блоков...

Если хотя бы чего то не будет, то о достоверности результатов можете забыть.

Ну тут вроде как не ставится вопрос целостности сигнала, по крайней мере явно. Выше вроде была речь чисто про S-параметры, а это можно сделать в ADS, например, достаточно просто

-

21 час назад, Карлсон сказал:

Пробовал делать правила для зазора пина с определенной цепью - приходится слишком много ошибок гасить, неудобно. Хочется автоматизации.

Вряд ли есть какой-то конкретный инструмент для этого, сделать пин шейпом - как минимум странно, ведь тогда он должен наследовать все свойства класса шейп. В голову приходит два варианта - статик шейп на весь пин или регион.

-

13 минут назад, Alexbewon сказал:

Подскажите, каким образом в проекте посмотреть, используется ли BackDrill?

В Nc - > Backdrill Setup посмотрите, например

-

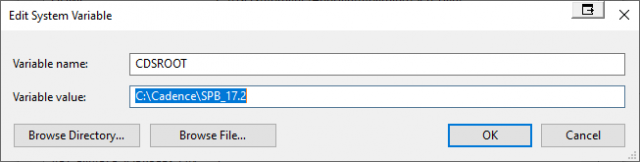

давайте просто прямой путь напишем в path

C:\Cadence\SPB_17.2\tools\bin\

-

и с установленной CDSROOT получается сделать смену директории? или опять The system cannot find the path specified?

-

руками можете найти файл allegro.exe? по какому пути он лежит?

CDSROOT в системных переменных создали?

-

-

3 минуты назад, Roman53 сказал:

c:\>cd %CDSROOT%\tools\bin

The system cannot find the path specified.Значит, проверяйте наличие переменной %CDSROOT%

Если ее нет - добавляйте. Она должна вести к корневому каталогу установки, например C:\Cadence\SPB_16.6

-

1 минуту назад, Roman53 сказал:

нет, cd перед %CDSROOT% у меня нет, надо написать?

Вы не поняли, это надо написать в командной строке, cmd.exe

cd - команда смены директории

-

давайте поверим корректность пути, который прописали

в командную строку "cd %CDSROOT%\tools\bin"

если откроется нужный адрес - проблема не в пути

Вопросы по Agilent ADS

в RF & Microwave Design

Опубликовано · Пожаловаться

Коллеги, добрый день! Кто-то пишет обработку результатов схематика на AEL? Не могу понять, как сформировать структуру данных такого типа, как на скрине, чтобы вектора могли быть разной длины (irregular)

list не подходит, по нему неудобно итеррировать. Пробовал сделать копию исходных данных и там переписать вектор - получаю ошибку, потому что размеры разные (в результате обработки количество точек изменяется)