Alex Shirokov

Участник-

Постов

18 -

Зарегистрирован

-

Посещение

Весь контент Alex Shirokov

-

Interrupts GPIO Raspberry Pi 3

Alex Shirokov ответил Alex Shirokov тема в Raspberry Pi

То есть все GPIO могут быть прерываниями? -

Interrupts GPIO Raspberry Pi 3

Alex Shirokov опубликовал тема в Raspberry Pi

Подскажите пожалуйста какие GPIO разъема являются прерываниями? -

DDR2 в три слоя

Alex Shirokov ответил kappafrom тема в Работаем с трассировкой

Ряда 4 в сумме да, но у вас разводка в общем 2 по 2 на слой,и опять же несопоставимо большое расстояние от проца до планки- а в плане выравнивания это ключевой момент влияющий на сложность. Что касается приведенного скриншота- а можете разводку показать? Разводка там к сожалению не в 3 слоя, ибо в 2011 году делалась и тогда опыта еще было мало. В любом случае разводка по площади сильно выйдет за габариты чипа. -

DDR2 в три слоя

Alex Shirokov ответил kappafrom тема в Работаем с трассировкой

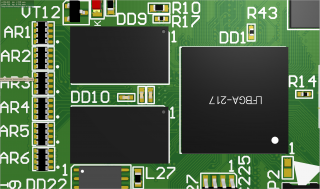

Да, линии 0.075 из за процессора. Вообще DDR занимает 4 ряда процессора, да и чипов 2. Думаю при наличии всего одного чипа разводка сильно упрощается. Вообще был опыт разводки DDR2 на очень близком расстоянии от процессора. Это возможно. Тут 2 чипа MT47H256M8, в сумме как у ТСа получается. -

DDR2 в три слоя

Alex Shirokov ответил kappafrom тема в Работаем с трассировкой

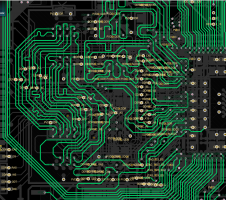

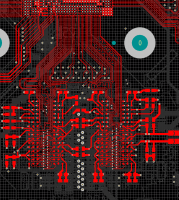

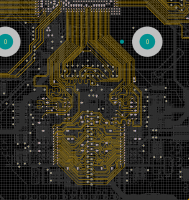

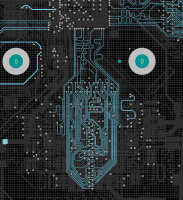

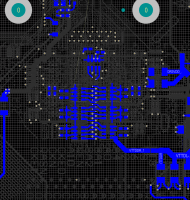

Но тут над понимать что вы используете микровиа и судя по всему погребенные отверстия в staggered конфигурации, а у ТС переходные обычные.. И места у вас гораздо больше чем у него. И пинаут удобнее. Насчет отверстий согласен, есть и глухие и скрытые, но от них частично или полностью можно избавится если делать отверстия в пинах. Насчет места и пинаута не соглашусь, так как разводка от процессора с шагом 0.5мм. У ПЛИС гибкости больше в данном случае. На картинках длинна шин данных 30 мм, адресных 50 мм. -

DDR2 в три слоя

Alex Shirokov ответил kappafrom тема в Работаем с трассировкой

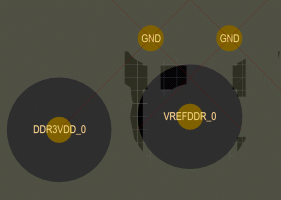

Здравствуйте. Мне удалось развести 16-битный чип в 3-х слоях + 4-й слой под терминирование. Разводка деревом. Собственно вот: Если интересно, могу пояснить, что куда. Терминирование считаю обязательным, но тогда в 3-х слоях 16-ти битный чип развести сложно. -

BGA корпус с шагом 0,5 мм

Alex Shirokov ответил ViKo тема в Работаем с трассировкой

Можно в первом ряду сделать площадки овальными. У тех плат что я делал были следующие характеристики по первому ряду: 1) Площадка 0.3*0.275, маска 0.075, протаскивается проводник 0.075 мм, переходные микроотверстия 0.1*0.3 с маской 0.075 (плата 2011-го года) 2) Площадка 0.25*0.25, маска 0.06, протаскивается проводник 0.075 мм, переходные микроотверстия 0.1*0.275 с маской 0.075 (более поздние платы) Изготавливались на китайской фабрике, в России вроде нет такого производства. На самом деле так себе совет. На месте выброшенных контактных площадок будет маска, которая выше площадок. Шарики микросхемы упрутся в маску, что приведет к непропаю. Тогда уж шарики с BGA-шки тоже убирать нужно. -

Здравствуйте! Если в правилах случайно установить Plane Clearance = 0, то будет КЗ со всеми отверстиями по всему Plane и при Short-Circuit Constraint (Allowed=No) это КЗ при DRC анализе не отслеживается. КЗ в Plane можно как то отследить?

-

С LGA и BGA корпусами так не получится, если ключей на корпусе нет. А у мобильных процессоров я такого не встречал. Да и проблема может быть в самом процессоре (брак).

-

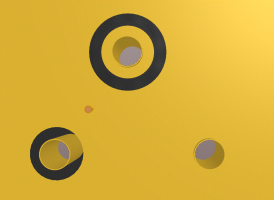

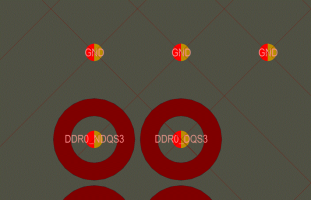

Извиняюсь, похоже со второй картинкой я всех запутал. На ней просто хотел показать отсутствие ободка в Plane. Попробую обрисовать ситуацию еще раз: На данной картинке мы видим слой Plane (в 3D режиме) подключенный к VDD, и 3 отверстия. То что справа, подключено к VDD с правилом Direct Connect. Отверстия слева и сверху подключены к GND. Левое не имеет ободка - это проблема которую я хочу решить. Верхнее обведено кольцом в слое Plane, то есть физически вырезан кружок меди с отверстием по центру. Этот кружок подключен к цепи GND, и как видно на картинке образует площадку - то, что нужно. Но этот способ очень кривой. Есть ли нормальный способ это реализовать? P.S. Вопрос касается конкретно реализации металлического ободка в слое Plane у отверстия не имеющего электрического соединения с этим слоем. Если такой возможности нет, то так и напишите :).

-

Спасибо. Интересная информация.

-

В моем случае материнскую плату разрабатываю я, и схему защиты реализую непосредственно на плате. А в вашем случае изменение сопротивления IO покажет КЗ по Ядру процессора?

-

Если кратко, то как реализовать картинку 1 настройками Алтиума, а не колечком нарисованным вручную?

-

Для наглядности пара картинок: Это площадка сделанная на костыле в виде колечка. Внурти кольца площадка подключена к линии. А так получается по умолчанию. P.S. Еще не освоился с инструментарием форума, так что могут быть ляпы

-

Металлизированный ободок отверстия в Plane

Alex Shirokov опубликовал тема в Altium Designer, DXP, Protel

Здравствуйте! Суть проблемы: В негативном слое Plane отверстия не имеют металлического ободка, и я не могу найти где такой ободок можно задать. В Rules-PlaneClearance задается только зазор от металлизации до отверстия. Для чего такой ободок нужен: Имеется плата с глухими лазерными отверстиями структурой: Top - Plane1 - Mid1-... , где Plane1 является опорным слоем для ВЧ линий на слоях Top и Mid1, то есть без него никак. Отверстия возможны только лазерные, ибо для BGA с шагом 0.5 мм и ниже. При препрегах толщиной в районе 0.75 мм нужно сделать стек из 2-х лазерных отверстий с Top на Plane1 и с Plane1 на Mid1, а площадки для этого на Plane1 нет, что выливается в проблемы с производством платы. Да, конечно можно вместо Plane использовать обычный сигнальный слой и заливать все полигоном, либо в слое Plane рисовать вокруг каждого такого отверстия колечко, но может есть более простой вариант? -

Варианты защиты от КЗ на плате

Alex Shirokov опубликовал тема в Цифровые схемы, высокоскоростные ЦС

Добрый день! Итак задача: Имеем материнскую плату с сокетом под процессор. Процессор может быть вставлен не по ключу, и возникнет КЗ. Нужно реализовать защиту от такого КЗ. Варианты: 1) Самовосстанавливающийся предохранитель. - В моем случае не подходит, так как возможен нагрев платы свыше 70 градусов. 2) Использовать специальные микросхемы типа TPS25921. - Но тут возникает вопрос, что делать с напряжениями диапазона 0.65В - 2В? Мне не удалось найти, но может есть в природе? 3) Схема на транзисторах. - По мне слишком много элементов, хотелось бы что то более элегантное. 4) Связка АЦП+ПЛИС, которая мониторит уровни напряжения на резисторах для замера тока (0.05 Ом в разрыв цепи питания) и выключает DC-DC в случае сильной просадки. Так как у меня на плате есть ПЛИС (питается независимо от процессора) со свободными IO, решил остановиться на этом варианте. Тут возникает вопрос, хватит ли скорости АЦП+ПЛИС, чтобы вырубить DC-DC до выгорания схем? Что думаете по данным вариантам защиты от КЗ? Какие еще есть способы? -

Если компоненты мелкие то проще самому нарисовать. А по остальным обращайтесь в техподдержку фирмы производителя, саппорты вам пришлют библиотеку