vit0099

Новичок-

Постов

10 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйПосетители профиля

198 просмотров профиля

-

Спасибо, тоже вариант, буду благодарен за более подробную информацию об утилите что Вы говорите. Речь идет наверное о C2Prog.exe ?

-

Так на нормальной плате как раз и висит ресет в воздухе, а супервизор стоит получается без толку. Они раньше ставили на эти платы супервизоры и подключали их нормально, и соответственно а тут решили супервизор поставить, но не подключили. У них такое бывает. Это не проблема, я прошивал ранее версии с супервизорами, для этого нужно на плату подать все питания чтобы он сработал или линию ресета разъединить чтобы супервизор в низком состоянии ресет не удерживал. Тут или я туплю или сани не едут)))) Думал о таком варианте, но это будет уже крайняя мера, если что)

-

Насколько смог, сравнил) В плате, которая прошивается китайцы поставили супервизор питания, не плате несколько питаний, и супервизор должен держать в состоянии сброса (в низком состоянии) проц пока все питания не сформируются и не стабилизируются. Но китайцы, остаются китайцами, они поставили супервизор, но его выход не подключили к ресету XRS 80pin. Ресет просто висит в воздухе. На плате которая не инициализируется JTAG, ресет XRS 80pin подключен через резистор 390Ом на питание 1.8В. Я пробовал снять этот резистор и пробовал через резистор на 4.3кОм подключить XRS к питанию 3.3В. Результата не дало. У меня одна уже только мысль осталась, что процессор залочен и отрабатывает protected ECSL area

-

Посмотрел, на общем ресете XRS, на обеих платах постоянно висит высокий уровень. У меня вот какая мысль в голову пришла, а может на этих платах, которые не получается подключить к JTAG контроллеры залочены? Вообще если подключать залоченый проц по JTAG, то обычно подключение инициализируется, но не дает прочитать защищённые области памяти, но может в этом случае не доходит до работы с TAP контроллером, в виду того что XDS100V3 требуется некоторое время, чтобы взять под контроль процессор. В это время ЦП начнет работать и может выполнить инструкцию, которая осуществляет доступ к защищенной области ECSL. Если это произойдет, ECSL отключится и приводит к разрыву соединения отладки JTAG. Вот из даташита: When initially debugging a device with the password locations in flash programmed (that is, secured), the JTAG debug probe takes some time to take control of the CPU. During this time, the CPU will start running and may execute an instruction that performs an access to a protected ECSL area. If this happens, the ECSL will trip and cause the JTAG debug probe connection to be cut. Two solutions to this problem exist: 1. The first is to use the Wait-In-Reset emulation mode, which will hold the device in reset until the JTAG debug probe takes control. The JTAG debug probe must support this mode for this option. 2. The second option is to use the “Branch to check boot mode” boot option. This will sit in a loop and continuously poll the boot mode select pins. The user can select this boot mode and then exit this mode once the JTAG debug probe is connected by re-mapping the PC to another address or by changing the boot mode selection pin to the desired boot mode Буду смотреть, есть ли у XDS100V3 режим Wait-In-Reset, ибо второй метод для меня вообще не понятен)

-

да, совершенно верно, есть пару плат одной модификации, они прошиваются без проблем и пару плат другой модификации, которые не могу прошить, т.к. jtag в ошибку уходит. Статика не вариант, тут с платами что-то не то. похоже что китайцы или по интерфейсу чего-то намудрили, хотя вроде все звонится одинаково, или чего-то другое. Сейчас смотрю что там на общем ресете XRS

-

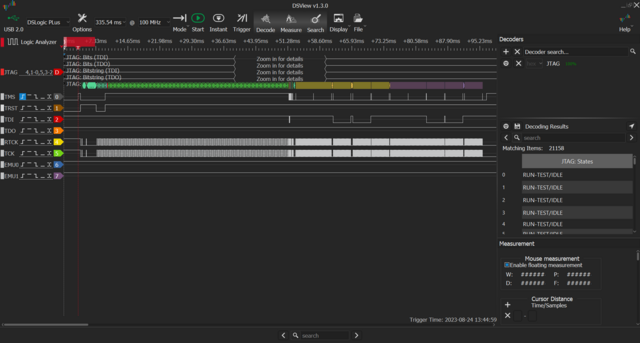

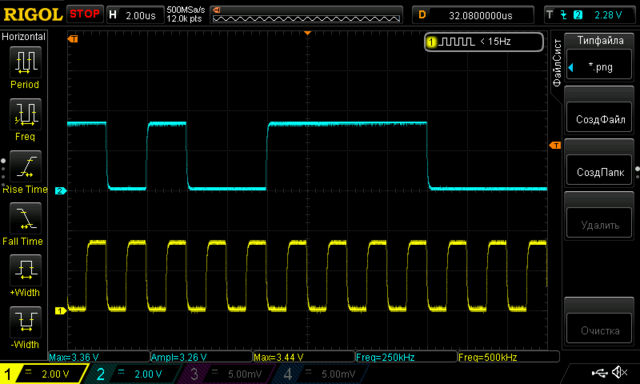

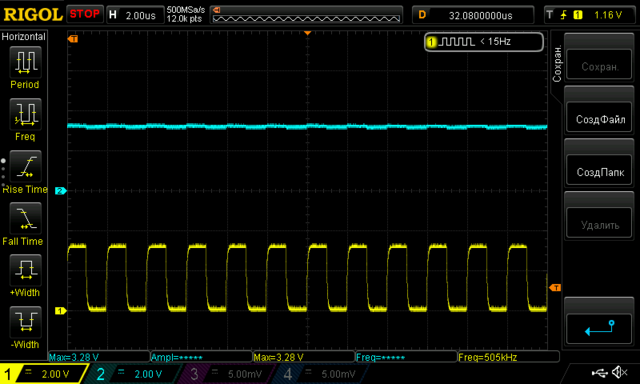

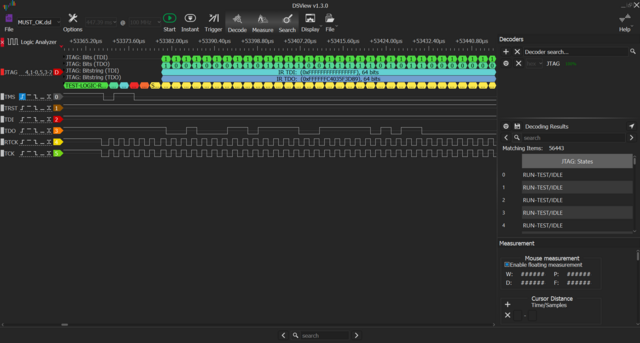

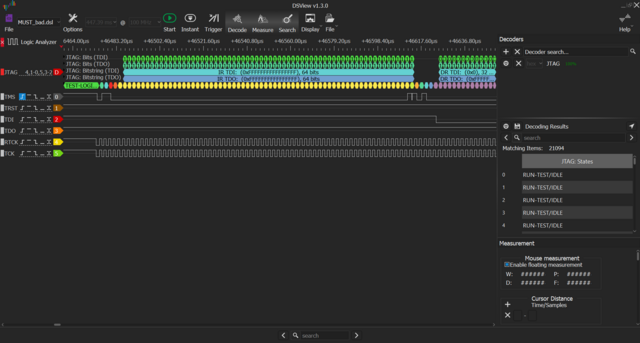

Вот еще скрины, первый нормальная плата, второй проблемная, тут уже развертку сделал побольше чтобы видно было что происходит с TRST На самих платах TRST нет подтяжки на землю резистором, как в даташите к TMS320F28335 нарисовано, ну а в единицу TRST тянет уже сам программатор XDS100V3

-

Спасибо. Да по контактам уже крутил по всякому, платы нормальные, заводские. Прграмматор JTAG XDS100V3 подключен шлефом к стандартному разъему на 14pin на плате под JTAG Также посередине этого шлейфа дополнительные разъем стоит с выводами на анализатор. Анализатор точно все адекватно считывает.

-

Вот скриншоты сигналов на осциллографе, желтый луч TCK, синий луч TDO Первая картинка с платы которая нормально общается по JTAG, вторая картинка тот тип платы которая не общается, на TDO постоянно активный уровень висит, и даже не пытается ни разу перейти на низкий уровень И TDO - 77 пин у микроконтроллера не универсальный, используется только для JTAG scan out, test data output, т.е. его никак нельзя сконфигурировать регистрами под что-либо другое. И самое интересно, что если сравнивать с рабочей платой, по логическому анализатору то все что касается TRST, TCK, TMS, все происходит абсолютно одинаково, до того момента пока мы на рабочей получаем ответ по TDO, а на не рабочей постоянно активный уровень и все. В обеих типах плат TDO прозванивается по сопротивлению относительно земли, питания, абсолютно одинаково, и в режиме прозвонки полупроводника также. И при чем это не одна плата. Прошил несколько плат одной модификации и также не могу прошить несколько плат другой модификации.

-

Спасибо за ответ! Платы заводские, 2-х типов исполнения, так вот один тип прошивается, а второй нет. Там нету никаких проблем (с большой долей вероятности) с контактами или еще с чем-то подобным. Все сигнальные линии прозванивал от JTAG разъема на плате до ножек микроконтроллера. Оба типа платы одинаково все звонится и проблем с этим я не вижу. Конечно проверял, прозванивал перед тем как вопросы на форуме задавать.

-

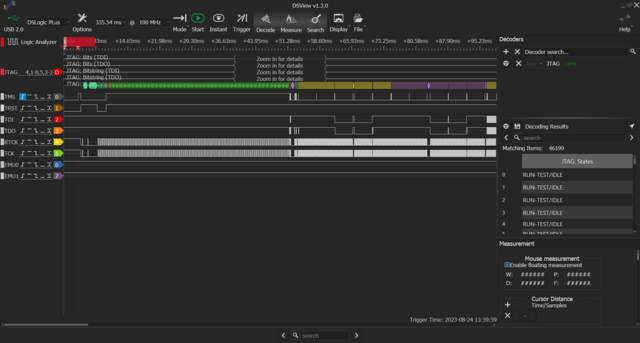

Доброго времени суток! Нуждаюсь в помощи коллективного разума) Есть несколько плат с TMS320F28335 прошиваю через JTAG XDS100V3 Часть прошил без проблем, часть не получается, JTAG при ресете вываливается в ошибку: Error connecting to the target: (Error -233 @ 0x0) The JTAG IR and DR scan-paths cannot circulate bits. Посмотрел анализатором, со всеми сигналами все норм, а вот по TDO не получаем ответа, похоже как TDO постоянно висит в Z состоянии. Если померять вольтметром на всех платах на выводе TDO висит от половины питания 1.5В висит (анализатор у меня от 1.1В уже показывает этот уровень как лог. 1) Так вот на рабочей плате по команде на выводе TMS контроллер переходит в состояние SHIFT_IR выдает наружу через TDO значение 0xFFFFFFC4035F3D89 А вот на той, плате что не ресетится по TDO ничего не получаем, вторая картинка. С контактами до пина TDO контроллера все хорошо. Не кто не сталкивался что это может быть, куда копать? Картинки прилагаю Спасибо!