Hirer

Участник-

Постов

33 -

Зарегистрирован

-

Посещение

Весь контент Hirer

-

Иженер-программист по ПЛИС, Санкт-Петербург

Hirer ответил OKKONS тема в Предлагаю работу

"К административной ответственности может быть привлечено любое лицо или организация, распространяющие информацию о вакансиях, в которой содержатся ограничения дискриминационного характера. Если подобные уточнения появятся в тексте объявления о вакансии, штраф для граждан составит от 500 рублей до 1 тысячи рублей, для индивидуальных предпринимателей – от 3 тысяч до 5 тысяч рублей, для юридических лиц – от 10 тысяч до 15 тысяч." © -

"... Но сейчас другой период Течет на стыках Иногда хлещет Вы видимо встречали команды где все валят др на др - железячники на программеров нижнего уровня те на системщиков и все вместе на аналитиков которые формировали ТЗ ... Поэтому я предпочитаю 80% проекта держать в своих руках Хотя мозг не резиновый получается эффективней ... " © Это точно !

-

Узнавал у технолога - нет проблем. Объединят в один слой паяльной маски сколько нужно герберов. DipTrace в минус почему-то не делает, хотя в строке редактирования ошибку не выдает. Пришлось менять параметры via (0.75 мм поставил) а потом экспорт в гербер. Все получилось.

-

"Скока вешать в граммах ?" © :) "Немного" по рекомендациям Е.Бегер "Паяльная маска" "... Размер выреза в паяльной маске должен быть на 100–150 мкм больше размера контактной площадки (то есть расстояние от края контактной площадки до края паяльной маски должно лежать в пределе от 50 мкм до 75 мкм). Такие значения связаны с точностью совмещения внешних слоев платы с паяльной маской, которая обычно составляет 50–75 мкм, в зависимости от технологических возможностей производителя ..." © Про переходные отверстия таких рекомендаций не встречал. Заглянул в DipTrace-Export-Gerber - там отдельных опций для Via нет. Есть один общий параметр - "Solder Mask Swell". Как вариант - выводит два гербера TopMask_Pads и TopMask_Via с ожиданием, что производитель их соединит у себя в одно целое.

-

Суть рекомендации - использовать более мелкие переходные отверстия и как следствие - повышать класс изготовления ПП ?

-

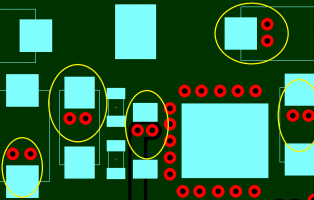

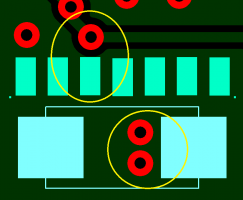

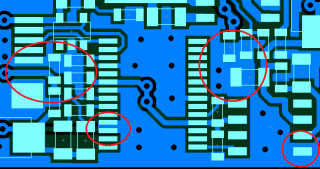

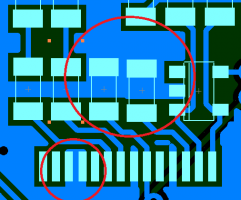

Еще один вопрос, касающийся паяльной маски. Расстояние между переходным отверстием под компонентом и контактной площадкой равно 0.28-0.31 мм (в разных местах по разному. см. фото). Разработчик требует открытой переходки и обязательное наличие паяльной маски в этом зазоре. Переписывался с технологами из двух контор которые занимаются производством ПП, ответ примерно один : «Про мостики из маски, пример: 2 Медных площадки 1,5*1,0мм, находятся друг против друга по длинной стороне. Масочное вскрытие для них 1,7*1,2мм. Если расстояние "красная линия " больше или равно 0,1мм - будет мостик из маски. В подобных местах мы делаем масочное вскрытие 1,6*1,1м если заказчик просит. Никаких мостиков из маски на окружностях мы не гарантируем. Только приведённый мною пример.» Как быть в этом случае ? История начинается с присланной платы :

-

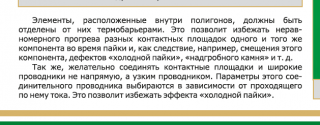

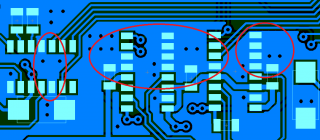

"На SMD-падах они излишни, если предполагается пайка в печи" © т.е. вот эту рекомендацию я могу смело игнорировать ? (пайка в печи - ключевое) ... попалось при поиске на электрониксе - Термобарьеры и требования IPC + ДЕФФЕКТ ПАЙКИ – ПОДНЯТИЕ КОМПОНЕНТА КАК ИЗБЕЖАТЬ ЕГО ИЛИ УМЕНЬШИТЬ? "... Неравномерность оплавления, как правило, бывает связана с неправильной конструкцией платы (например, с различной теплоемкостью площадок, если не выполнены корректные термобарьеры) ... " ©

-

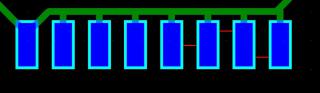

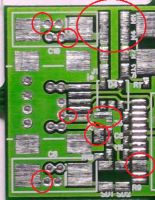

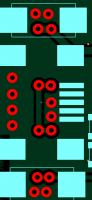

Доброе утро ! Решил проконсультироваться у людей которые профессионально занимаются разработкой печатных плат. Есть масса информации от учебных материалов до лаконичных рекомендаций производителей печатных плат и тех кто занимается контрактной сборкой. А есть исполнители которые всей этой информацией пренебрегают. Пока остановлюсь на двух моментах : 1. Расположение контактных площадок на залитых полигонах без термобарьеров. 2. Соединение соседних ножек микросхем кратчайшим путем или полигоном - ключевые моменты обвел красным, хотя думаю этого и не требовалось. Теперь суть вопроса. Какова цена вышеупомянутых рекомендаций и какие последствия их несоблюдения можно получить в итоге ? Есть ли вероятность, что автор фрагментов выше — настоящий профессионал и мне не о чем волноваться ? Как вы оцениваете этот справочник ? Справочник инженера-разработчика Еще вопрос из области «где должен закончиться разработчик ПП» ? Поясню ... Человек работает в DiрТrace. Когда приходят готовые платы говорит, что сделано очень плохо и для аргументации показывает экран с увеличенным фрагментом ПП. «Вот тут должна быть паяльная маска !». Замеряю зазор от переходного до контактной площадки. Получается 0.2 мм. На мое замечание, что в настройках «Export-Gegber-Solder Mask Swell» стоит параметр 0.102 мм получаю ответ, что он всегда делает = 0 и вообще — герберы это работа технологов производителя, а не его работа. Еще один аргумент из его арсенала - «Раньше все приходило как надо». «Раньше» - это заказ в «Таберу» с передачей PCAD-файла. Нынешние заказы проходят через Микролит-Резонит. Дополню свой вопрос ... Что такого страшного в гербер-файлах, что у разработчика даже не возникает желания экспортировать все слои и подстраховаться просмотром в каком-нибудь независимом вьювере. Я лично использую GC-Prevue ™ for Windows. На мой взгляд — человек пытается таким образом дистанцироваться от полной ответственности за результат. Всегда можно открыть «идеальный» проект в САПР и сказать - «смотрите, тут все хорошо».

-

Чтобы более полно проконсультироваться на форуме по конкретным вопросам сделал ветку в "Печатные платы (PCB) > Работаем с трассировкой > Примеры плат" - "Вопреки рекомендациям от производителей ..." Тема проектирования ПП в настоящий момент на первом месте. Разумеется это только план. Более того, "заполняя" первые 6 пунктов, начинаю все больше и больше испытывать желание сделать все самому. Новый человек тянет за собой вопросы по минимизации рисков. Если я сам могу заставить работать себя сколько нужно для достижения результата и с нужным качеством, то стороннего работника - вряд ли.

-

Хотелось бы уточнить, что именно там нереально ?

-

Доброе утро ! Страна у нас большая разброс в уровнях трат-зарплат еще больше. Есть и официальная точка зрения Зарплаты 2016 Цена разработки - есть компромиссное решение обоих сторон. Это - главное. Договорились - пожали руки. Заложили даже 15% аварийный запас сверху. С моей стороны все было выполнено. Сейчас работаю над детальным ТЗ на новый проект. Скелет примерно такой : 1 Общие сведения. Плановые сроки начала и окончания работ. 2 Назначение и цели проектирования "___" 3 Состав "___" 4 Требования функциональные и специальные (в т.ч. - инф. безопасность) 5 Технические характеристики. 6 Состав и содержание работ по проектированию "___". 7 Состав и содержание работ по реализации и вводу "___" в действие. 8 Требования к документированию. Состав разрабатываемых документов. 9 Порядок контроля и приемки. 10 Нормальные условия эксплуатации. Требования к квалификации персонала. 11 Календарный план. 12 Допущения и ограничения 13 Риски 14 Глоссарий (словарь терминов и определений)

-

Согласен ! :) У вас получилось лаконично. У меня эмоции вмешались - "доколе ..." Только я понял, что это фотографии после нанесения паяльной пасты до пайки ( и не смещение, а криво приложенный трафарет ) И мне было совершенно неясно где именно непротрав с непромывом ... Вот фрагмент одной платы из партии ...

-

Добрый день ! Тут нарисовалось небольшое продолжение истории. Пришли новые печатные платы. Они производят монтаж. И присылают по почте фотографии с претензией - "платы некачественно сделаны", "непромыв и непротрав" © Мне просто любопытно - я один все это не вижу ? Я так понимаю, лучше перед передачей ПП - все их обозначить и "поименно" сфотографировать ? После пайки сложно что-то доказывать. Попутно возник еще один вопрос - переходные отверстия закрывать маской или нет ? Они утверждают, что плата с закрытыми паяльной маской переходными отверстиями больше года не живет и они снова ничего не гарантируют. Как бороться с такими утверждениями ? 100 штук плат перезаказать - не вопрос. Вопрос - так ли это на самом деле ? Перелистав кучу форумов, лишний раз убедился - сколько людей, столько и мнений.

-

Там графика. С обратной стороны - сплошная заливка. Еще раз повторюсь - это плата совсем иного назначения.

-

В точку.

-

Нет. Это вторая плата, не имеющая к rfid никакого отношения. Рабочие токи - единицы миллиампер. Практически статика.

-

Кстати, говоря о пользе сторонних специалистов - пришлось их привлекать и платы все же переделывать. Картинки вниз скину. Исходный "дизайн" в виде усов электронщик назвал "экраном" и на исправленную версию всерьез обиделся. Это так. Но ТЗ детального не было (к сожалению).

-

Все же думаю "не пофигу". В данном случае важнее опыт или же чувство ответственности. Они кстати почти вдвое по возрасту отличаются ... Нет, не угадали :) - старше электронщик. Отчеты - это "не их религия". Так и не убедил программиста сделать детальное логирование в десктоп-приложении для последующего анализа. Золотые слова !

-

Оптимально и надежно, но - дорого ! :) Отнюдь - я сам по себе "пара". И электроника и программирование. Но раздвоением личности не страдаю :)

-

Я это понимаю. Следующий проект учтет все замечания и рекомендации этой ветки.

-

Это я еще интерфейс его десктоп-приложения не показал :) (служебная тайна)

-

картинка выше - из PCAD, да. Но разводил в Альтиуме. Соглашусь с Вами, особенно - про тетрадь. Самый четкий и наглядный индикатор "деятельности". К сожалению исполнителей выбирал не я лично. Именно так. Определен был только финал. Так ведь взрослые люди :). А программист даже что-то преподает. Наверное это действительно правильное решение. Я подумаю, спасибо.

-

Я наверное не совсем корректно выразился. Редактируется конечно. Но все соединения - наборы отрезков приставленных друг к другу. Где гарантия, что после редакции ничего не сдвинется. Повторюсь - DRC не работает в этом случае, т.е. гарантий никаких. Конденсаторы на кварц тоже не ставят. Аргумент тот же - "и так работает".

-

ДВОЕ ИЗ ЛАРЦА

Hirer опубликовал тема в Общение заказчиков и потребителей электронных разработок

Добрый день ! Хочется спросить совета у форумчан по одному вопросу, хотя не совсем уверен, что выбранная тема четко соотносится с ним. Я — заказчик. Проект небольшой – ATmega168 + PCF7991, пара реле, пара ключей и десяток входных сигналов (логика). На выходе должен появится работающий образец в предфинальном варианте для запуска в серию + вся исходная информация. Исполнителей двое, электронщик и программист. С каждым из них - своя история взаимодействия. При отправке ПП на изготовление выяснилось, что все проводники на плате были сделаны не трассой а графикой (линии), которые естественно нормальному редактированию не поддавались. При увеличении была заметна небрежность — нахлесты, несведение в точку и т.п. Ну и апофеозом всего — невозможность автоматической проверки корректности дизайна платы в контексте правил разводки (DRC ). На мой вопрос «почему так» было сказано, что Altium в котором он работал с очень ограниченной лицензией и по другому никак ... Потратив несколько часов на обзор и вникание в имеющейся доступный софт, был сделан выбор в пользу DipTrace. Цена вопроса - 10 тыс.р (1000 выводов, 4 слоя). Плата была переделана в приемлемый срок и с надлежащим качеством. Пре передаче в Резонит выяснилось, что теперь формат DipTrace в качестве входного не принимается. На мое указание транслировать проект в гербер и сверловку, электронщик заявляет, что это работа технолога и ничего в этом случае гарантировать не может. Пришлось делать самому, заняло примерно пять минут с проверкой полученных герберов сторонним вьювером. Из Резонита все пришло как задумывалось и без вопросов. Программист ... Тут сложнее — ломаный IAR. Попытка разговора в стиле «ай-яй-яй, а давай делать в Atmel Studio» (4.18 например) не привела ни к чему. Хотя изначально было сказано, что проект будет развиваться и необходим грамотный и качественный подход к проектированию и железа и софта. Ну Си он и в Африке Си, махнул на это рукой, запланировав по окончанию этой фазы переехать в студию за короткое время. Наконец пришло время тестирования полученного образца. Детали описывать не стану. Выяснилось, что устройство при провалах питания ведет себя непредсказуемо, но чаще всего намертво «зависает». Посовещавшись пару дней и проводя какие-то эксперименты ими было заявлено, что это «плохие» микроконтроллеры ... - Не вопрос, - сказал я и приобрел с десяток ATmega168 из разных мест и партий. Снова испытания и проверки, но — безуспешно. На мой вопрос «а включен ли внутренный BOD?» было бодро ответили - «пробовали по всякому, ничего не помогает» и предложили - «а давайте на вход по питания поставим отсечку», чтобы ниже 8 вольт устройство просто отключалось. Время поджимало — снова махнул рукой (зря) ... Прошло несколько дней на протяжении который электронщик как в старые добрые времена СЮТов взяв в руки паяльник плодил вариант за вариантом схему, приговаривая «вот уже почти ...» Делать мне было нечего и я взялся чтение классики и истоков. Изучив варианты построения схемотехники UVLO (under voltage lock out) и внимательно почитав datasheet на микроконтроллер решил взять инициативу в свои руки ... На моем рабочем столе помимо компьютера разместились : опытный образец, программатор, паяльная станция и лабораторный источник питания. Получив по запросу от программиста исходный код и прошивку (IAR я не устанавливал) взялся за тщательную проверку всего и вся. Собственно все заняло минут десять. За это время я убедился, что fuse bits прошиты мягко говоря странным образом. На вопрос «Это правильно?» был четкий ответ - «Да ! У нас так все устройства работают». Пришлось распечатать нужные страницы даташита и попросить пояснить наглядно. Случился таймаут по окончании которого мне было выдано две разные версии с новыми комбинациями и «пояснениями» в стиле «а можно и вот так» ... Я пригласил грамотного специалиста который мне шепотом сообщил, что ошибка на самом деле на генетическом уровне. Им же аргументировано объяснил, что все не так, как они себе представляли и нужно просто вдумчиво читать документацию, т.к. там все-все написано. Закончив объяснения он запрограммировал fuse bits как нужно. Устройство перестало себя вести неадекватно на что программист заявил, что он — программист а не железячник и эти конфигурационные биты не его проблемы. Электронщик в ответ показал пальцем на программиста ... Еще не занавес. Напоследок я потратил пару часов на анализ исходного кода (лучше бы я это не делал). Вновь не стану описывать увиденное. Сообщу только одну деталь (программная реализация SPI – это мелочи) — сбросов watchdog-а я насчитал целых 70 ! ... На высказанное мое недоумение был ответ «Ну работает же!» © Занавес ... А теперь собственно суть вопроса. Как при наличии двух исполнителей найти ответственного за косяк и доказать, что это именно он а не другой ? Каким образом добиться от программиста качественного программного кода ? P.S. Спасибо за терпение, проявленное при прочтении текста выше :) -

Тестовое устройство для электродвигателя

Hirer ответил Hirer тема в Предлагаю работу

Личка на форуме уже работает. Ваше сообщение получил.