def_rain

Свой-

Постов

315 -

Зарегистрирован

-

Посещение

Весь контент def_rain

-

Спасибо! Это именно то что мне было нужно. У меня есть еще один вопрос. Допустим на готовой плате есть Символ (компонент) с уже выравненным и установленном в нужном месте(свободном месте) RefDes и ключом. В процессе выясняется что у этого символа нужно поменять step модель или изменить графику на слое assembly. Делаю данные изменения в библиотечном dra файле, затем на плате update symbol - reset symbol text location and size для этого символа. Однако после Апдейта сбивается положение RefDes. Меня интересует способ как сделать апдейт без изменении шелкографии RefDes? Особенно этот момент становится проблематичным если плата уже готова, сделаны гербера шелкографии. Получается что изменения step модели, которая по идее не как не должна влиять на топологию платы, сбивает шелкографию и гербер уже не соответствует плате в brd.

-

А где находится этот Suppress shapes less than: xxx ? Поискал у себя в OrCad PCB Designer Prof и не нашел... Это User Preferences наверное?

-

Здравствуйте, товарищи. Мне нужен совет по следующему вопросу: Есть полигон земли на топе, он частично вырезается остальной топологией на этом же слое, получается весь изрезаный полигон. Не подключенные к Нету островки удаляю с помощью Delete Unconnected Copper. Но все равно есть совершенно бесполезные обрывки полигона, которые не нужны, но при этом не являются Unconnected Copper и соответствующим инструментом их не удалить (см.фото). Меня интересует быстрый способ как убрать эти бесполезные "полуостровки". Можно конечно в этом месте сделать вырез в полигоне так, чтобы он перекрыл эти полуостровки, но может есть какой то специальный инструмент для этого.

-

Спасибо, теперь разобрался. А как нибудь можно сопоставить их к одному общему?

-

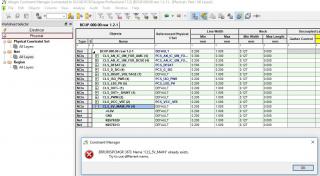

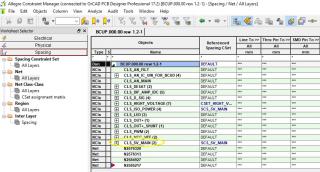

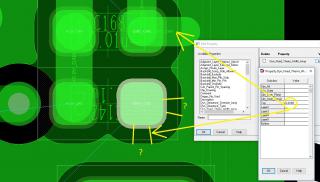

Может быть кто нибудь сталкивался с такой проблемой: Пытаюсь переименовать Класс в Physical CM, допустим CLS_5V_MAIN_PH в CLS_5V_MAIN при этом выдается ошибка что класс с таким именем уже существует. Хотя на самом деле в списке классов Physical его нет(см.рис 1). Однако этот класс есть в списке в списке классов Spacing(см.рис 2). Как такое может быть, ведь наборы Классов для ограничений Physical и Spacing должны быть общие? Т.е. как я понимаю я должен видеть одни и те же Классы как в ограничениях для Physical, так и для Spacing, а в моем случае, получается что в Physical одни Классы, а в Spacin другие... Помогите разобраться. Рис.1 Рис.2

-

Как раз и у меня есть вопрос по Lite версии. У нас несколько плавающих лицензии OrCad PCB Designer Pro. При запуске PCB Designer-а нельзя выбрать Lite версию как один из тип лицензий, его нет в списке доступных. Пробовали как то даже отдельно Lite ставить, ничего так и не получилось. Суть в том что иногда бывают маленькие платки для которых и Лайт версии хватит(чтобы не занимать полноценную лицензию), но у нас почему то не работает вместе с остальными лицензиями.

-

Да, так и сделано. Есть такая положительная практика. Ресет здесь как общий пример рассматривался. Но все равно спасибо.

-

А ведь и в правду, очень похоже на антенну получается. Длинный проводник с конец в воздухе.

-

Расположение подтягивающего резистора на плате

def_rain опубликовал тема в Работаем с трассировкой

Здравствуйте. Микроконтроллер имеет входа, выхода которые по умолчанию должны иметь определенный уровень H или L, в зависимости от ситуации. Этот уровень по умолчанию задается подтяжкой 4.7кОм. В процессе работы и выполнения программы эта подтяжка может быть перетянута в противоположный уровень, допустим из H(уровень по умолчанию) в L. Хочу более детально разобраться где и почему лучше располагать подтягивающие резисторы на плате для входов и выходов микроконтроллера? По данному вопросу я рассуждаю следующим образом: 1. Допустим есть ножка RST микроконтроллера,для него это Вход(I). Этот вывод RST подключен к разъему для программатора, ножка RST программатора это соответственно Выход(О). По умолчанию RST должен быть подтянут к H (через 4.7кОм) чтобы не поймать какую нибудь наводку, которая может привести к нештатному Ресету. Данную подтяжку к Н (4.7кОм) можно расположить либо у самого МК, либо у разъема для программирования. У меня есть предположение, что подтяжку лучше расположить максимально близко к выводу RST микроконтроллера. Наверно это будет лучше для помехоустойчивости, т.к. непосредственно сама ножка МК подтягивается к нужному уровню. 2. Так же есть и обратная ситуация, когда вывод МК является Выходом(О). В данном случае, мне кажется что лучше подтяжку расположить ближе уже не возле МК, а возле приемника. Получается что вся длинна дорожки нагружена, лучше для помехоустойчивости. Есть ли вообще смысл в этом? И где можно почитать более подробно? Спасибо. -

В итоге сделал задуманное с помощью CSET assignment matrix, заранее создав для этих двух нетов отдельный класс и комбинируя применение Сетов в матрице.

-

Там немного другая ситуация. Мне нужно настроить индивидуальное правило не для одного Нета, а чтобы это было индивидуальное правило для двух нетов сразу в одном классе. Что я имею в виду: В предложенном Вами решении я получу ситуацию что тот Net(допустим N11111) для которого я настрою правило зазора на уровне Net Level (допустим shape to shape=3mm) будет иметь зазор до полигонов всех других Нетов равный 3мм. А мне нужно чтобы N11111 имел зазор для всех других Нетов равный 6мм, а конкретно для одного Нета (допустим N22222) расстояние равное 3мм. При этом оба Нета (N11111, N22222) относятся к одному классу. Я даже не знаю, возможно ли такое вообще. Как буд то бы класс в классе получается или в классе есть подкласс и у этого подкласса свой собственный Spacing Constraints Set... Как мог объяснил

-

Меленький вопросик. В ConstraintManager-е настроил ограничения, но есть один момент который не пойму как сделать. На плате net-ы выполнены полигонами. net-ы собраны в Классы. Есть Spacing Constraints Set который применяю к этим классам. Меня интересует ограничение между полигонами Shape to Shape, допустим установил 6мм. Но в одном классе есть два net-а, которые должны иметь расстояние между своими полигонами не 6мм, а 3мм. Хотя относительно всех остальных в данном классе Shape to Shape должно оставаться 6мм. Другими словами, два Нета, принадлежащие одному Классу должны иметь расстояние между друг-другом отличающееся по сравнению с остальными Нетами этого же класса. Т.е. исключение для двух конкретных Нетов.

-

Да, это вполне рабочий вариант. Так можно сделать! Просто интересно еще с этим св-вом разобраться...

-

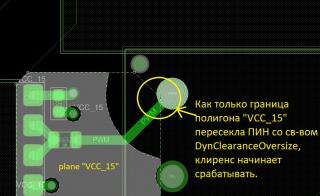

Нет, не помогает. Единственное что помогает, это когда полигон в котором должен быть сделан клиренс пересечет (или полностью закроет) пин для которого настроена функция DYN_CLEARANCE_OVERSIZE ARRAY. Но такой глюк не со всеми полигонами. С теми у которых все в порядки я пробовал копировать на место глюченых (с заменой net-a) и этот глюк проявлялся и у них. Это говорит о том что дело не в настройках конкретного полигона.

-

Я это пробовал, тоже не помогает. Стоит по умолчанию режим Smooth. Перестает вырезать в полигонах отступы если в настройках динамического полигона выбрать Disable. Так что вопрос открыт...

-

Пробовал, не помогло... Здесь не понял о чем речь, уточните, пожалуйста. Верно. Это я для примера показал, в этом месте и не обязателен такой отступ. Просто на плате есть вывода thru pin для разъемов с напряжением до 1кВ. Вот как раз там нежен большой отступ от всего. PS Я в своем первом посте снизу сделал приписку с еще обнаруженными нюансами этого глюка.

-

Здравствуйте. Ситуация следующая: Есть компонент с выводом thru pin. Этот вывод подключается с помощью дорожки. Нужно сделать отступ от него всех полигонов с другими net-ами во всех слоях. Чтобы в радиусе 4 мм не было ничего. Как я понимаю это св-во DYN_CLEARANCE_OVERSIZE_ARRAY. Применяю его к нужному выводу компонента (вывод PWM на фото). В итоге какие то полигоны сделали отступ от пина, а какие то нет. См. фото 1 Вот что интересно, те полигоны которые не сделали отступ(не сработало св-во DYN_CLEARANCE_OVERSIZE), начинают реагировать и подчиняться этому св-ву только в том случае если граница этого полигона начинает пересекать контактную площадку(вывод), для которой я установил DYN_CLEARANCE_OVERSIZE. Меня это не устраивает. См. фото 2 Кто нибудь может объяснить в чем проблема? Вот еще что было мною замечено: 1. Данный глюк присутствует на всех полигонах и на выводах любого компонента. Это не глюк какого то конкретно вывода или полигона. 2. если компонент для пина которого которого заглючило это св-во (клиренс) немного подвинуть командой move (хоть на сотую миллиметра), то клиренс до полигона у этого пина сразу работает как нужно. Т.е. св-во начинает работать. 3 Однако, если даже св-во и начало работать(для конкретного полигона, после того как я подвигал компонент), стоить хоть немного отредактировать этот полигон и Клиренс для пина снова начинает глючить. Т.е. можно сделать вывод как будто Клиренс не обновляется для полигона.

-

У нас тоже на тех компах на которых прошло большое обновление Вин10 стали тормозить иконки при прорисовке.

-

Прочитайте здесь как я решил проблему с 3Д моделями: https://electronix.ru/forum/index.php?showtopic=143763

-

Да, наверно так и есть! Что то я не обратил внимание на это...

-

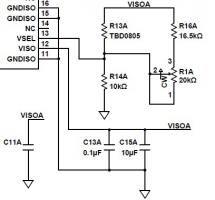

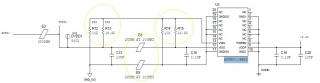

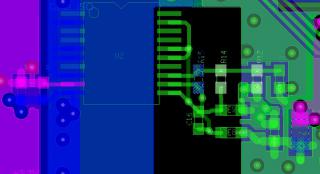

ADUM5010 EvalBoard вопрос по схеме

def_rain опубликовал тема в Цифровые схемы, высокоскоростные ЦС

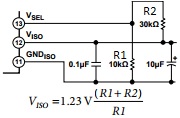

Здравствуйте. Есть изолированный DC/DC преобразователь ADUM5010ARSZ. Он сделан по технологии isoPower и iCoupler 2.5кВ. Напряжение на его изолированном выходе задается делителем от 3.15 V to 5.25 V. Из Datasheet: Есть еще отдельно Evaluation Board User Guide UG-487 для этого ADUM5010,в котором стоит подстроечный резистор для ручной регулировки Viso. Однако я наткнулся еще на одну схему, где этот делитель зачем то дублируется два раза, разделенный ферритовыми бусинами. Это схема для EVAL-CN0376-SDPZ. Если посмотреть трассировку этой платы, там сделан сшивающий конденсатор по технологии перекрытия опорных полигонов первичной и вторичной(изолированной) стороны. Ферриты Е8 и Е9 разделяют грязную землю и питание ADUM5010 от основных полигонов GND и VDD. Не могу понять в чем здесь смысл делать два одинаковых делителя разделенных ферритами (выделил желтым на схеме)? -

В некоторых случаях это поможет. Но это костыль получается, какие то площадки ортогонально, какие то диагонально... Интересно докопаться до сути проблемы, понять возможно ли регулировать как то этот нахлёст? По фото видно, что перемычкам не обязательно так глубоко в полигон заходить, там еще приличное расстояние от края полигона до начала скругления кончиков перемычек.

-

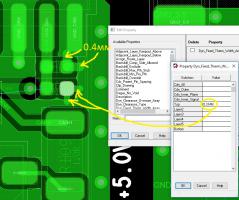

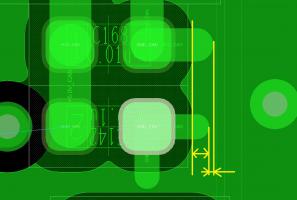

Здравствуйте. Ситуация следующая: На плате TOP залит полигоном земли, к этому полигону нужно подключить с помощью терморельефа земляную площадку SMD 0402 конденсатора. Перемычки делаю толщиной 0.4мм. Однако, есть проблема с нижним конденсатором C142 (см.фото1), из-за того что толщина перемычки довольно большая, он не может подключиться к узенькому перешейку земляного полигона между R109 и самим C142(см.фото2). В Аллегро есть такой нюанс, что чем толще перемычка термобарьера, тем больше для нее должен быть нахлест на соответствующий полигон(см.фото2). Но в моем случае перешеек узкий и для того чтобы терморельеф нормально подключился приходится уменьшать толщину перемычки свойством Dyn_Fixed_Therm_Width_Array до значения 0.3мм(см.фото2). Подскажите, пожалуйста, может быть есть какой то способ контролировать нахлёст перемычки терморельефа на полигон? Чтобы я смог подключить перемычку 0.4мм к узкому перешейку. На фото 3 показал разницу в нахлесте между перемычкой 0.3 и 0.4мм Фото1 Фото2 Фото3 PS Тип подключения Full contact не рассматриваю, интересует как сделать на терморельефе.

-

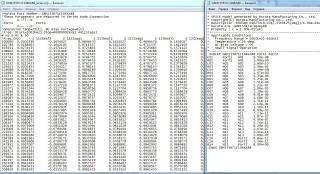

А вы этот файлик как то сгенерировали? Это выглядит как библиотека из четырех конденсаторов. У меня немного другая ситуация... S параметры к конденсаторам, резисторам и индуктивности я могу подключить, т.к. это стандартные библиотечные компоненты для Сигрити. Делаю это так: Допустим есть конденсатор для которого есть только S-параметры. В Project Library - Add Model - заполняю в ручную параметры для данного конденсатора в соответствии с даташит (см. фото выделил желтым строку с этими параметрами). Далее, Edit SPACE... - в открывшемся окне Edit Circuit Definition нажимаю Import snp - выбираю файлик *.s2p S параметры добавляются в Definition в виде дополнительной строки с моделью и путём к неё (см.фото, выделил эту строку желтым) Теперь эту модель можно подключить к конденсатору через Browse Model. Не уверен в правильности этого способа... Поправьте если что. Однако в моем случае нужно прикрепить S параметры к ферритовой бусинке. Вот это я не понимаю... Как Вы сказали, можно сделать не на уровне библиотеке а сразу в Definition - через Edit Правильно ли я понял, что для этого мне нужно в Definition просто указать путь к файлу *.s2p для данной ферритовой бусины ? И после этого можно считать что s параметры подключены к бусине?

-

Спасибо за ответ, Вы мне помогли! 1. Вы имеете в виду чтобы номер вывода в модели компонента в столбце Ckt Node соответствовал номеру вывода в столбце Layout Node самой трассировке (cм. фото)? На фото я стрелочками показал это место. То о чем вы пишете проверяется здесь? Позвольте еще задать вопросы... 2. Я имею конденсатор, для него существуют S-параметры файл .s2p, но по мимо этого еще есть как я понимаю SPICE модель (.mod). На фото ниже соответственно слева и справа открыл их в блакноте. Скажите какие модели в каком случае применять? 3. Допустим, я имею только s-параметры, как их подключить к компоненту? Если просто скопировать содержимое файла в Definition компонента, то Сигрити выдает ошибку по каждой строчке. Просто так S- параметры не переваривает. Содержимое в S-параметрах намного больше чем содержимое SPICE модели(если открыть блакнотом). Однако, S параметры можно подключить к компоненту, если делать это через Project Library (Assign - Browse Model). ПРи этом Definition выглядит как на фото ниже. Видно, что указывается путь где расположен файл s параметров. Но не понятно что здесь значат остальные цифры и обязательны ли они? S1 1 2 3 2 Model="C:\Cadence\Sigrity2017\share\library\decap library\Murata_Spara\Murata_Ceramic_Capacitors_Spara\GRM155R71C104KA88_series.s2p" V 3 2 0 Может Вы подскажите?