emerg_reanimator

Свой-

Постов

67 -

Зарегистрирован

-

Посещение

Весь контент emerg_reanimator

-

Infineon SOCRATES PEB22622

emerg_reanimator ответил emerg_reanimator тема в Компоненты

Инфинеон большая компания котороя любит больших заказчиков (хотя есть исключения). Чип не рекомендуеться потому, что счетверённый рекомендуеться. Вообще идея неплохая 1) девайс получится дешевле, 2) трассировка проще, но только на многослойке, 3) .bis поддерживается и по двум парам может работать. Что касается документации, то во-первых это конъюктура на рынке, во-вторых документацию легче поддерживать. А вообще в этой компании всё засекречено. Как впрочем и в большенстве подобных гигантов. -

SDE tools

emerg_reanimator опубликовал тема в MIPS

Добрыь день Некоторое время назад попытался собрать SDE toolchain, но после нескольких неудачных попыток я бросил эту затейю. Необходимость сборки обусловлена наличием определённых ошибок в компиляторе (точнее в DSP extension), с которыми можно жить, но есть желание их исправить. Кому нибудь удалось собрать toolchain? -

Если фильтр с передаточной функцией H(z)=B(z)/A(z) - минимально-фазовый, то фильтр H(z)=A(z)/B(z) устойчив. Если корни B(z) лежат на единичной окружности, то мы получим генератор. Условие минимальной-фазности: http://sepwww.stanford.edu/sep/prof/pvi/zp...tml/node26.html

-

1. Все правильно, но для типичных аппроксимаций (Батт., Чебышев, Золоторёв) модуль нулей ЧХ равен 1. Поэтому как ни крути, нули всегда на единичной окружности. 2. Я нашёл объснение тому, что АЧХ фильтра непоменяется, если использовать обратные нули: H(z) = H'(z)*(1+z0/z)*(z0+1/z)/(z0+1/z) H(z) = H'(z)*H1(z)*(1+(1/z0)/z), где H1(z) - фазовое звено 1-ого порядка, модуль АЧХ которого равен 1. Вопрос: Как из обычно эллиптического фильтра получить минимально-фазный?

-

Рекурсивные КИХ фильтры

emerg_reanimator опубликовал тема в Алгоритмы ЦОС (DSP)

Добрыь день, уважаемые коллеги Будте добры, поделитесь информациеё о рекурсивных фильтрах с конечной импульсной хар.-кой. Ни в классической литературе, ни в глобольной сети обилия разработойк в этой области я не нашёл. Мне показалось, что теория РКИХ фильтров ещё не достаточно развита по сравнению с традиционными разделами ЦОС. После продолжительных блужданий в сети я нашёл несколько ссылок на ИИЭР (IEEE) и АСНИиЭ. Спасибо! -

Firmware Developer (Infineon, Riga)

emerg_reanimator опубликовал тема в Предлагаю работу

Contact me for more information -

Спасибо за ответы Решение с фазовращающими звеньями обычно не оптимально. Хотя наверное могут быть варианты. Я таких не знаю. Кроме того, ГВЗ в этом случае увеличется. Уважаемый, SM, могли бы Вы по подробнее расказать о методике отображения нулей.

-

Миниизация ГВЗ для БИХ

emerg_reanimator опубликовал тема в Алгоритмы ЦОС (DSP)

Добрыь день! Интереснует, кто занима-лся/ется такой задачей и какие подходы для её решения уже существуют. Спасибо! -

ethernet на avr

emerg_reanimator ответил siriasis тема в AVR

Добрый день Простите меня уважаемым siriasis. Но у меня складывается впечатление, что вы себя поиском в сети и на фтп особо не утруждали ;) Инетерсно, для каких целей вы собираетесь использовать АВР + АиПи? Какая требуется пропускная способность? См. приложение. avr460_incomplete.part1.rar avr460_incomplete.part2.rar avr460_incomplete.part3.rar avr460_incomplete.part4.rar AVR_Ethernet.part1.rar AVR_Ethernet.part2.rar AVR_Ethernet.part3.rar -

Спасибо, проверю :)

-

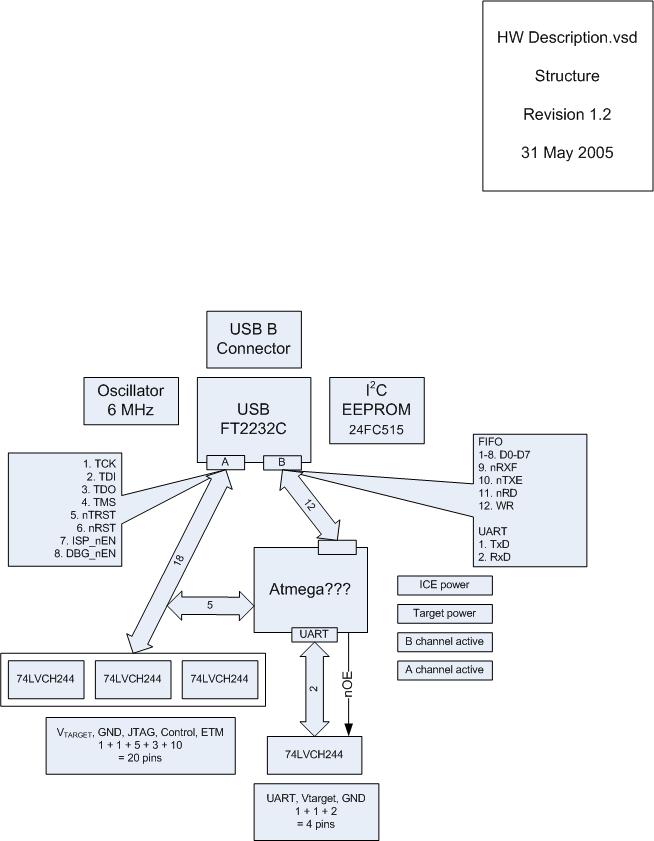

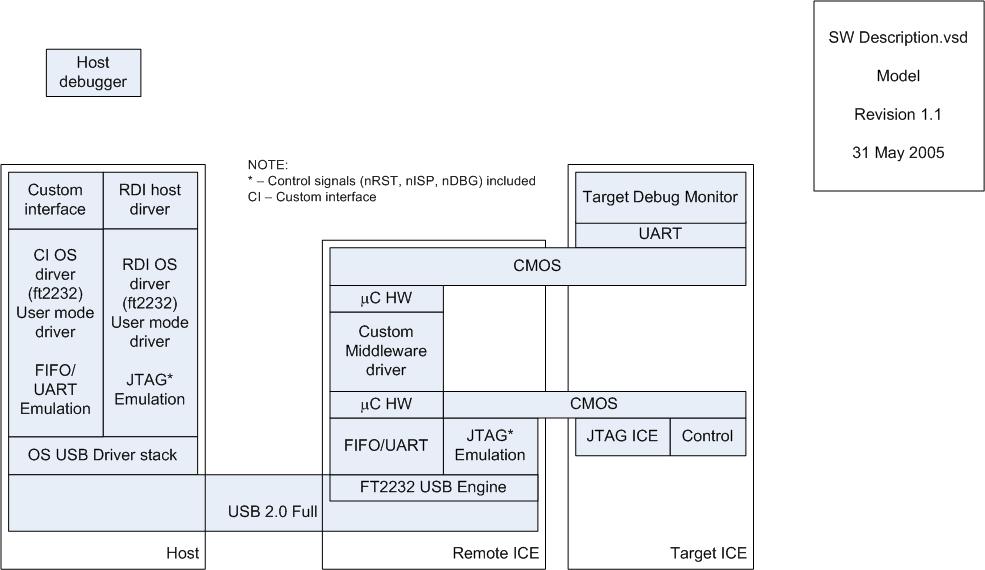

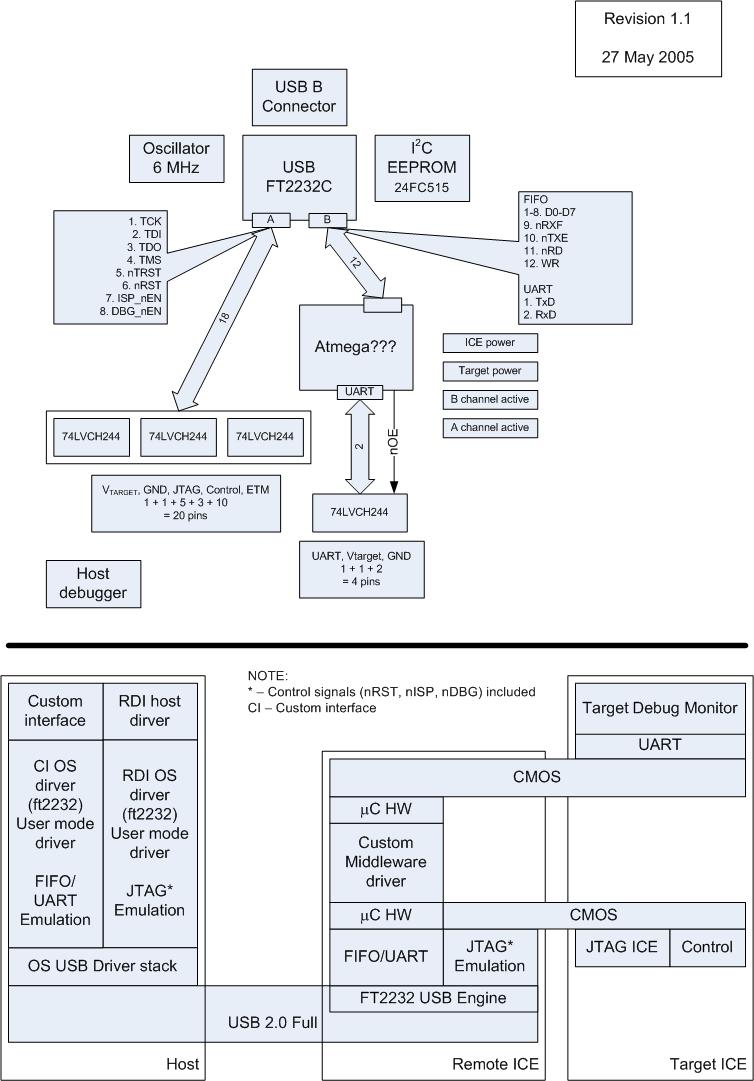

Быстрй USB JTAG интерфейс

emerg_reanimator ответил Dainis тема в ARM

Добрый день, уважаемые 1. Проект отрытый (OpenSource, GPL) 1. FTDI выбран из-за наличия дров к ниму. Если есть дрова для предлогаемого ЦПУ, можно подумать. Иначе, самому дрова писать - гиблое дело. А на счёт цены, я бы сказал, что торг здесь неуместен :) 2. ЦПУ нужен, если необходимо организовать интелектуальный обмен между хостом и целевым устройством. (например для организации универсального интерефеса с встраиваемым монитором типа IAR ROM-monitor). ЦПУ добавляет большей гибкости. 3. Что требуется поменять в схеме для совместимости с другими ЦПУ (AVR, MSP430)? Как применить это устройство для конфигурации ПЛМ, я не знаю. Скорее всего совместимость определяется на уровне EDA. Потэтому я рекоммендую пока оставить эту задачу. Для начала задача минимум: Разработать адаптер для отладки ЦПУ АРМ через ДжТаГ с программным интерфейсом RDI. Для этого надо собраться компании в человек (5-10), распределить обязаности, начать работать. У кого есть желание и возмжности - пишити прямо. Могу и хочу (вакансии в посте от May 27 2005, 14:19). -

ARM7 вопрос

emerg_reanimator ответил emerg_reanimator тема в ARM

Я не совсем правильно описал проблему. Отладка с использованием внутрисхемного эмулятора проходит норамально (тоесть я могу смотреть состояние регистров, делать пошаговае выполнение и т.п., но после того как я ознакомился с содержанием регистров КП, ЦПУ не воспринимает прерывания хотя выполнение инструкций продолжается). Я думаю это скрое связано с самим ЦПУ нежели с отладчиком. Надо попрбывать что-нибудь подобное в другой среде. -

ARM7 вопрос

emerg_reanimator ответил emerg_reanimator тема в ARM

Именно так уважаемый d__ Не инициализировался стэк в режиме System. После добавления инициализации ситуация исчезла. Но обнаружилась другая фича. Под IAR 3.21a на Olimex LPC E2124 пытается крутится uCOS-II 2.76 + uCOS-View 1.10. Помаргивает диодами до момента пока я не открываю в отладчике C-spy окошко с регистрами контроллера прерываний (КП, VIC). После этого дейтвия, прерывания ЦПУ игнорируются (прерывания в ЦПУ разрешены, флаг готовности в регистре статуса КП установлен). Установленны два прерывания от TIMER0 и UART0. -

Быстрй USB JTAG интерфейс

emerg_reanimator ответил Dainis тема в ARM

Добрый всем день Я смотрю что тема уже созрела. Так может того... Потянем сами проект Я предлагаю такую структуру. Необходимо: Техническая часть 1. Найти описание RDI (1.5.1, 1.5.2). Реализацию можно подсмтреть в GNU gdb-server. 2. Разработать интерфейс общения с встроенным монитором (за базу можно взать Ангел!а) 3. Подготовить ТЗ для ПО для хоста, адаптера. 4. Выбрать Мегу. Организационная 1. Найти энтузиастов для - Разработка хост дров (1-3 человека) - Разработка мидлвареза (1-2 человека) - Создания схемы и платы (1-2 человека) - Документация (1-3 человека) Итого: 4 человека за 3-4 месяца 10 человек за 1-2 месяца Жду коментарии, предлжения и критику -

Вопросы по схеме Wiggler'а

emerg_reanimator ответил Xarann тема в ARM

1. Я немогу сказать точно, что этот сигнал означает, но я его подтягиваю к питанию. 2. Если имеются ввиду транзисторы и т.д., то я их не установил. Хотя сброс ингода нужен. 3. Мой адаптер заработал с 4.20а (я так понимаю, что эта версия изобилует различными фичами и в том числе большим количеством багов), после того как соединил на LPT 8 и 15 выводы. Можно посмотреть схему баньяна. http://armdebug.27h.com/Doc/softmanual.zip Там больше пояснений. -

ARM7 вопрос

emerg_reanimator ответил emerg_reanimator тема в ARM

Точно! Вспомнил. В описании на LPC2124 тоже указывается в каких ситуациях ЦПУ попадает в это исключения. Но вопрос возник по другому поводу. На Olimex LPC E2124 происходит ошибочное измениение указателя стэка. ... OSStartHighRdy MSR CPSR_cxsf,#0xDF ; Switch to SYS mode with IRQ and FIQ disabled BL OSTaskSwHook ; OSTaskSwHook(); ... После выполнения инструкции загрузки CPSR происходит обновление R14(SP). В стэк записывается значение адресса который указывает на несуществующую область памяти. И в итоге я попдаю в исключение по данным. Такая ситуация происходит когда ЦПУ не нагрелся до рабочей температуры :) -

ARM7 вопрос

emerg_reanimator опубликовал тема в ARM

Добрый день Подскажите при каких условиях ЦПУ попдает в этот режим? Углубление в описание на архитектуру (DDI0210B ARM7TDMI Rev.4) ясности не прибавило. -

EWARM 4.20a отладка с Wiggler

emerg_reanimator ответил emerg_reanimator тема в ARM

Прерывание одно. Но дело скорее всего в среде разработки. Потому как под 3.21а работает без проблем и с двумя прерыванями. Прадва грузится по Wiggler-у немного медленее. -

EWARM 4.20a отладка с Wiggler

emerg_reanimator опубликовал тема в ARM

Добрый день! Ситуация: ewarm-4.20a + wiggler. Отлаживаю uCOS-II для Olimex LPC E2124 . В случае, если ОС запускается из флэш - таймер тикает. Когда отлаживаюсь из C-spy один раз срабатывает прерывание от таймера0 и прерывание не сбрасывается. Вот код обработчика: void Tmr_TickISR_Handler (void) { T0IR = 0xFF; /* Clear timer #0 interrupt */ OSTimeTick(); /* If the interrupt is from the tick source, call OSTimeTick() */ #ifdef DEBUG_IAR_SIM_EN VICVectAddr = (INT32U)Tmr_TickISR_Handler; #else VICVectAddr = 0; /* */ #endif } Код настройки таймера: void Tmr_TickInit (void) { /* VIC TIMER #0 Initialization */ VICIntSelect &= ~(1 << VIC_TIMER0); /* Enable interrupts */ VICVectAddr2 = (INT32U)Tmr_TickISR_Handler; /* Set the vector address */ #ifdef DEBUG_IAR_SIM_EN VICVectAddr = (INT32U)Tmr_TickISR_Handler; // Simulate VIC #endif VICVectCntl2 = 0x20 | VIC_TIMER0; /* Enable vectored interrupts */ VICIntEnable = (1 << VIC_TIMER0); /* Enable Interrupts */ T0TCR = 0; /* Disable timer 0. */ T0PC = 0; /* Prescaler is set to no division. */ T0MR0 = CPU_PERIPHERAL_CLK_FREQ / OS_TICKS_PER_SEC; /* Count up to this value. */ T0MCR = 3; /* Reset and interrupt on MR0 (match register 0). */ T0CCR = 0; /* Capture is disabled. */ T0EMR = 0; /* No external match output. */ T0TCR = 1; /* Enable timer 0 */ } В чём жучок? -

Речь идёт о инициализации стэка в режиме прерывания (IRQ mode). Для каждого из семи режимов определяется указатель стэка. Определние происходит в файле сstartup.s79 (для ИАРовской оболочки). Размер стэка задаётся в файле конфигурации компановщика (*.xcl). А базовый адрес сегмента (IRQ_STACK) определяется самим компановщиком. Я так понимаю. Вопрос: Как узнать базовый адрес сегмента?

-

uCOS-II Initialization

emerg_reanimator опубликовал тема в Операционные системы

Добрый день Не могу найти как в ОС инициализируется стэк. Особенно интересно в контексте портирования OSView для ARM. Переменные OSIntStkSize, OSIntStkBase в исходниках отсутствуют. P.S. Если у вас вдруг имеется оглавление книги "μC/OS, The Real-Time Kernel", не сочтите за труд поделится :) Немного разобравшись понял, что стэк инициализируется в библиотеке времения выполнения (библ ВВ). Но появился другой вопрос. Я использую библ ВВ от IAR. Расположение сегментов определяется в соответсвующем xcl-файле. Размер стэка указывается явно, а как задаётся базовый адресс стэка (в данном случае для режима прерывания). -

LPC-2214 + uC/OS-II - VIC problem!

emerg_reanimator ответил Domnitch тема в ARM

Не могу себя назвать знатоком в практическом примении этой ОС и процессора, но теоретико-логическом плане определённые знания имеются. Мне почему-то подумалось вот, что: Такая ситуация может возникнуть на процессорах LPC в момент когда перырвания запрещаются (Spurious interrupts). Периферия обнаруживает прерывания и посылает запрос на обработку прерываний к ядру. Но в этот момент ядро выполняет команду запрета прерывания. После выполнения этой команды, прерывания обрабатываеться и вашем случае передаётся управление контроллеру прерываний. А так как прерывания запрещены, то контроллер не может определить источник прерываний и возвращает нулевой адрес обработчика прерываний. Насколько я помню, в микроКОСе таки прерывания обрабатываются заглушками (DummyInterrupt Handlers, если я не ошибаюсь). И система никак не фиксирует такие события. На мой взгляд в вашем случае стоит попробывать без контроллера прерываний (1), аппаратно буфферизировать прерывания (2). Хотелось бы увидеть код обработки прерывания для работы с ОС и без неё. Тест запрещает прерывания? -

ISDN I.440

emerg_reanimator ответил emerg_reanimator тема в ISDN/G.703/E1

Спасибо! Вспомнил, что кроме ИТУ-Та есть ещё в евровпе стандарт ЕТСИ. -

ISDN I.440

emerg_reanimator опубликовал тема в ISDN/G.703/E1

Подскажите, пожалуйтса, где найти. -

Быстрй USB JTAG интерфейс

emerg_reanimator ответил Dainis тема в ARM

Выбор режима делает драйвер. Функция FT_SetBitMode () описана в документе AN2232C-02 BIT MODE FUNCTIONS FOR THE FT2232C. Я не пользуюсь этой МКС, но идея имет USB адаптер мне нравиться. Соответствующая документация есть на сайте. ft2232c.zip