justontime

Свой-

Постов

261 -

Зарегистрирован

Весь контент justontime

-

Похоже, нашел окончательную проблему - все-таки MAX был подгоревший. Заменил на другой - вообще все странности исчезли, и все заработало нормально с обеими Blaster'ами

-

Нашел, попробую...

-

Не подскажете, где это устанавливается ?

-

На всякий случай, если вдруг кто-то еще столкнется с таким... Как уже писал, в процессе отладки системы на MAX 10 с NIOS вдруг появился сбой при попытке загрузить проект NIOS - что-то с областью памяти. Начал проверять память рекомендованным выше способом с помощью memory editor и сразу же обнаружил, что при попытке загрузки в память всех единиц вылетает ошибка JTAG. При этом все нули пишутся и читаются вроде нормально. Утвердился с мыслью, что при замыкании ранее подпортил FPGA, но для очистки совести решил провести аналогичный эксперимент с похожей, но другой, платой (вроде нормально работающей). К моему удивлению, она повела себя аналогично ! А вот после замены фирменного USB Blaster II от Altera на самый обычный от Waveshare (который раз в 10 вроде дешевле) обе платы заработали нормально... Что это было, понятия не имею... P.S. А так Altera USB Blaster II вроде работает нормально, прошивку программирует без проблем...

-

Да я о таких способах и сам размышлял, но надеялся, что есть что-то более гламурное :)

-

Проверка MAX 10 на исправность

justontime опубликовал тема в Работаем с ПЛИС, области применения, выбор

Существует ли простой способ проверить MAX 10 на физическую исправность (в первую очередь, исправность блоков RAM) ? Отлаживал проект на NIOS на собственной плате, и в какой-то момент NIOS перестал грузиться - выдает ошибку верификации памяти. До этого все работало, и другой проект вроде нормально грузится, но не факт, что эти проекты используют тот самый участок памяти. Подозрение именно на физическую проблему с FPGA довольно сильное - до этого немножко :) замкнул одно питание на другое, но вроде бы сначала ничего не проявлялось, все работало... Подключение к FPGA самое обычное, через JTAG -

Только что уже сам нашел, но все равно спасибо ! Мне эти байты как раз очень нужны были :)

-

Блин, и оно при этом работает ! С ума сойти, это именно то, что мне нужно было, еще раз спасибо ! P.S. А как драйвер нафиг выбросить ? P.P.S. Ну, и если еще кто столкнется - самым простым решением убрать прерывание ADC (которое просто все подвешивало, хотя специально не разрешал) было просто отключение соответствующей линии IRQ в Platform Designer'е

-

А не поделитесь ещё и инициализацией ?

-

Спасибо !!! У меня версия 17.1 lite, там уже нормально ? И еще вопрос, если можно - судя по коду, который удалось найти в интернете, в какой-то момент названия были изменены, типа вместо MODULAR_AD1C_0_SEQUENCER_CSR_BASE стало ADC_SEQUENCER_CSR_BASE Это действительно так ?

-

Блин, вроде бы сделал, как нужно, но фигню какую-то читает неменяющуюся (при изменении напряжения на входе ADC). Никто не поделится кусочком работающего кода, инициализирующего ADC и получающего данные ? Имел ввиду - код на С под NIOS...

-

Они озверели !!! "Bank 1A, 1B, 2, and 8—you cannot use GPIO pins in these banks." если ADC в принципе включен !!! И это в корпусе E144... Вообще первоначальный восторг по поводу MAX 10 у меня начинает проходить - уже в который раз натыкаюсь на подобные засады... Да, понятно, что UG нужно читать внимательно, но... Да я параллельно уже тоже нашел (только в другом месте), и высказал свое крайнее неудовольствие... Реально у MAX 10 слишком много таких ограничений... Кстати, именно это ко мне не имеет отношения - я же использую ANAIN, а не пин из обычного банка, поэтому и не ожидал такой засады... Ладно если бы использование пина из банка отрубало этот банк, но когда сам факт включения ADC отрубает чуть ли не половину GPIOs, это уже ни в какие ворота не лезет...

-

Мне кажется, я задал достаточно определенные вопросы, а не просто попросил рассказать вообще... А ADC UG у меня и так последние пару дней любимое чтиво... Ладно, с clk я уже разобрался (все, как и предполагал), возник другой вопрос. Использую только один аналоговый вход - ANAIN, а выводы ADCx (пара из них) задействованы как обычные GPIOs. При этом в процессе генерации ADC core указал, что используется только channel 0, в sequencer указал, что slot 1, привязан к ch 0. Тем не менее, при компиляции ругается, что "Can't place multiple pins..." именно на те ADCx, которые у меня задействованы, как GPIOs. Где ему еще нужно сказать, что эти ноги нафиг для ADC не нужны ???

-

Altera ADC core

justontime опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Пытаюсь запустить ADC на MAX 10, что-то не очень (мягко говоря) получается... Для начала, кто-нибудь знает, чем отличаются clock и adc_pll_clock ? Типа по clock идет общение с внешним миром, а adc_pll_clock только для преобразования A->D ? Если так, они должны быть как-то синхронизированы и т.д. ? -

Блин, все еще продолжаю бороться... Если запустить проект на реальном железе, то все в порядке - в disassembly имеется как раз то, что нужно. Но как получить аналогичное без запуска проекта - не понимаю :(

-

Нужно запускать на реальном железе, или нужно настраивать ? Просто при попытке настроить все упирается в Target Connection - без железа не получается, а нужно, как изначально говорил, именно просто посмотреть код после компиляции без необходимости запускать...

-

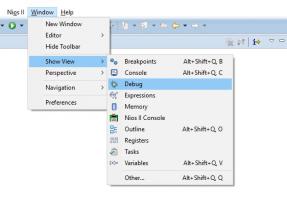

Как раз сам начал туда смотреть :) Вкладка Disassembly появилась, но пустая, и как там что-то получить, непонятно... Случайно не нужно запускать на реальном железе ? При попытке Run -> Debug выдает "Launching .elf has encountered a problem. Error with command gdb --version" Или нужно что-то еще для отладчика gdb настраивать ? P.S. Извините за глупые вопросы - только начинаю со всем этим разбираться...

-

Блин, у меня там нет Disassembly... Quartus 17.1 Если честно, я с ним вообще не знаком... Обязательно посмотрю, но сейчас даже особо и не нужен - было бы вполне достаточно нормально смотреть код...

-

Кстати, а нафига вообще нужен внутренний генератор с такими параметрами (вернее, с отсутствием таковых), какое у него может быть реальное применение ?

-

Блин, ну как же не люблю бороться не только с проектом, но еще и средой... Очевидно, я совсем тупой, но как удобно смотреть в Eclipse, какой машинный код отвечает тому или иному куску кода на C ??? Понятно, что можно посмотреть в .objdump, но там все подряд, а хотелось бы ткнуть мышкой в строку исходника, и увидеть, что получилось из этого на asm. Причем это еще хочется без необходимости запускать приложение на реальном железе (отладка не нужна, просто смотреть соответствие кода)...

-

И еще вопрос - правильно ли я понимаю, что при аппаратном сбросе NIOS все переменные в программе, написанной на C, либо инициализируются значением, указанным при декларировании (если указано), либо не определены ? Существует ли какой-то правильный способ передать данные (совсем немного, несколько байт) из состояния "до сброса" в состояние "после сброса" ?

-

Столкнулся с идентичной проблемой - вроде мелочь, но раздражает, что нельзя использовать свое имя... Неужели так и нет решения ?

-

Сразу же помогло, спасибо !

-

По непонятным для меня причинам с какого-то момента редактор в Eclipse стал ругаться на новые имена, которые появляются в ходе развития проекта. Допустим, добавляю PIO, и все ссылки на его регистры, берущиеся напрямую из system.h, вызывают ошибки редактора "Symbol xyz could not be resolved" - значок напротив строки в редакторе и сообщение в списке проблем. При этом все нормально компилируется и запускается. Обновлял и заново генерировал все, что можно - разницы никакой... Нашел у Altera следующее - https://www.altera.com/support/support-reso...ns/fb91565.html У меня версия 17.1 - неужели за это время не починили ??? И метод решения предлагают классный - просто отключить предупреждения...

-

В книге Pong Chu "Embedded SoPC design" есть подробнейший пример с NIOS II и PS/2 клавиатурой/мышью Причем книга есть как на VHDL, так и на Verilog