bratok-gl

-

Постов

44 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные bratok-gl

-

-

Ищу монтажника в москве или ближнем подмосковье для монтажа перемычек на плату.

Требется:

1.Изготовить перемычки (отрезки проводов).

2.Монтировать перемычки на плате до 12шт. Бывают и 2 перемычке и 11 перемычек, среднее где-то 6-7 на плату. Все зависит от партиии.

3.Подклеить длинные перемычки, чтобы не оторвались.

Оплата происходит за два этапа, первый за установку (изготовление, установка, приклейка) перемычек 250 рублей за одну плату.

Вторая после удачной проверки на работоспособноссть платы - 250 рублей.

Процентов 20 из плат требуют дополнительно поставить перемычки 1-2 после проверки, так не всегда могу точно можно определить дефект платы. Плата возвращаеться вам на установку перемычек и повторно проверяется на работоспособность.

В сумме за одну плату получается 500 рублей. В месяц примерно 40 плат, встреча раз в неделю для передачи и получения плат и денег ( район ВАО, СВАО).

пример короткой пермычки, длинная вдали

для контакта, вопросов и предложений пишите на [email protected] Антон

Вакансия закрыта.

-

Ищу монтажника в москве или ближнем подмосковье для монтажа перемычек на плату.

Требется:

1.Изготовить перемычки (отрезки проводов).

2.Монтировать перемычки на плате до 12шт. Бывают и 2 перемычке и 11 перемычек, среднее где-то 6-7 на плату. Все зависит от партиии.

3.Подклеить длинные перемычки, чтобы не оторвались.

Оплата происходит за два этапа, первый за установку (изготовление, установка, приклейка) перемычек 250 рублей за одну плату.

Вторая после удачной проверки на работоспособноссть платы - 250 рублей.

Процентов 20 из плат требуют дополнительно поставить перемычки 1-2 после проверки, так не всегда могу точно можно определить дефект платы. Плата возвращаеться вам на установку перемычек и повторно проверяется на работоспособность.

В сумме за одну плату получается 500 рублей. В месяц примерно 40 плат, встреча раз в неделю для передачи и получения плат и денег ( район ВАО, СВАО).

пример короткой пермычки, длинная вдали

для контакта, вопросов и предложений пишите на [email protected] Антон

-

Вместо FD_1 поставьте IFD_1. Зачем у вас там BUFG натыканы? Fanout этих цепей равен 1 - BUFG тут неуместен.

Спасибо попробую, от безысходности:))

-

Добрый день, такая проблема, подскажите...

Кристал XQR2V3000-4cg717

Имеются четыре дифференциальных входа, которые через глобальные буферы проходят на модуль управления. Не получается подключить регистры в IO блоках, хотя выходные получилось,поставив на схеме регистры перед выходами. Здесь поставил те же регистры, поставил в свойствах Pack I/O Registers/Latchers into IOBs - For Input and Output

-

Вот вы то мне и нужны!)

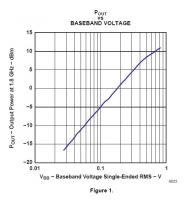

Я так понимаю для TRF3703-15 входной сигнал, от ЦАП, не должен превышать 1.5 В?

На плате ЦАП(к примеру на вашей) , выходной уровень фиксирован, либо же можно выбрать, например 3.3 В или 1.5 ?

В даташитах по сопряжению подобных микрух(QPSK модулятора и ЦАП) между ними ставить какой-то делитель на резисторах, где номиналы резисторов уж слишком точны, что бы их найти. Как вы решили эту проблему?

Ну и последний вопрос, что у вас за генератор для модулятора и для ЦАП?

Как я понял TRF370315 With 1.5-V CM at I, Q Baseband Inputs - вход I и Q с 1.5В опорой.

После ЦАП стоят фильтры убирающие периодичность, а потом дифференциальный усилитель THS4511 у которого есть вход СМ, туда и подаю 1.5 В.

А какая точноть номиналов 0.5 или 0.1%??

Опору для модулятора мне дают, а вот на ЦАП использую ГК-CPPV7-A7BR-160.0M БМГ Плюс.

А вход IQ Vbb до 1В

-

Как раз щас и буду запускать плату с TRF370315 и DAC5675A, вот и посмотрим:))) DAC уже работает а вот TRF пока нет... но греиться сильно градусов 50

-

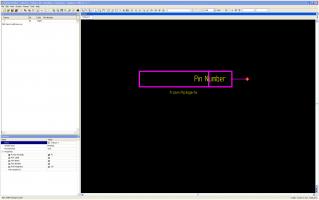

Вы задали только номер пина, RefDes тоже должен быть установлен, именно поэтому при повторном запуске у вас ничего не меняется.

Да fill, я с нетерпением ждал вашего ответа, работает, я все таки думал что-бы RefDes автоматически присваивался, а gates (pin) выбирать самому - это удобнее:)

Еще раз спасибо!

-

поставь Frozen Package=fix

Тоже самое dxd_pinfix_4.rar

Правда меняется только один раз, при упаковке, а потом не меняется, так и должно?

-

Видимо используете опцию Repackage_all.

Да, действительно, делал Repackage_all, щас делаю Repackage Unfixed Symbol, тоже самое происходит, в чем загвоздка не пойму.....

Вот видео записал ....dxd_pinfix.rar

-

-

Пробовал отдельно найти impact в версии ISE6.3 и переписать на другой комп - не запускался! есть ли отдельные программы для заливки??

а то ставить весь ISE не всегда надо

-

ВАОООООООО!!!! Вот это да! Спасибо большое все заработало! Я не и не думал что проблема выходит за рамки программы Mentor, наверно скрипт писали под их винду:) Получается что у кого работает не русифицированный Windows XP. Вот только интересно как я сам должен был до этого дойти, в каких документах это написано:)

Еще раз, спасибо, кстати у нас лицензия на ментор куплена на несколько компов (НИИТП), только я всеравно на пиратской пока, так как сеть по предприятию плоховата и сервера под это дело еще не поставили, а зависеть от другого компа не прикольно.

-

Fill, извените еще раз, так я и не нашел где установить точку в качестве разделителя...

Создал проект в нем под 300 компонентов из них 197 конденсаторов, ПЛИС XQR2V3000-4CG717V через IO designer, два DAC5675 всякой обвязки, и перечень пришлось щас делать по компонентам как REFDES легли:)

-

Все сделал, ошибка регистрации исчезла, но проблема так и осталась с LOAD

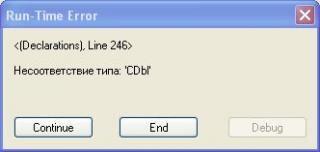

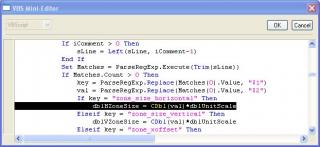

dblHZoneSize = CDbl(val)*dblUnitScale за что отвечает эта строчка в скрипте assignrefdes.efm?

-

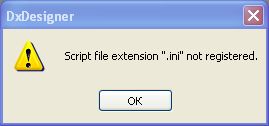

добавил во все WDIR так стал выдавать "Script file extension .ini not registred", потом ок и запускаетьcя DxD

в FlexLM scripts.ini :

[ViewDraw]

Script#0=C:\FLEXlm\scripts.ini

C:\MentorEE20076\2007.6EE\SDD_HOME\standart\ scripts.ini:

[LibraryStudio]Script#0=$SDD_HOME/$SDD_DX/samples/lstudio/scripting/verification_menu.vbs[ViewDraw][HDLPCBDesigner]

Script#0=verilog_preview.vbs

Script#1=hdlpcbmenus.vbs

Script#2=decal.vbs

Script#3=CopyCircuit.vbs

В первом само прописываеться если в DxD установить скрипт Setitngs-Run on startup-scripts

Как только убираю в C:\FLEXlm\scripts.ini строку то ошибка пропадает

-

- переписал файлы assignrefdes.efm, CopyCircuit.vbs, RefdesSettings.efm в C:\MentorEE20076\2007.6EE\SDD_HOME\standard

- добавил в файле C:\MentorEE20076\2007.6EE\SDD_HOME\standard\scripts.ini

[LibraryStudio]Script#0=$SDD_HOME/$SDD_DX/samples/lstudio/scripting/verification_menu.vbs[ViewDraw][HDLPCBDesigner]

Script#0=verilog_preview.vbs

Script#1=hdlpcbmenus.vbs

Script#2=decal.vbs

Script#3=CopyCircuit.vbs

- запускаю DXD, открываю страницу, edit->assign Refdes, ставлю натсройки как выше, при попытке LOAD выскакивает ошибка <(Declarations), Line 246> несоответствие типа CDbl , что я не так делаю? подскажите..

-

В процессе отладки - пользоваться JTAG-ом FPGA, грузить проект из САПР и только итоговый прошить в ПЗУ (увы - она однократная).

Или найти что-то подходящее перепрограммируемое, по крайней мере для макетного образца, а потом заменить.

По другому не знаю.

Все понял, спасибо, в чип-дипе нашел программатор ELNEC BEEPROG+ USB-LPT 37500.00 руб. правда к нему нужен адаптер

http://www.chip-dip.ru/product0/9000035152.aspx - программатор

-

Получаеться, сначало надо запрограммировать ПЛИС через кабель, отладить проект и только потом прошить ПЗУ и запоять на плату:)) ТАк получается?

-

Жил не тужил, и тут.. Разрабатываю плату где стоит XQR2V3000-4CG717V радиационностойкий, выбираю к нему ПЗУ XQR17V16, при разраработке схемы удивляюсь что ПЗУ One-time programmable (однократно программируемая), это меня озадачило так как всегда программировал FLASH память для vittex-e, немного Altera, с помощью всевозможных байтбластеров, но тут как быть?? Чем и как программировать данный девайс??

Походу должен быть программатор...но как подсоединять нет ни TDO TDI TSK...

ПЗУ http://www.xilinx.com/support/documentatio...heets/ds126.pdf

ПЛИС http://www.xilinx.com/support/documentatio...heets/ds124.pdf

Поскажите что читать?

-

Перепробовал версии MS SE 5.8f, 6.0a,6.0, 6.2f,6.2a, 6.3.

6.3 вообще не запускается

6.2f запускается но вылетает с кодом ошибки "211" при выполнении команды vsim, хотя

этот проект великолепно симулится под Modelsim X.X + WinXPSP2.

Может ModelSim пока не знает про Vista?

Такая же ошибка - "211", моделсим 6.2b и 6.2f, вот мучился, только щас залез и посмотрел что не поддерживается vist-ой http://www.model.com/support/platform.asp

Жаль переходить на XP, только привык:)

-

Подскажите пожалуйста, с LVDS первый раз сталкиваюсь. Подвожу к кристалу xcv600e-hq240 LVDS сигнал с приемника (LVPECL -->LVDS sn65lvds101 ) (pin 160 & 159) положительный и отрицательный, ставлю 100 Ом близко к ножкам ПЛИСа. В проекте есть модули написаные на VHDL и собраные в общую схему в ISE редакторе, там есть сигнал INF который надо получить из LVDS. Какой элемент мне поставить в схеме (буфер LVDS?) и как его потом прописать в *.ucf. Вроде просто, но немогу сообразить. И как по поводу того что растояние между ножками LVDS положительного и отрицательного всего 0.65 мм (соседние пины)??

-

-

Все!!! Наконец-то нашел причину, просто у меня блок памяти подключался к другому, в котором один разряд данных не использовался. Так вот из-за этого и была ошибка, как только не нужный разряд вывел на улицу(пин), все отлично.

Теперь буду ждать , когда запрограммирую, очень интересно, как будет работать память???? это мой первый проект с памятью:)))

-

Забил я с этим Coregen'ом и решил написать кодом, по подсказкам пользователей посмотрел в Constraints Guide и вот что написал:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity rominfr is

port ( CLK : in std_logic;

addr : in std_logic_vector(10 downto 0);

data : out std_logic_vector(15 downto 0)

);

end rominfr;

architecture syn of rominfr is

type rom_type is array ( 0 to 2047) of std_logic_vector (15 downto 0);

constant ROM : rom_type :=

(

"0000000000000000",

"0000000000000000",

.

..

..

"0111011100101001",

"1001001000001001",

"1010101011101001",

"1111111110001001",

"0000000000001001"

);

begin

process (clk)

begin

if (CLK'event and CLK='1') then

data <= ROM(conv_integer(addr));

end if;

end process;

end syn;

Потом вставил этот модуль в схему свою, и вроде память подключилась и моделируется.

Но трасировщик не подключил один вывод блока памяти.

Running DRC.

WARNING:DesignRules:332 - Blockcheck: Dangling BLKRAM output. Pin DOA0 of comp XLXI_781_Mrom__n00011_inst_ramb_2 is not connected.

DRC detected 0 errors and 1 warnings.

Такой вопрос: почему?????

Где можно изготовить модули LTCC?

в RF & Microwave Design

Опубликовано · Пожаловаться

В АО НИИ ТП изготавливают, декабристов 51 г.Москва