-

Постов

104 -

Зарегистрирован

-

Посещение

Весь контент honeycomb0

-

Переходные отверстия под QFN корпусом

honeycomb0 опубликовал тема в Работаем с трассировкой

Пытаюсь развести плату с MSP430F5528IRGC (в QFN корпусе). Плата очень ограниченна в размерах, из-за чего очень сложно "fan out" все нужные дорожки. Можно ли раположить переходные отверстия под QFN корпусом как указано на картинках? Какие могут быть ждать неприятности? Спрашиваю, т.к. в референс дизайне от TI все дорожки выведены наружу, но они и не были ограничены по площади. Спасибо -

Радиосвязь.

honeycomb0 ответил raslmc тема в Форумы по интерфейсам

Вам надо знать: выходной импеданс передатчика, входной импеданс приемника, волновое сопротивление кабеля, диапазон мощности передатчика и предельный уровень входного сигнала приемника. Если выходной импеданс передатчика равен входному импедансу приемника (они равны Z0), то можно соеденять напрямую кабелем с волновым сопротивлением равным Z0 при условии, что мощность передатчика не превысит максимальную допустимую мощность приемника на входе. Последнее условие можно удовлетворить поставив аттенюатор с необходимым коэф. ослабления на вход приемника. Если импедансы не равны, то их нужно согласовывать. -

Всем спасибо за ответы - ткнули в правильную сторону. В итоге остановился на ADS1174 - идеально подходящий под мои нужды АЦП. :)

-

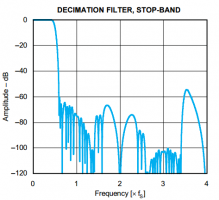

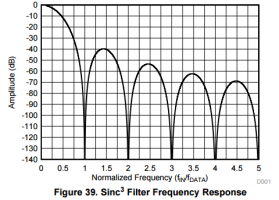

Спасибо за оперативный ответ! Единственной проблемой является АЧХ сглаживающего фильтра. Я прикрепил для сравнения АЧХ PCM1870 и ADS131A02. Естественно, PCM1870 целевой задачей являются аудио приложения, и оттого там фильтруют намного агрессивнее. Если бы не АЧХ, то ADS131A02 был бы идеальным АЦП для моей задачи. Прошу прощения что не уточнил сразу это требование. Если быть точным, то мне необходимо оцифровать 0-10кГц синал, при этом подавить сигналы на 40кГц и выше на как минимум 40дБ. Аудио АЦП с этим справляются на ура, однако все их интерфейсы для передачи данных - I2S (что логично для аудио).

-

Есть ли такой АЦП в природе?

honeycomb0 опубликовал тема в Цифровые схемы, высокоскоростные ЦС

По сути мне нужен АЦП PCM1870a, но который слал бы данные по SPI. Надо качественно дискретизировать две полосы в 10кГц, желательно чтобы фильтр сглаживания был уже встроен в АЦП (как в стандартных аудио АЦП, в которых сигнал круто "оверсамплится"). Все АЦП которые находятся имеют стандартные I2S интерфейсы для передачи данных. К сожалению из-за определенных ограничений в системе, этого интрефейса у меня нет - есть только SPI :crying: -

Вот спектр комплексного сигнала (описанного выше) в Матлабе. Никаких аллиасов на 30 и 40кГц не видно... Кстати, частота реконструкционного фильтра векторного генератора 10МГц.

-

Здравствуйте. Попробую описать свою проблему, над которой бьюсь неделю... Уверен, что решение лежит где-то на повернхости, и просто из-за моей нехватки опыта или фундаментального понимания процесса, оно (решение), продолжает ускользать. Надеюсь на помощь "зала" :) Итак, я пытаюсь сгенерировать комплесный сигнал (назовем его S1), который состоит из: - Синусойда с частотой f1 (пусть будет 30Гц) - "Под-несущая" с частотой f2 (пусть будет 10кГц), которая частотно модулированна (FM) частотой f1 (но с разнецой в фазе, psi). Для пущей сложности, амплитуда "под-несущей" f2 (10кГц), промодулированная АМ, частотой f3 (пусть будет 60Гц). И, наконец, боковые полосы частот FM "под-несущей" f2, поочередно подавляются с частотой f4 (пусть будет 1170Гц - четное f1). (Описанный выше сигнал, S1, будет амплитудно модулировать несущую в полосе УКВ, но это не важно в рамках данной задачи, все что я пытаюсь сделать - это сгенерировать сигнал S1 при помощи векторного генератора сигналов.) Есть люди, которые уже решали конкретно эту задачу, и подробно (но не без опечаток) описали ее решение в патенте. Сюда приведу только конечные уравнения, которыми этот комплексный сигнал S1, был описан в патенте: I(S1) = (1 + Mv*cos(2*pi*f1)) * cos(psi) + (1 + Mv*cos(2*pi*f1)) * Mr*sin(2*pi*f2 - Mc*sin(2*pi*f3)) Q(S1) = (1 + Mv*cos(2*pi*f1)) * sin(psi) + (1 + Mv*cos(2*pi*f1)) * Mr*cos(2*pi*f2 - Mc*sin(2*pi*f3)) * sign(cos(f4)) Где Mv, Mr и Mc - индексы модуляции. Проблема вот в чем. Измеряю выход векторного генератора, и вижу следующий спектр (центральная частота - это упомянутая RF нусещая, диапозон частот - 100кГц). Частота под-несущей - 10кГц (и ее видно на одно деление от центра). Но откуда взялся этот "аллиасинг", что на 30 и 40кГц от центра? Первое что приходит на ум - это что-то с ФНЧ на выходе векторного генератора... Но! Если я перестану "поочередно подавлять" боковые полосы поднесущей т.е. S1 примет вид: S1 = 1 + Mv*cos(2*pi*f1) + Mr*cos(2*pi*f2 - Mc*sin(2*pi*f1)) * (1 + Md*cos(2*pi*f3)) ... то весь этот "антиаллиасинг" изчезает. Частота дискретизации 4 * f2, т.е. оверсамплинг самой большой частоты S1 (10кГц) в 4 раза. Что это может быть? Правильны ли уравнения? P.s. дописал и понял, насколько непросто кому-нибудь слету все это переварить...

-

Каюсь. Я про выше 115200 uart и не подозревал... :(

-

Все верно, блоками длиной в 12к и небольшими передышками между ними (в идеале эта передышка была бы в районе сотен мс). Просто если использовать UART для записи в память, эта передышка будет уж очень огромна... Если получится, обязательно поделюсь. А с какими проблемами вы столкнулись?

-

Ну, требования ведь не изменились. Комп читает длинный файл построчно, файл содержит массив сигналов. В любом случае связь с компом необходима, для генерации самого массива и его записи в память/FIFO. Спасибо всем за интересные варианты.

-

Спасибо, заинтриговали:) да, сигналы заранее подготовленны... А зачем два, простите за вопрос? в quad быстрее передача? (Полез параллельно гуглить)

-

Бюджетный вариант: ПЛИС с 12КБ памяти, вместо UART'а контроллер с USB2.0.

-

Спасибо, буду иметь в виду. По поводу передачи 12КБ в память, это пока самый реализуемый вариант, я согласен. Единственная проблема - будет ощутимая задержка между сигналами (сигнал в данном случае - это последовательность из 12000 бит на каждом из 8ми каналов). Т.е. У меня сигнал длиной в 120мкс (10нс на каждый бит), поэтому перезаписывая неспеша по UART'у после каждого 120мкс сигнала очень мучительно... В идеале, ПК читает длинный файл и пихает в FIFO, котороый и тайминги соблюдает и не дает ПК переполнить буфер. Ну тут, действительно, задача на USB3 с небольшим ПЛИС от Lattice вырисовывается...

-

Спасибо _pv за наводку! Не знал про FT600Q, в мою задачу вписывается идеально.

-

Все так, только у меня же 8 параллельных каналов (8 ножек). И каждый канал непрерывно должен "выпалить" 12000 бит.

-

Всем спасибо за ответы! да, на самом деле я что-то не подумал написал про USB... Попробую реализовать на ПЛИС. Минимальная длина сигнала, который надо непрерывно генерировать имеет 12000 бит, а значит надо будет организовать 12 килобайт памяти.

-

Как проще сделать детерминированный бит-банг?

honeycomb0 опубликовал тема в В помощь начинающему

Здравствуйте! Посоветуйте, как было бы проще собрать устройство, которое на входе получает байт, а на выходе ставит 8 ножек согласно битам из принятого байта (в просто-народе "бит-бангинг"). Главное требование, оно же и ограничение - выход должен строго работать на частоте 100МГц. Может есть какие-то готовые решения (что-то вроде дешевого анализатора спектра, только наоборот)? Каким я вижу одно из возможных решений: взять кортекс М4 с USB2.0, и настроить DMA для USB и GPIO. Хост (на ПК) будет построчно читать из файла байты, и слать их по USB на МК. Единственное, в чем я вижу сложность, это как мне строго задать частоту всего пайплайна, чтобы на выходе ножка порта дергалась каждые 10нс? Насколько такое решение вообще реализуемо? (Простите, за возможно делитанский вопрос.) -

ФАПЧ на целочисленной арифметике

honeycomb0 ответил honeycomb0 тема в Алгоритмы ЦОС (DSP)

Спасибо за наводки, буду смотреть-разбираться... -

ФАПЧ на целочисленной арифметике

honeycomb0 ответил honeycomb0 тема в Алгоритмы ЦОС (DSP)

Насчет подбора, я полностью соглашусь. Однако я должен признать свою полную несостоятельность на этом поприще. Я перерыл много материала по теме, везде подробно описано как устроена ФАПЧ, приведена передаточная хар-ка петли, выведены основные параметры (резонансная частота петли, коэффициенты фазового детектора, коэффициент ГНУ, демпинг фактор и др.), мне даже стали понятны критерии стабильности всей ФАПЧ - однако как расчитать коэффициенты я так и не понял. Они все связаны между собой, и никак не получается систематизировать их отношения и рассматривать как отдельно взятую еденицу. Я ищу этот рецепт, но пока результат никакой, рецепта найти не удалось. Повсеместно гоняю ФАПЧ в симуляторе, однако уже становится понятным что результат этой затеи плачевен... -

ФАПЧ на целочисленной арифметике

honeycomb0 ответил honeycomb0 тема в Алгоритмы ЦОС (DSP)

В курсе, но вот незадача: ki = 5.9164e-009, kp = 1.5384e-005. -

ФАПЧ на целочисленной арифметике

honeycomb0 опубликовал тема в Алгоритмы ЦОС (DSP)

С горем пополам удалось реализовать модель ФАПЧ (кстати прекрасно описанной на dsplib.ru) для простой, как мне казалось задачи - просто "схватиться" за фазу входной медленой (30Гц) синусойды и сихронизировать с ней NCO на той же частоте (другими словами просто "скопировать сигнал"). Удачно подобрал коэффициенты для моей задачи, получившийся ФАПЧ устраивает всем, кроме одного - модель используют double тип данных, а моя конечная цель - реализовать ФАПЧ на полностью целочисленной арифметике. На данный момент, все мои попытки конвертировать получившиюся модель на integer математику, как и ожидалось, неудачны. Проблема в том, что коэффициенты петлевого фильтра нещадно малы - я отчаяно пытаюсь их маштабировать, но на выходе ФАПЧ выходит каша... Хотел узнать, ведь наверняка кто-то сталкивался с подобной проблемой, может подтолкнете меня в нужное направление? Ведь каким-то образом данная задача реализовывалась на ПЛИС? Спасибо -

Помогите разобраться с Process Gain

honeycomb0 опубликовал тема в Алгоритмы ЦОС (DSP)

Заранее прошу прощения за англ. терминологию - я нигде не встречал русского аналога термину Process Gain, однако он прямо пестрит в англоязычной литературе. Обычно, понятие Process Gain можно встретить в конексте ПФ, и определяется следующим образом: В более общей форме, Process Gain представляется как 10*log10( Fs/(2*BW) ), где Fs - частота дискретизации, а BW - полоса. В случае ПФ, рабочая полоса равна Fs/M - и с Process Gain вопросов не возникает. А вот если у меня простой тракт ЦОС состоящий из КИХ/БИХ фильтров, и никакого ПФ, правильно ли я понимаю что для оценки Process Gain моей ЦОС, полоса будет равной пропускной полосе всей системы (т.е. -3дБ полоса результирующей АЧХ всей цепочки из цифровых фильтров в тракте ЦОС)? И таким образом я могу грубо прикинуть SNR моей ЦОС как: -

Спасибо, обязательно гляну!

-

Спасибо за ответ!

-

Как оценить "чистоту" спектра реализованного DDS?

honeycomb0 опубликовал тема в Алгоритмы ЦОС (DSP)

Реализован простенький DDS для квадратурного смесителя. Имеется его реализация в С++ (изначально была написана симуляция всего DSP в софте), а так же и последующая его описание на VHDL. Очень интересно удостоверится в "чистоте" его спектра. На ум приходит вот что: Берем реализацию С++, берем данные на его выходе и прогоняем их через ДПФ в Матлабе, применяя наиболее подходящее для этого окно. Вопрос - насколько наивен данный метод для анализа спектра реализованного DDS? :rolleyes: Какое окно посоветуете применять для данной задачи?