Zol'berg

Участник-

Постов

17 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Zol'berg

-

Звание

Участник

Посетители профиля

-

No source available for ""

Zol'berg ответил Zol'berg тема в ARM, 32bit

"Интересно, что вы будете делать, когда решение из гугля будет для ситуаций с похожими симптомами, но другими причинами?" Как и раньше, буду биться головой о стену т.к. не знаю даже где искать :( , ибо раньше уже встречался с такой проблемой, после бессонных ночей так и не понял откуда взялась и куда делась! -

No source available for ""

Zol'berg опубликовал тема в ARM, 32bit

Всем привет, ладил я тут как то код на F4 Discovery, и ниче, нормально, решил попробовать в реальном устройстве, в котором стоит STM32F405RG, раньше ладилось, а теперь при запуске отладки пишет 'No source available for "" ' и предлагает глянуть в дисассемблер, в CooCox в конфигурации во вкладке Device выбираю нужную микруху, все равно ничего, как то была такая фигня, когда в имени исходника были русские буквы, а сейчас?? О, в Гюгле нашел, BOOT0 висел в воздухе, хотелось бы все же знать что значит этот меседж)) Гюгел - сила :yeah: -

float32 в параллельный порт

Zol'berg ответил Zol'berg тема в ARM, 32bit

Всем спасибо, заработало! :cheers: -

float32 в параллельный порт

Zol'berg опубликовал тема в ARM, 32bit

Всем привет, имеется программка, имеющая результатом своих вычислений массив float32_t, на базе stm32f4, и все хорошо, но вот проблемка, теперь необходимо вывести это все параллельно через порт (16 битный), сперва старшие 2 байта, а после младшие 2 байта, как это сделать на С без преобразования float в int не догоню, операции сдвига для float не катят!! Спасибо)) -

Исключения или нет STM32F4?

Zol'berg ответил Zol'berg тема в ARM, 32bit

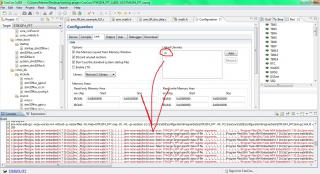

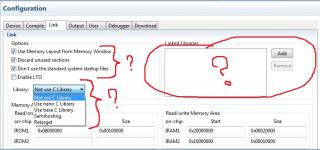

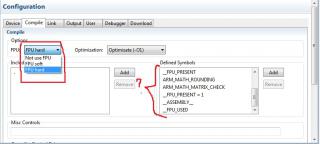

Походу дело было в этом, кажись теперь не вылетаю)), тогда не понятно что за опция в "FPU hard": Tеперь другая проблема, компилятор не знает: "undefined reference to `sqrtf'", но по ходу моя вина, как то по дурости очистил все Linked Libraries, и теперь не знаю что туда грузить! Что значат вот тее опции?? А вот подгрузил libm.a из "C:\Program Files\GNU Tools ARM Embedded\4.7 2013q1\arm-none-eabi\lib\thumb", результат попытки компиляции внизу скрина. Кстати файлов "libm.a" там целая куча в разных папках, какой именно необходимо грузить? Действительно не пашет :crying: -

Исключения или нет STM32F4?

Zol'berg ответил Zol'berg тема в ARM, 32bit

Определил функцию: static void HardFault_Handler(void) { /* Go into an infinite loop. */ while (1) { } } Все равно попадаю в Default_Handler, сейчас гляну регистр.. Чет я вообще не пойму, как посмотреть этот самый ICSR?? -

Исключения или нет STM32F4?

Zol'berg ответил Zol'berg тема в ARM, 32bit

Вижу структуры для сохранения состояний регистров, как этим воспользоваться никак не пойму, что такое ""codebox" перед "code"" вообще не знаю, что это?? Листинг/сухой код это конечно хорошо... -

Исключения или нет STM32F4?

Zol'berg ответил Zol'berg тема в ARM, 32bit

СПС :rolleyes: А где этот самый регистр, ICTR (NVIC) вижу, ICSR не вижу!? И к слову никаких инициализаций прерываний не делал! -

Исключения или нет STM32F4?

Zol'berg опубликовал тема в ARM, 32bit

Всем привет, занимаюсь освоением FFT на STM32F4 в CooCox, кое как собрал проект из "CMSIS STM32F4 DSP and standard peripherals library" , вроде компилятор не ругается, но вот беда, при вызове функции "arm_radix4_butterfly_f32" в файле "arm_cfft_radix4_f32.c", а если её закомментить , то в другой ф-ии влетаю в, если я правильно понял "системное исключение" и зависаю в цикле: static void Default_Handler(void) { /* Go into an infinite loop. */ while (1) { } } В файле startup_stm32f4xx.c. Где или в каком регистре отображается причина происходящего,"статус ядра", может в "xpsr"? Как насчет регистров группы DBG (отладчика)? Значения передаваемые в Ф-ию проверял, кажись норм! :crying: Что делать?? startup_stm32f4xx.c: /*----------Stack Configuration-----------------------------------------------*/ #define STACK_SIZE 0x00000200 /*!< Stack size (in Words) */ __attribute__ ((section(".co_stack"))) unsigned long pulStack[sTACK_SIZE]; /*----------Macro definition--------------------------------------------------*/ #define WEAK __attribute__ ((weak)) /*----------Declaration of the default fault handlers-------------------------*/ /* System exception vector handler */ void WEAK Reset_Handler(void); void WEAK NMI_Handler(void); void WEAK HardFault_Handler(void); void WEAK MemManage_Handler(void); void WEAK BusFault_Handler(void); void WEAK UsageFault_Handler(void); void WEAK SVC_Handler(void); void WEAK DebugMon_Handler(void); void WEAK PendSV_Handler(void); void WEAK SysTick_Handler(void); void WEAK WWDG_IRQHandler(void); void WEAK PVD_IRQHandler(void); void WEAK TAMP_STAMP_IRQHandler(void); void WEAK RTC_WKUP_IRQHandler(void); void WEAK FLASH_IRQHandler(void); void WEAK RCC_IRQHandler(void); void WEAK EXTI0_IRQHandler(void); void WEAK EXTI1_IRQHandler(void); void WEAK EXTI2_IRQHandler(void); void WEAK EXTI3_IRQHandler(void); void WEAK EXTI4_IRQHandler(void); void WEAK DMA1_Stream0_IRQHandler(void); void WEAK DMA1_Stream1_IRQHandler(void); void WEAK DMA1_Stream2_IRQHandler(void); void WEAK DMA1_Stream3_IRQHandler(void); void WEAK DMA1_Stream4_IRQHandler(void); void WEAK DMA1_Stream5_IRQHandler(void); void WEAK DMA1_Stream6_IRQHandler(void); void WEAK ADC_IRQHandler(void); void WEAK CAN1_TX_IRQHandler(void); void WEAK CAN1_RX0_IRQHandler(void); void WEAK CAN1_RX1_IRQHandler(void); void WEAK CAN1_SCE_IRQHandler(void); void WEAK EXTI9_5_IRQHandler(void); void WEAK TIM1_BRK_TIM9_IRQHandler(void); void WEAK TIM1_UP_TIM10_IRQHandler(void); void WEAK TIM1_TRG_COM_TIM11_IRQHandler(void); void WEAK TIM1_CC_IRQHandler(void); void WEAK TIM2_IRQHandler(void); void WEAK TIM3_IRQHandler(void); void WEAK TIM4_IRQHandler(void); void WEAK I2C1_EV_IRQHandler(void); void WEAK I2C1_ER_IRQHandler(void); void WEAK I2C2_EV_IRQHandler(void); void WEAK I2C2_ER_IRQHandler(void); void WEAK SPI1_IRQHandler(void); void WEAK SPI2_IRQHandler(void); void WEAK USART1_IRQHandler(void); void WEAK USART2_IRQHandler(void); void WEAK USART3_IRQHandler(void); void WEAK EXTI15_10_IRQHandler(void); void WEAK RTC_Alarm_IRQHandler(void); void WEAK OTG_FS_WKUP_IRQHandler(void); void WEAK TIM8_BRK_TIM12_IRQHandler(void); void WEAK TIM8_UP_TIM13_IRQHandler(void); void WEAK TIM8_TRG_COM_TIM14_IRQHandler(void); void WEAK TIM8_CC_IRQHandler(void); void WEAK DMA1_Stream7_IRQHandler(void); void WEAK FSMC_IRQHandler(void); void WEAK SDIO_IRQHandler(void); void WEAK TIM5_IRQHandler(void); void WEAK SPI3_IRQHandler(void); void WEAK UART4_IRQHandler(void); void WEAK UART5_IRQHandler(void); void WEAK TIM6_DAC_IRQHandler(void); void WEAK TIM7_IRQHandler(void); void WEAK DMA2_Stream0_IRQHandler(void); void WEAK DMA2_Stream1_IRQHandler(void); void WEAK DMA2_Stream2_IRQHandler(void); void WEAK DMA2_Stream3_IRQHandler(void); void WEAK DMA2_Stream4_IRQHandler(void); void WEAK ETH_IRQHandler(void); void WEAK ETH_WKUP_IRQHandler(void); void WEAK CAN2_TX_IRQHandler(void); void WEAK CAN2_RX0_IRQHandler(void); void WEAK CAN2_RX1_IRQHandler(void); void WEAK CAN2_SCE_IRQHandler(void); void WEAK OTG_FS_IRQHandler(void); void WEAK DMA2_Stream5_IRQHandler(void); void WEAK DMA2_Stream6_IRQHandler(void); void WEAK DMA2_Stream7_IRQHandler(void); void WEAK USART6_IRQHandler(void); void WEAK I2C3_EV_IRQHandler(void); void WEAK I2C3_ER_IRQHandler(void); void WEAK OTG_HS_EP1_OUT_IRQHandler(void); void WEAK OTG_HS_EP1_IN_IRQHandler(void); void WEAK OTG_HS_WKUP_IRQHandler(void); void WEAK OTG_HS_IRQHandler(void); void WEAK DCMI_IRQHandler(void); void WEAK CRYP_IRQHandler(void); void WEAK HASH_RNG_IRQHandler(void); void WEAK FPU_IRQHandler(void); /*----------Symbols defined in linker script----------------------------------*/ extern unsigned long _sidata; /*!< Start address for the initialization values of the .data section. */ extern unsigned long _sdata; /*!< Start address for the .data section */ extern unsigned long _edata; /*!< End address for the .data section */ extern unsigned long _sbss; /*!< Start address for the .bss section */ extern unsigned long _ebss; /*!< End address for the .bss section */ extern void _eram; /*!< End address for ram */ /*----------Function prototypes-----------------------------------------------*/ extern int main(void); /*!< The entry point for the application. */ //extern void SystemInit(void); /*!< Setup the microcontroller system(CMSIS) */ void Default_Reset_Handler(void); /*!< Default reset handler */ static void Default_Handler(void); /*!< Default exception handler */ /** *@brief The minimal vector table for a Cortex M3. Note that the proper constructs * must be placed on this to ensure that it ends up at physical address * 0x00000000. */ __attribute__ ((section(".isr_vector"))) void (* const g_pfnVectors[])(void) = { /*----------Core Exceptions------------------------------------------------ */ (void *)&pulStack[sTACK_SIZE-1], /*!< The initial stack pointer */ Reset_Handler, /*!< Reset Handler */ NMI_Handler, /*!< NMI Handler */ HardFault_Handler, /*!< Hard Fault Handler */ MemManage_Handler, /*!< MPU Fault Handler */ BusFault_Handler, /*!< Bus Fault Handler */ UsageFault_Handler, /*!< Usage Fault Handler */ 0,0,0,0, /*!< Reserved */ SVC_Handler, /*!< SVCall Handler */ DebugMon_Handler, /*!< Debug Monitor Handler */ 0, /*!< Reserved */ PendSV_Handler, /*!< PendSV Handler */ SysTick_Handler, /*!< SysTick Handler */ /*----------External Exceptions---------------------------------------------*/ WWDG_IRQHandler, /*!< 0: Window WatchDog */ PVD_IRQHandler, /*!< 1: PVD through EXTI Line detection */ TAMP_STAMP_IRQHandler, /*!< 2: Tamper and TimeStamps through the EXTI line*/ RTC_WKUP_IRQHandler, /*!< 3: RTC Wakeup through the EXTI line */ FLASH_IRQHandler, /*!< 4: FLASH */ RCC_IRQHandler , /*!< 5: RCC */ EXTI0_IRQHandler, /*!< 6: EXTI Line0 */ EXTI1_IRQHandler, /*!< 7: EXTI Line1 */ EXTI2_IRQHandler, /*!< 8: EXTI Line2 */ EXTI3_IRQHandler, /*!< 9: EXTI Line3 */ EXTI4_IRQHandler, /*!< 10: EXTI Line4 */ DMA1_Stream0_IRQHandler, /*!< 11: DMA1 Stream 0 */ DMA1_Stream1_IRQHandler, /*!< 12: DMA1 Stream 1 */ DMA1_Stream2_IRQHandler, /*!< 13: DMA1 Stream 2 */ DMA1_Stream3_IRQHandler, /*!< 14: DMA1 Stream 3 */ DMA1_Stream4_IRQHandler, /*!< 15: DMA1 Stream 4 */ DMA1_Stream5_IRQHandler, /*!< 16: DMA1 Stream 5 */ DMA1_Stream6_IRQHandler, /*!< 17: DMA1 Stream 6 */ ADC_IRQHandler, /*!< 18: ADC1, ADC2 and ADC3s */ CAN1_TX_IRQHandler, /*!< 19: CAN1 TX */ CAN1_RX0_IRQHandler, /*!< 20: CAN1 RX0 */ CAN1_RX1_IRQHandler, /*!< 21: CAN1 RX1 */ CAN1_SCE_IRQHandler, /*!< 22: CAN1 SCE */ EXTI9_5_IRQHandler, /*!< 23: External Line[9:5]s */ TIM1_BRK_TIM9_IRQHandler, /*!< 24: TIM1 Break and TIM9 */ TIM1_UP_TIM10_IRQHandler, /*!< 25: TIM1 Update and TIM10 */ TIM1_TRG_COM_TIM11_IRQHandler,/*!< 26: TIM1 Trigger and Commutation and TIM11*/ TIM1_CC_IRQHandler, /*!< 27: TIM1 Capture Compare */ TIM2_IRQHandler, /*!< 28: TIM2 */ TIM3_IRQHandler, /*!< 29: TIM3 */ TIM4_IRQHandler, /*!< 30: TIM4 */ I2C1_EV_IRQHandler, /*!< 31: I2C1 Event */ I2C1_ER_IRQHandler, /*!< 32: I2C1 Error */ I2C2_EV_IRQHandler, /*!< 33: I2C2 Event */ I2C2_ER_IRQHandler, /*!< 34: I2C2 Error */ SPI1_IRQHandler, /*!< 35: SPI1 */ SPI2_IRQHandler, /*!< 36: SPI2 */ USART1_IRQHandler, /*!< 37: USART1 */ USART2_IRQHandler, /*!< 38: USART2 */ USART3_IRQHandler, /*!< 39: USART3 */ EXTI15_10_IRQHandler, /*!< 40: External Line[15:10]s */ RTC_Alarm_IRQHandler, /*!< 41: RTC Alarm (A and B) through EXTI Line */ OTG_FS_WKUP_IRQHandler, /*!< 42: USB OTG FS Wakeup through EXTI line */ TIM8_BRK_TIM12_IRQHandler, /*!< 43: TIM8 Break and TIM12 */ TIM8_UP_TIM13_IRQHandler, /*!< 44: TIM8 Update and TIM13 */ TIM8_TRG_COM_TIM14_IRQHandler,/*!< 45:TIM8 Trigger and Commutation and TIM14*/ TIM8_CC_IRQHandler, /*!< 46: TIM8 Capture Compare */ DMA1_Stream7_IRQHandler, /*!< 47: DMA1 Stream7 */ FSMC_IRQHandler, /*!< 48: FSMC */ SDIO_IRQHandler, /*!< 49: SDIO */ TIM5_IRQHandler, /*!< 50: TIM5 */ SPI3_IRQHandler, /*!< 51: SPI3 */ UART4_IRQHandler, /*!< 52: UART4 */ UART5_IRQHandler, /*!< 53: UART5 */ TIM6_DAC_IRQHandler, /*!< 54: TIM6 and DAC1&2 underrun errors */ TIM7_IRQHandler, /*!< 55: TIM7 */ DMA2_Stream0_IRQHandler, /*!< 56: DMA2 Stream 0 */ DMA2_Stream1_IRQHandler, /*!< 57: DMA2 Stream 1 */ DMA2_Stream2_IRQHandler, /*!< 58: DMA2 Stream 2 */ DMA2_Stream3_IRQHandler, /*!< 59: DMA2 Stream 3 */ DMA2_Stream4_IRQHandler, /*!< 60: DMA2 Stream 4 */ ETH_IRQHandler, /*!< 61: Ethernet */ ETH_WKUP_IRQHandler, /*!< 62: Ethernet Wakeup through EXTI line */ CAN2_TX_IRQHandler, /*!< 63: CAN2 TX */ CAN2_RX0_IRQHandler, /*!< 64: CAN2 RX0 */ CAN2_RX1_IRQHandler, /*!< 65: CAN2 RX1 */ CAN2_SCE_IRQHandler, /*!< 66: CAN2 SCE */ OTG_FS_IRQHandler, /*!< 67: USB OTG FS */ DMA2_Stream5_IRQHandler, /*!< 68: DMA2 Stream 5 */ DMA2_Stream6_IRQHandler, /*!< 69: DMA2 Stream 6 */ DMA2_Stream7_IRQHandler, /*!< 70: DMA2 Stream 7 */ USART6_IRQHandler, /*!< 71: USART6 */ I2C3_EV_IRQHandler, /*!< 72: I2C3 event */ I2C3_ER_IRQHandler, /*!< 73: I2C3 error */ OTG_HS_EP1_OUT_IRQHandler, /*!< 74: USB OTG HS End Point 1 Out */ OTG_HS_EP1_IN_IRQHandler, /*!< 75: USB OTG HS End Point 1 In */ OTG_HS_WKUP_IRQHandler, /*!< 76: USB OTG HS Wakeup through EXTI */ OTG_HS_IRQHandler, /*!< 77: USB OTG HS */ DCMI_IRQHandler, /*!< 53: DCMI */ CRYP_IRQHandler, /*!< 53: CRYP crypto */ HASH_RNG_IRQHandler, /*!< 53: Hash and Rng */ FPU_IRQHandler /*!< 53: FPU */ }; /** * @brief This is the code that gets called when the processor first * starts execution following a reset event. Only the absolutely * necessary set is performed, after which the application * supplied main() routine is called. * @param None * @retval None */ void Default_Reset_Handler(void) { /* Initialize data and bss */ unsigned long *pulSrc, *pulDest; /* Copy the data segment initializers from flash to SRAM */ pulSrc = &_sidata; for(pulDest = &_sdata; pulDest < &_edata; ) { *(pulDest++) = *(pulSrc++); } /* Zero fill the bss segment. This is done with inline assembly since this will clear the value of pulDest if it is not kept in a register. */ __asm(" ldr r0, =_sbss\n" " ldr r1, =_ebss\n" " mov r2, #0\n" " .thumb_func\n" "zero_loop:\n" " cmp r0, r1\n" " it lt\n" " strlt r2, [r0], #4\n" " blt zero_loop"); #ifdef USED_FPU /* Enable FPU.*/ __asm(" LDR.W R0, =0xE000ED88\n" " LDR R1, [R0]\n" " ORR R1, R1, #(0xF << 20)\n" " STR R1, [R0]"); #endif /* Call the application's entry point.*/ main(); } /** *@brief Provide weak aliases for each Exception handler to the Default_Handler. * As they are weak aliases, any function with the same name will override * this definition. */ #pragma weak Reset_Handler = Default_Reset_Handler #pragma weak NMI_Handler = Default_Handler #pragma weak HardFault_Handler = Default_Handler #pragma weak MemManage_Handler = Default_Handler #pragma weak BusFault_Handler = Default_Handler #pragma weak UsageFault_Handler = Default_Handler #pragma weak SVC_Handler = Default_Handler #pragma weak DebugMon_Handler = Default_Handler #pragma weak PendSV_Handler = Default_Handler #pragma weak SysTick_Handler = Default_Handler #pragma weak WWDG_IRQHandler = Default_Handler #pragma weak PVD_IRQHandler = Default_Handler #pragma weak TAMP_STAMP_IRQHandler = Default_Handler #pragma weak RTC_WKUP_IRQHandler = Default_Handler #pragma weak FLASH_IRQHandler = Default_Handler #pragma weak RCC_IRQHandler = Default_Handler #pragma weak EXTI0_IRQHandler = Default_Handler #pragma weak EXTI1_IRQHandler = Default_Handler #pragma weak EXTI2_IRQHandler = Default_Handler #pragma weak EXTI3_IRQHandler = Default_Handler #pragma weak EXTI4_IRQHandler = Default_Handler #pragma weak DMA1_Stream0_IRQHandler = Default_Handler #pragma weak DMA1_Stream1_IRQHandler = Default_Handler #pragma weak DMA1_Stream2_IRQHandler = Default_Handler #pragma weak DMA1_Stream3_IRQHandler = Default_Handler #pragma weak DMA1_Stream4_IRQHandler = Default_Handler #pragma weak DMA1_Stream5_IRQHandler = Default_Handler #pragma weak DMA1_Stream6_IRQHandler = Default_Handler #pragma weak ADC_IRQHandler = Default_Handler #pragma weak CAN1_TX_IRQHandler = Default_Handler #pragma weak CAN1_RX0_IRQHandler = Default_Handler #pragma weak CAN1_RX1_IRQHandler = Default_Handler #pragma weak CAN1_SCE_IRQHandler = Default_Handler #pragma weak EXTI9_5_IRQHandler = Default_Handler #pragma weak TIM1_BRK_TIM9_IRQHandler = Default_Handler #pragma weak TIM1_UP_TIM10_IRQHandler = Default_Handler #pragma weak TIM1_TRG_COM_TIM11_IRQHandler = Default_Handler #pragma weak TIM1_CC_IRQHandler = Default_Handler #pragma weak TIM2_IRQHandler = Default_Handler #pragma weak TIM3_IRQHandler = Default_Handler #pragma weak TIM4_IRQHandler = Default_Handler #pragma weak I2C1_EV_IRQHandler = Default_Handler #pragma weak I2C1_ER_IRQHandler = Default_Handler #pragma weak I2C2_EV_IRQHandler = Default_Handler #pragma weak I2C2_ER_IRQHandler = Default_Handler #pragma weak SPI1_IRQHandler = Default_Handler #pragma weak SPI2_IRQHandler = Default_Handler #pragma weak USART1_IRQHandler = Default_Handler #pragma weak USART2_IRQHandler = Default_Handler #pragma weak USART3_IRQHandler = Default_Handler #pragma weak EXTI15_10_IRQHandler = Default_Handler #pragma weak RTC_Alarm_IRQHandler = Default_Handler #pragma weak OTG_FS_WKUP_IRQHandler = Default_Handler #pragma weak TIM8_BRK_TIM12_IRQHandler = Default_Handler #pragma weak TIM8_UP_TIM13_IRQHandler = Default_Handler #pragma weak TIM8_TRG_COM_TIM14_IRQHandler = Default_Handler #pragma weak TIM8_CC_IRQHandler = Default_Handler #pragma weak DMA1_Stream7_IRQHandler = Default_Handler #pragma weak FSMC_IRQHandler = Default_Handler #pragma weak SDIO_IRQHandler = Default_Handler #pragma weak TIM5_IRQHandler = Default_Handler #pragma weak SPI3_IRQHandler = Default_Handler #pragma weak UART4_IRQHandler = Default_Handler #pragma weak UART5_IRQHandler = Default_Handler #pragma weak TIM6_DAC_IRQHandler = Default_Handler #pragma weak TIM7_IRQHandler = Default_Handler #pragma weak DMA2_Stream0_IRQHandler = Default_Handler #pragma weak DMA2_Stream1_IRQHandler = Default_Handler #pragma weak DMA2_Stream2_IRQHandler = Default_Handler #pragma weak DMA2_Stream3_IRQHandler = Default_Handler #pragma weak DMA2_Stream4_IRQHandler = Default_Handler #pragma weak ETH_IRQHandler = Default_Handler #pragma weak ETH_WKUP_IRQHandler = Default_Handler #pragma weak CAN2_TX_IRQHandler = Default_Handler #pragma weak CAN2_RX0_IRQHandler = Default_Handler #pragma weak CAN2_RX1_IRQHandler = Default_Handler #pragma weak CAN2_SCE_IRQHandler = Default_Handler #pragma weak OTG_FS_IRQHandler = Default_Handler #pragma weak DMA2_Stream5_IRQHandler = Default_Handler #pragma weak DMA2_Stream6_IRQHandler = Default_Handler #pragma weak DMA2_Stream7_IRQHandler = Default_Handler #pragma weak USART6_IRQHandler = Default_Handler #pragma weak I2C3_EV_IRQHandler = Default_Handler #pragma weak I2C3_ER_IRQHandler = Default_Handler #pragma weak OTG_HS_EP1_OUT_IRQHandler = Default_Handler #pragma weak OTG_HS_EP1_IN_IRQHandler = Default_Handler #pragma weak OTG_HS_WKUP_IRQHandler = Default_Handler #pragma weak OTG_HS_IRQHandler = Default_Handler #pragma weak DCMI_IRQHandler = Default_Handler #pragma weak CRYP_IRQHandler = Default_Handler #pragma weak HASH_RNG_IRQHandler = Default_Handler #pragma weak FPU_IRQHandler = Default_Handler /** * @brief This is the code that gets called when the processor receives an * unexpected interrupt. This simply enters an infinite loop, * preserving the system state for examination by a debugger. * @param None * @retval None */ static void Default_Handler(void) { /* Go into an infinite loop. */ while (1) { } } /*********************** © COPYRIGHT 2009 Coocox ************END OF FILE*****/ Что значит: 1. #pragma weak NMI_Handler = Default_Handler 2. void WEAK Reset_Handler(void); (WEAK) ???? :blink: В регистрах такие значения: xpsr 0x61000003 lr 0xfffffff9 //???? sp 0x1fffbfe0 -

Чудеса оптимизации кода GCC-ARM

Zol'berg ответил Zol'berg тема в ARM, 32bit

Да, я все равно никак не пойму что такое и как работает bitband применительно к СЧИТЫВАНИЮ порта, с регистром BSRR(BSRRL и BSRRH) я знаком! Если я не ошибаюсь bitband это метод установки/сброса и никак не касается считывания!? Ну, а SPI_MISO() из чего сделано? -

Чудеса оптимизации кода GCC-ARM

Zol'berg ответил Zol'berg тема в ARM, 32bit

Ну, к регистру IDR необходимо применять маску, я так и делаю, а это время, а 5 MHz SCK это много! Когда я работал на Асме на AVR было четко и ясно, за 2 такта я мог опросить любой бит одной командой, а тут за 8 еле еле, и C компилятор живет своей жизнью, хочет разгоняет, а хочет тормозит! И что делать? В функции SSS() вполне достаточно одного цикла на все 4 канала Да, ты прав, наворотил я здесь . -

Чудеса оптимизации кода GCC-ARM

Zol'berg ответил Zol'berg тема в ARM, 32bit

Может я чего не пойму, но у меня только приемник (slave), т.е. я не управляю, а слежу за состоянием SCK и NSS, и параллельно снимаю 4 потока данных, И не пойму, как реализовать проверку состояния порта через bitband (Ваш SPI_MISO())??? P.S. Все те угрюмые навороты в моей проге только по причине нехватки скорости (проверка состояния входа через маску - ~40 ns) , как через bitband проверить, ведь регистр BSRR только для установки и сброса !?? -

Чудеса оптимизации кода GCC-ARM

Zol'berg опубликовал тема в ARM, 32bit

Всем привет!! 1. Из инструментов при себе имею STM32F407 - Discovery, CooCox и осцилл (2ch x 100MHz). 2. Задача: захватить 16 разрядные данные с ADC (4 канала) по протоколу SPI при тактовой частоте 5MHz (CLK). 3. Решение: программная реализация протокола ввиду наличия лишь 3_ёх SPI в STM32F407 и некоторых отклонений входного потока от стандарта SPI (исходные условия), при тактовой в 168 MHz хватает впритык и только с оптимизатором -O3. Программка выглядит так: // Соответствие функций входных линий и ножек порта: #define SCK 1<<4 #define NSS 1<<5 #define MOSI_SPI0 1<<0 #define MOSI_SPI1 1<<1 #define MOSI_SPI2 1<<2 #define MOSI_SPI3 1<<3 #define N_DATA 10 // количество данных (выборок) uint16_t DATA_0[N_DATA]; // Массив отсчетов для 0_го канала uint16_t DATA_1[N_DATA]; // Массив отсчетов для 1_го канала uint16_t DATA_2[N_DATA]; // Массив отсчетов для 2_го канала uint16_t DATA_3[N_DATA]; // Массив отсчетов для 3_го канала uint16_t DATA_temp[16]; // Буфера для сохранения состояний порта, (для повышения быстродействия) uint16_t N_Data; // Счетчик/номер текущего отсчета в периоде захвата или выдачи данных uint8_t i; // Само собой разумеется void SSS(void) // Ф-ия преобразования сохраненных состояний порта DATA_temp[i] в отчеты DATA_0-3[N_Data] { i=0; DATA_0[N_Data] = 0; while(i<16) for(i=0;i<16;i++) { if((DATA_temp[i] & MOSI_SPI0 == MOSI_SPI0) ) DATA_0[N_Data] |= (0x8000>>i); i++; } i=0; DATA_1[N_Data] = 0; while(i<16) { if((DATA_temp[i] & MOSI_SPI1) == MOSI_SPI1) DATA_1[N_Data] |= (0x8000>>i); i++; } i=0; DATA_2[N_Data] = 0; while(i<16) { if((DATA_temp[i] & MOSI_SPI2) == MOSI_SPI2) DATA_2[N_Data] |= (0x8000>>i); i++; } i=0; DATA_3[N_Data] = 0; while(i<16) { if((DATA_temp[i] & MOSI_SPI3) == MOSI_SPI3) DATA_3[N_Data] |= (0x8000>>i); i++; } } void Flag(void) // Ф-ия "Флаг" - "контрольная точка" { GPIOD->BSRRL =(1<<14); // set GPIOD->BSRRH =(1<<14); // clr } void ProgramSPI(void) // Программная реализация SPI где D0-MOSI(SPI0)|D1-MOSI(SPI1)|D2-MOSI(SPI2)|D3-MOSI(SPI3) D4-SCK D5-NSS { N_Data=0; { while ((GPIOD->IDR & NSS) == 0)// NSS==0 (ждем начала выполнения преобразования ADC) {} while ((GPIOD->IDR & NSS) == NSS)// NSS==1 (ждем окончания выполнения преобразования ADC) {} // Flag(); // Процесс захвата данных (SPI0-3): i=0; while (i<16) { while ((GPIOD->IDR & (NSS|SCK)) != SCK) // SCK!=1|NSS==0 {} Flag(); DATA_temp[i]=GPIOD->IDR; Flag(); while ((GPIOD->IDR & (NSS|SCK)) != 0) // SCK!=0|NSS==0 {} // Flag(); i++; } SSS(); // Проверка принятых байтов: if((DATA_0[N_Data]!= 0xA38C) | (DATA_1[N_Data]!= 0xA38C) | (DATA_2[N_Data]!= 0xA38C) | (DATA_3[N_Data] != 0xA38C)) { Flag(); } N_Data++; // Инкремент счетчика отсчетов - подготовка к следующему полуслову if(N_Data==N_DATA) return; // Переполнение буфера данных, возврат в main() } } int main(void) // Очень странная функция !!!;) { SystemInit(); PortD_Init(); while(1) { ProgramSPI(); } } В общем все работает, ф-ия Flag() - контрольная точка (выводит строб на порт который контролируется осциллографом), ProgramSPI() сохраняет состояние ножек порта в нужное время 16 раз, ф-ия SSS() преобразует данные, но есть одно НО, при подключении вызова ф-ии SSS() компилятор отказывается оптимизировать код в сторону быстродействия, т.е. другими словами - в случае применения где либо этих массивов, скорости не хватает и появляются ошибки чтения. Пытался применять квалификаторы типа volatile и restrict, не помогло. Вопрос: как заставить компилятор оптимизировать или не оптимизировать нужные мне куски кода?? Спасибо :) -

Непонятные ошибки при компиляции

Zol'berg ответил allsettingsdone тема в ARM, 32bit

Спасибо за развернутый ответ, ценю!!! :a14: ЖесТЯЯЯЯК, я в шоке, неделю бьюсь над быстродействием, применял Bit-bang, но все равно на установку бита в порту уходило не менее 6 тактов, а на проверку состояния и прерывание - воще гора и это все при -O0 оптимизаторе, но РЕВОЛЮЦИЯ в моем осознании наступила, стоило мне переключить с -O0 на -O1, и на установку бита в порту теперь 1 такт, я об этом даже не мечтал, все вспоминал 2 такта ATMEG_и )). А как правильно организовать проверку бита в порту (в плане максимального быстродействия) ?))))). И какими средствами в CooCox или еще где, определить количества тактов на команду, можно ли сделать"виртуальный" Debug без контроллера, как в AVR-studio? P.S. Количество тактов рассчитано примерно при помощи осцилла))) -

Непонятные ошибки при компиляции

Zol'berg ответил allsettingsdone тема в ARM, 32bit

Глобальные и локальные переменные мне знакомы, работают по разному, но суть одна-в том, что работать должно и так и так ( и глобальные для всех функций инициализации и локальные - в каждой функции свои), а по поводу "медленных примеров", я не только/только начал изучение STM32, для меня и C нов, т.к. ранее работал с AVR на ассемблере! А как сделать быстрее, писать конфигурацию прямо в регистры? В моем проекте инициализацию можно провести медленно. Но есть другой вопрос, уже наверное не по теме : как добиться быстрой работы с портами, ассемблерные вставки? Так не могу найти описания этих самых команд для STM32F4! Может есть темы на эту тему?))