ASDFG123

-

Постов

199 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные ASDFG123

-

-

22 hours ago, oleg-n said:

Кстати , а кабели heliax 1/2 по отношению к обычным серии LMR не ломкие ? Какие минусы есть ?

Есть минус, их должны монтировать те у кого руки не из жопы растут, очень требовательны, еще разъемы от разных производителей по разному монтируются. Рекомендую и кабель и разъем от одного производителя брать и лучше с комплектом инструментов для монтажа.

Эти кабели как и любые другие со сплошной экранировкой не любят сгибы туда сюда, один раз согнули как он должен стоят и не трогайте. И перегрев не любят, у них наполнитель довольео легко плавится и стекает.

-

On 2/27/2024 at 8:07 PM, Александр Мылов said:

Если точно, то в 3D симуляторе.

Какие частоты?

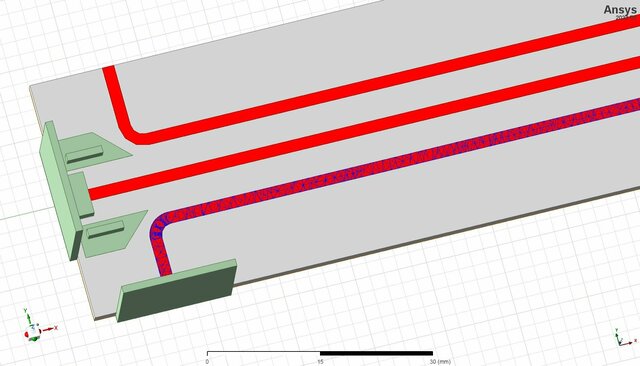

Частота 200Мгц. Да я как раз в 3д рассчитывал и не совпадают результаты. Линия именно полосковая, две земли сверху и снизу и полосок во внутреннем слое. Разъемы ставятся на корпус, и только вывод на площадку платы. Из ограничений еще большая проходная мощность.

Документ просмотрел Optimizing_Test_Boards_End_Launch там как раз микрополосок (CBCPW), а вот по подключению полосковых линий практически ничего нету.

-

Опубликовано · Изменено пользователем ASDFG123 · Пожаловаться

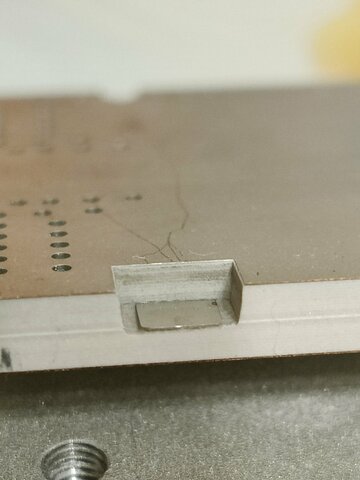

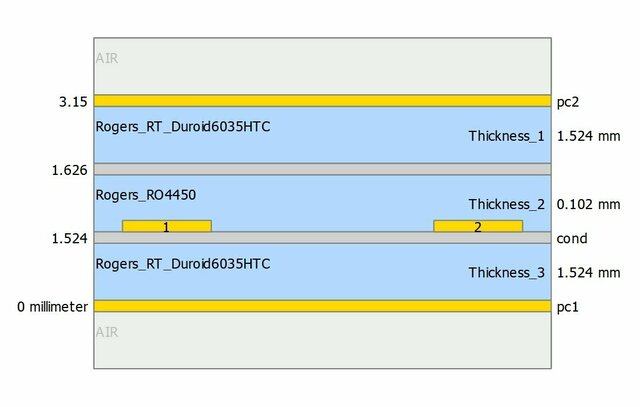

Здравствуйте, есть вопросы по плате выполненной в виде симметричной полосковой линии. Стэк: медь 1 слой, ламинат 1 слой, медь 2 слой (внутренний), препрег, ламинат 2 слой, медь 3 слой. Основной момент это подключение ВЧ разъема к плате, для этого в фаиле я сделал границу платы на втором слое с вырезами под вывод разъема. По сути переход от полосковой линии к микроплосковой линии. Также фото готовой платы, там явно что то не то, вырез имеет явный скос и вообще не выглядит технологичным, как будто его вырезали на готовой плате уже после спекания с препрегом. Как вообще подобная задача решается? Возможно со стороны дизайна как то можно внести изменения либо же это косяк производителя?

Ну и попутно можно ли как то определить что производитель не обманул и применил тот ламинат что нужно, а не похожий по хар-кам?

-

Опубликовано · Изменено пользователем ASDFG123 · Пожаловаться

Если актуально, то делаете алюм фрезерованную пластину куда ставится резистор и 2 фланцевых разъема (желательно покороче) и замеряете sparam, сохраняете и используете в модели заместо идеального резистора, до частоты 500-600 Мгц делитель будет сходиться модель-реальность. А больше даже сам резистор плохо будет работать так как у него больше 13 пф паразитной емкости.

А еще чтобы скомпенсировать это в делителе вилкинсона, надо параллельно припаять с каждого вывода резистора индуктивность на землю.

-

Это вообще не то, на фото микрополосковая линия

-

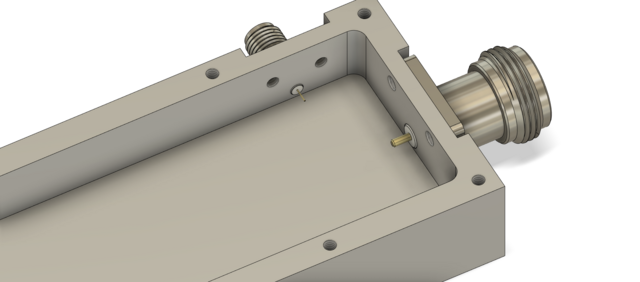

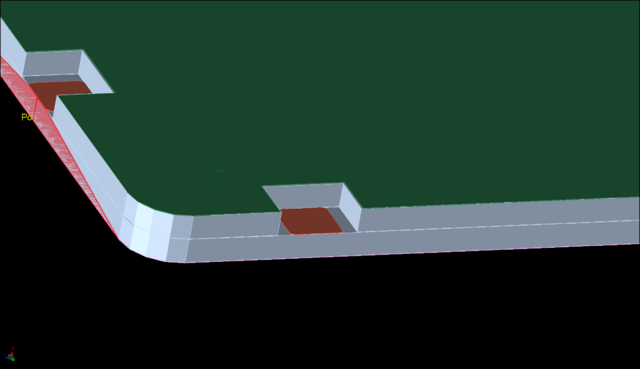

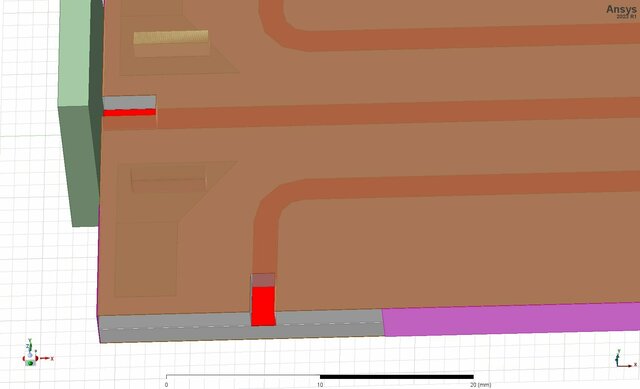

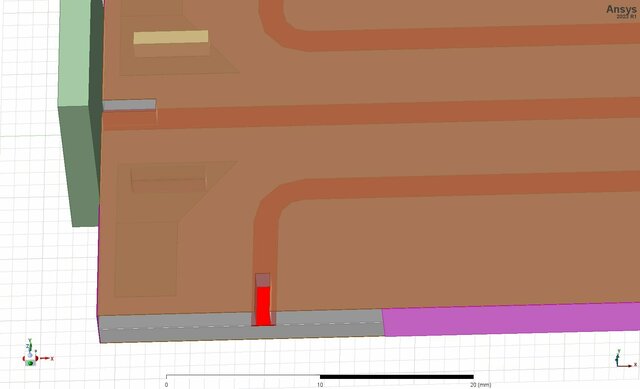

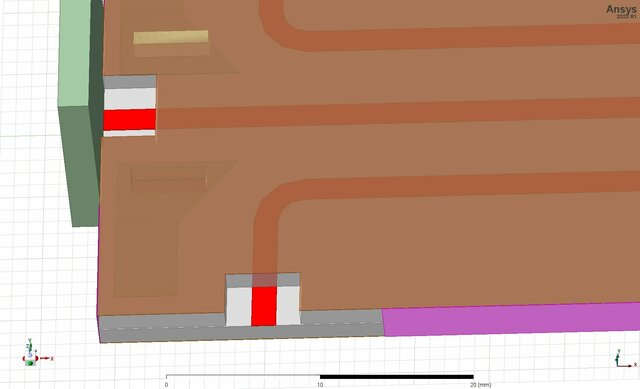

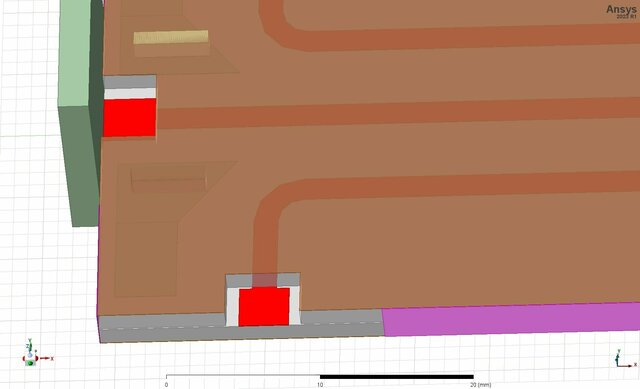

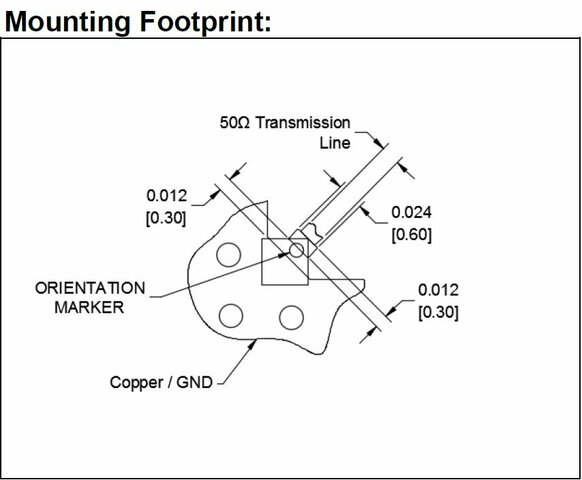

Проектирую направленный ответвитель на симметричной полосковой линии и не получается разобраться с подсоединением разъема к плате. Разъем типа такого, фланец на фрезерованный корпус, длина тефлоного цилиндра 3,18мм. На скриншотах ниже возможные варианты, по моделированию в hfss у меня есть сомнения что я сделал правильно так как результаты сильно прыгают. Ширина полоска в теории SL ~1.6mm, MS ~3.3mm. Еще вопрос по резистору 50 Ом, как лучше его подключить. На скриншотах в верхней половине платы вырезы под разъемы, пин разъема припаивается прямо на центральный слой.

Какие варианты из практики лучше? Также волнует момент реализуемости, тестовые платы заказали с расчетом переход полосковая-микрополосковая линия, с падом 3.3 мм и шириной окна 5мм, так вот вырез получился трапециевидный и у внутреннего слоя был 4.4 мм вместо 5 мм.

Самый важный параметр это изоляция портов для достижения хорошей направленности, в тестовом экземпляре всего 16 дБ и это очень плохо, хотя ADS показывал что будет около 30 дБ. (Я уже делал ответвители на "коленке" просто прикручивая две платы и стягивая металлическими пластинами и у них было 28-29 дБ)

-

да менял lambda target, поставил 0.08. также выделял отдельные элементы и правой кнопкой и в меню mesh задавал отдельные параметры типа length based, но както не особо помогло. Где то в видео видел что автоматика сама уплотняет сетку, особенно на краях элементов, но только не помню был ли это hfss или cst.

-

-

Есть вопрос про смесители, конкретно RAY-1 сборка двойной балансный смеситель RAY-1+.pdf . Как его правильно согласовать? Допустим с LO туда подаем +23 dBm сигнал, особо не согласуя, RF по даташиту уже хорошо согласован. А вот с IF есть вопросы, он не очень, КСВ 2, как поступить в данном случае?

Первое как мне кажется надо измерить сопротивление на этом порту, но повторить измерения Mini-Circuit я не могу, нет оборудования. Можно ли подать на LO +23 dBm, RF заглушить на 50 Ohm и измерить IF в режиме S11 векторного анализатора?

Второе, допустим у меня есть сопротивление порта, должен ли я подгонять фильтр IF под это? да и по самому фильтру есть вопросы, насколько я понял лучше всего применять reflection-less фильтры, но есть ли они на диапазон 15-20 MHz?

-

Plain Спасибо, надо попробовать.

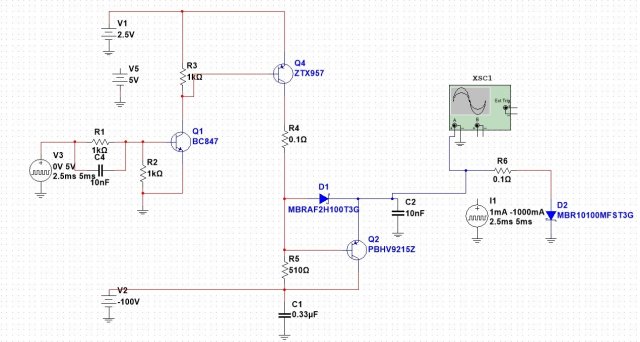

По применению ОУ тоже думал, но применять придется те у кого размах питания> 150V а это все таки совсем не стандартная штука.

-

-

Здравствуйте, подскажите схемотехнику для реализации ключа коммутатора. Положительное напряжение +2,5V 1A, а отрицательное -150V 1mA. Коммутировать надо поперемерно в одну точку. Управление +5 и 0. Я сделал схему на трех транзисторах, но работает не ахти, скорость нарастания отрицального напряжения очень медленая, нужно чтобы каждый фронт в течении стаблилизовался в течении 1 - 1,5 мкс. Пока незнаю в какую сторону смотреть. Навярняка есть способ реализовать схему, может не на транзисторах а на микросхемах или что нибудь другом.

-

А как отредактировать библиотеки в два клика? У меня созданы две библиотеки под схемы и под футпринты. Через PCBLIB filter выделил пады на TopLayer и поменял свойства всех падов на 10% округление, явно не два клика заняло, но результа вроде добился. Полигоны стали округленными, а на падах 10% почти не сказалось.

-

7 minutes ago, Uladzimir said:

Сделайте площадки Round Restance. Если хотите чтобы выглядели прямоугольными -- поставьте радиус закругления почти нулевой

То есть перелопатить все библиотеки и там поменять пады? А другого способа нет?

-

-

12 hours ago, Prostograf said:

Господа проблема с подключением модели мощного транзистора MRFE6VP6300. К ней там еще прилагается модуль FSL_Tech_Include, куда его сувать?

А можете скрины выложить? Вообще там просто модуль, на лист схематика его ставите и дальше вытаскиваете символ транзистора. На сайте frescale (nxp) была инструкция как подлючать design kit и как пользоваться.

-

И еще добавлю вы плату под усил. проверяли в чем нб типа ADS? Я как то моделировал плату от такого усилка (планарный балун) и ничего хорошего не получилось, дизайн от Frescale ущербный, особенно входной балун. Еще возможно что усилитель в режиме условно стабильный, и когда вы свипаете анализатором то начинается возбуд. Нужно проверить в программе К коеф. стабильонсти.

Попробуйте использовать стабильный источник сигнала на 50 Ом и контролировать осцилом после аттенюатора, все на сниженой мощности. Если также сгорит, то проблема в плате.

-

dee2mon,

Спасибо, вроде разобрался

И еще смотреть на K и дельту нужно в диапазоне где у усисилителя S21 больше нуля дБ.

-

Что касается входа, то эти транзисторы держат несколько Ватт мощности, анализатор даже физически не создат столько. Можно даже дискретный ограничитель мощности по входу поставить. Я думаю что проблема не в этом.

На выходном балуне индуктивность повторена 1 в 1 ? Кондеры балансира тоже? То что сгорает один и тот же транзистор говорит о некоем дисбалансе.

-

Подходит ламинат RT6035HTC без переделки, даже лучше чем TC350. По схеме затвора в аппноуте на усилитель 230 МГц у них есть схема контроля за напряжением и током, на 108 Мгц схеме этого нет.

Вот "Использую в качестве источника сигнала VNA в режиме качания мощности" момент непонятен, все равно ведь выход усилителя не подключить к VNA. Вам нужна мощная нагрузка 50 Ом и направленный ответвитель для контроля мощности.

Транзистор припаяли к медной подложке? Или хотя бы использовали проводящую термопасту.

-

On 7/9/2021 at 5:31 PM, cismoll said:

Проблема так и продолжает воспроизводится, к сожалению.

Усилитель спокойно работает при входных мощностях до 1 Вт, КУ более-менее соответствует приведённому в даташите, но вот только что при превышении Pin = 1,2 Вт сгорел затвор. Интересно, к слову, что это происходит всегда у одного и того же затвора из пары. ПП не припаяна, но плотно прижата винтами к радиатору, между медным фланцем и радиатором слой термопасты.

А вы купили прототип усилителя или сами по "мотивам" сделали? Есть ли 10 Ом резистор в цепи bias затвора? и еще резисторы c каждого затвора на вч землю (стаб. цепочка)?

-

ATC еще можно посмотреть Knowles.

-

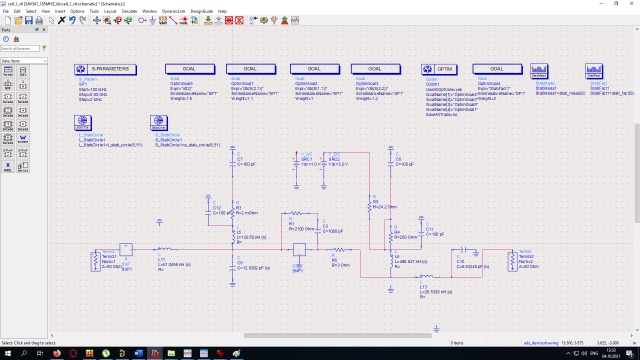

Есть вопрос по правильности симуляции стабильности LNA. Моделирую усилитель по Small signal S-param. Собрал схему в ADS вывел параметры StabFact.

В общем есть участки когда StabFact меньше 1, чем грозит режим Conditionally stable?

И еще более важный вопрос, я планирую ставить еще защиту (ограничитель) по мощности RLM-63-2W, и когда я симулирую вместе с ним то StabFact всегда больше 1. Скрин сим окна во вложении. Ограничитель мощности ставлю между П1 и МШУ. Правильна ли такая симуляция учитывая что измерения StabFact проводятся между портами 1-2?

-

Проверил MJF PP в общем это лучший 3д пластик в качестве диэлектрика RF, намного лучше чем смола или ABS, хотел еще проверить SLS PP, но не получилось.

Вопрос по направленным ответвителям

в RF & Microwave Design

Опубликовано · Пожаловаться

dircopl нужна полосковая стурктура, на микрополоске даже 15 дБ направленности не добьётесь без ухищрений.