-

Постов

535 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные topor_topor

-

-

Доброго времени суток. Решил стать программистом :) и заодно изучить связку STM32\FreeRTOS\C++.

Хочу запустить драйвер (LCD с I2C напр.) в отдельном таске FreeRTOS, потому что очень медленная комуникация.

Драйвер написан как С++ класс. Доступ к методам объекта драйвера (разны команды к LCD) соответственно с другого (MAIN) таска.

Просто очередь для обмена командами не подходит, ибо это не поток данных а разнообразные (разно форматные, с разным набором параметров) команды.

++++++++++++

Подскажите пожалуйста есть ли какие стандарты (или красивые способы) для организации доступа к методам такого объекта-драйвера с других тасков?

Может есть стандартный интерфейс драйверов для таких случаев?

-

10 hours ago, yes said:

на всякий случай, проблема с латчами - это петли обратной связи (feedback loop). что, например, будет если между входом и выходом латча будет инвертор? ну или xor или любая другая логика, куда заведены выходы...

поэтому их и не любят :)

Ту не вопросс любви а просто SDC: set_disable_timing

Если латч имеется ввиду два гейта а не нормальній латч....

10 hours ago, demidrol said:а зачем блочную память (даже набранную из триггеров) включать в скан-цепочку? Почему ее обычными BIST не тестировать?

я ж предлагаю по границе памяти поставить обычные триггеры. Понятно, что латчи требуют повышенной аккуратности.

1) Мы же вроде хотим маленькую память с набора тригеров так? А размер BIST контроллерра он какой по сравнению с маленькой памятью? Всё тут относительно конечно.

2) Не поможет. STA на feedback loop будет шипко ругаться на латч в виде двух гейтов.

-

С латчами одна проблема - они не скан пригодны.

Т.е. DFT их автоматом не протестит. Но кто мешает функционально как и память?

STA хавает без проблем по дефолту. Можно тайминги расслабить (time borrowing). Никаких проблем с клок три итп.

-----

В тест енкаунтере вроде есть поддержка теста латчей... но это не совсем автоматом - надо специальный импульс наружу выводить.

У меня чёт не вышло латчи в енкаунтере покрыть ATPGми. Если у кого вышло - научите.

-

On 4/15/2019 at 5:50 PM, baumanets said:

Часть вопросов тестирования закрывает продукция многим известной ФОРМ.

Кому компания не известна, зайдите к ним на сайт:

http://form.ru/products/chip/hf-ultra/

"Дружественное программное обеспечение" к сожалению подробностей разработчик больше не даёт для оценки насколько дружественное...

С\С++ есть? STIL формат принимает?

И опять-же, это только часть тестера микросхем и годится разве для ручного тестирования корпусированных чипов...штук сто в день :)

А тестеры выглядят примерно так:

www.larsenassociates.com/Exatron.html

-

7 hours ago, Tpeck said:

Заказали на производстве опытную партию.

В ней нашли ряд багов по вине создателя RTL, для коррекции этих багов, надо весь техпроцесс заново запускать (тратить те же 20 млн), или это гораздо дешевле уже будет?

Цифра обично что в чипе что в симуляторе идентично работает.

Аналог требует пару итераций с фул маск редизайном.

Цифру верифицировать надо чтоби избежать редизайна. Спаре-сэли внедряются для метал редизайна ибо он раза в два дешевле чем фул маск.

Первие семпели шатлом делают, что много дешевле.

++++++++++++

А в общем да, если в RTL баги то надо весь техпроцесс заново запускать (тратить те же 2 млн $, в некоторых процессах).

Но это не самое страшное :)

При серии 100 млн\месяц и если конечные юзеры нашли баг в RTL то плати бабки - за 1$ цены ввёрнутого назад чипа плати примерно 15000$ а это уже плохие новости :(

-

Как вариант есть куча китайських фирмочек которие делают шатли на старих технологиях до 0.13. Некоторие и аналоговий Тули дают. Можно склепать мелкую серию.... Как минимум демо чип

-

1 minute ago, Tpeck said:

По технологии 0,18 мм в какую цену это может вылиться?

Или подскажите где можно почитать про маршрут проектирования.

Только тут встречал какое-то описание процесса производства.

Спасибо

10 штук ето в shattle. На такий технологии могу предположить тищ 10уе за штук пять....

А вот если есть вопрос сколько тулзи для проектирования стоят, ви сто обойдется подготовка производства итп. Смоирите више

-

On 4/3/2019 at 6:56 AM, Aleх said:

Понял. Проиллюстрирую. Возможно, у вас своя кастом либа, поскольку как правило присутствуют такие флопы, использующиеся для скана:

Для генератора ATPG вообще пофиг как скан цепочка сделана. Хоть прямо в код вписана и синтезина с отдельно флопа плюс мукс, или хоть скан флопы DFT вставлял и в цепь соединял. Более того, шифт регистры DFT тул любит приладить в скан цепь по умолчанию. Вас же не смущает что синтезатор работает бей супер гейтов типа 2AND-3NAND-XOR?

On 4/3/2019 at 6:56 AM, Aleх said:Теперь, что такое самая простая скан-селла BC_2, использующаяся в баундари скан житага

Ставим это на цифровом выходе.

В скан режиме вдуваем значения в левый тригер. Даём одиночный клок пульс на updateDR и записываем всканенное значение в правый тригер - он задаёт режим аналога (как нам давно и надо было). Во время ATPG клок updateDR не дёргаем - аналог тоже не дёргается.

Вход левого тригера подключен к dataIN - т.е. он обзервит выход цифры.

clockDR это SCAN_CLK, scan_in - SCAN_IN, scan_out - SCAN_OUT.

В итоге имеем полноценную ATPG скан цепь которую сожрет ЕТ. Зачем что-то менять на скановские флопы?

-

On 4/3/2019 at 5:13 PM, Reanimatorr said:

Большое спасибо topor_topor за оценку, отрезвляет. и baumanets за техническую информацию!

Тем не менее, я думаю что состав более 3-5 человек именно микросхемщиков для нас избыточен.

Частоты для начала не более 200 МГц. Гигагерцовые идеи/планы тоже имеются, но на это замахиваться надо сначала что попроще сделать хотя бы раз до конца. Техпроцесс полагаю BiCMOS 0.18 мкм. Цифровой емкости логической большой нету, аналоговая часть замороченная.

Если можно дайте подробнее информацию о ПО, можно в ЛС, с учетом нашей специфики, что смотреть, на что мануалы начинать изучать.

Пока нет понятия даже о составе ПО.

На ваш вопрос нельзя дать адекватный и точный ответ из-за неясности задачи.

Что мы имеем:

1) 2 микросхемы в год.

Это до первого опытного образца или передача в производство?

Количество людей разное надо.

2) "Изделия имеют аналоговую специфику, которая даже в дискретных элементах оттачивается разными коллективами десятилетиями." " аналоговая часть замороченная" "Частота первых изделий не более 200 МГц."

Заморочки разные бывают. Тут нужно уточнять что за изделия. Если это RF, то просто. Если это частота переключения импульсного драйвера то много. Если тактовая цифровой схемы - то на 0.18 можно и не вытянуть. У когото сейфти дизайн.

Специфика изделия и определяет набор тулзов. Как и выбор специалистов.

Хоть примерно скажите сколько тригеров в цифре, сколько транзисторов в аналоге.

Но в общем случае вам дали пример:

https://www.cadence.com/content/cadence-www/global/en_US/home/tools/custom-ic-analog-rf-design.html

3) "Цифровой емкости логической большой нету"

Что значит большой нету? Это 20 флопов в АЦП или 5000 флопов DSP схемы? 20 - в аналоговой схематике нарисуете, 5000 - уже надо набор цифровых тулзов и цифровика.

Если вы думаете что 0.18 ОК, то библиотеки и симуляции XTalk\IR-drop в цифре не нужны.

4) Сертифицировать изделие надо или нет? ISO26262 итп.?

Если надо, то шагов больше и тулзы докупить придётся (типа TetraMax для доказательства соответствия стандарту качества напр.).

5) Пекедж надо проектировать или любой сойдёт? Может оптоволокно какое надо через дырку подключать....

6) Какую серию производим?

Если всего 1000шт, то можно забить на правильную верификацию и продакшин тесты, а если 100млн.месяц, то тут и верификацию по полной и тулзы надо.

7) У фаба где будете делать, дезайн киты под какие тулзы заточены?

Cadence\SYnopsys... Особенно если паразиты надо симулить...

8) Тести чипов (пластины\в пекедже) на каком оборудовании делать будем? Какой тип тестера?

Их писать комунить надо, а тестер может на вижуал бейсике работать и STIL формат не хавать.

9) Ну и тесты микросхемо-специфические типа ESD\EMC есть кому и где делать? Ну и тд.и т.п

+++++++++++++++

Я вот до сих пор совета умного дать не могу.

Пока что, ответ где-то между одним Virtuoso и полным набором для аналога и цифры. И порядок стоимости лицензий между 50к-1.5млн уе

Пытаться изучать какуюнить тулзу смысла не вижу (тем более без спец тренингов сложноваты).

Как и спорить о том лицензионный редхет брать или центос, брать conformal или нет...

Догм в выборе шагов маршрута проектирования для адекватных людей нет, главное понимать что делается в какой тулзе и что это реально даст.

Есть и большие корпорации которые гнушный SVN юзают и CentOS не брезгуют.

P/S Если купить все озвученные тут тулзы то вы по миру пойдёте и работать со всем этим замучаетесь.

-

2 minutes ago, Aleх said:

Шутите? У скан флопов расширенный состав пинов (встроен мультиплексор по входу). Может быть скан можно и на обычных флопах сделать, но я ни разу такого не видел, имел дело только со стандартными библиотеками, где скан флопы обязательно присутствуют.

Уж поверьте на слово

-

1 hour ago, alexunder said:

С characterization, т.е. тестированием, тоже есть свои нюансы. На начальной стадии проекта все спецификации должны быть обозначены и задокументированы, включая методики их тестирования и измерения. .......

Это не самое главное.

1 hour ago, alexunder said:Существуют компании, которые выполнят для Вас все перечисленные этапы "под ключ", включая разработку тестовой системы (платы-хоста для вашей ИМС), bring-up, полный цикл измерений, в т.ч. wafer testing. От Вас потребуется только хорошая документация на проект. Возможно, для вашей фирмы на начальном этапе деятельности такой аутсорс будет лучшим вариантом.

Ага, только все "тест паттерны им сразу дай" и отдебагай по месту....

А хорошая документация это хорошо, только ещё минимум 50% к рабочему времени каждого дизайнера накинет....

-

2 minutes ago, Aleх said:

Баундари скан джитага содержит не скан-флопы, а любые. В общем случае это обычные флопы.

А чем скановский флоп от любого отличается?

Я вот всегда беру простые флопы, синтезю и они как-то в DFT цепочку внедряются....

-

1 hour ago, Reanimator++ said:

Люди, понимающие специфику, имеются. Полностью отсутствуют люди по микросхемному техпроцессу, и понимание пути проектирования изнутри, т

....

Самый большой вопрос по софту. Как я понимаю он составляет основной вес в данном вопросе. Если можно, поясните поподробнее и дайте варианты куда рыть. Пока что я не в состоянии позвонить и корректно объяснить что нужно, чтобы получить информацию о стоимости.

.....

По итогу обсуждения мне нужны две цифры - стоимость первоначальных вложений (софт, сервера, оборудование, трансфер специалистов), и стоимость текущих расходов (зарплаты, семплы, что-либо еще). Дальше уже пусть вершители судеб решают, надо им это или нет.

Ух, Эх... (это я шашкой махнул :))

Начнём с самого сночала.

1) Немного смутила формулировка "Изделия имеют аналоговую специфику, которая даже в дискретных элементах оттачивается разными коллективами десятилетиями." Тут-бы уточнить что это такое.

Предположу что это какиенить гигагерцовые синтезаторы частот... А тут ответ такой - тоже самое но сделать в микросхеме ваще хана как сложно :) Людей которые это умеют пара штук на весь мир с ЗП от 200 000 $ год. Называются principal architect. Сейчас 5G дизайнят.

Ординарный аналоговый дизайнер тут ну никак не подойдёт...

По цифре проще но сложность не понятна.

2) Если нашли эксперта по пункту 1), то дальше проще.

Две микросхемы параллельно где-то за год это надо людей примерно:

- analog architect (руководить дизайнерами и писать ТЗ на аналог, с учётом микросхемного техпроцесса) - 90 000$/year

- digital architect (руководить дизайнерами и писать ТЗ на цифру) - 90 000$/year

- 2-3 senior analog designer на один чип (дизайн, DFT, характеризация и верификация) - 65 000$/year

- 1-2 senior digital designer на один чип (дизайн, DFT и верификация) - 60 000$/year

- 1 analog layout engineer на два чипа - 50 000$/year

- 1 digital back-end engineer на два чипа (этого можна зааутсорсить) - 55 000$/year

- 1 test engineer (производство будем масовое делать?) - 60 000$/year

- пекедж (стандартний фаб влепит), разработка ємбедыд софта, административка, командировки - не надо - 0$

Итого ЛЮДИ - 17шт\1.3 МЛН USD

- САПР лицензии (без них заграничные фабы не возьмут) на год на все тулзы - около 1.3 МЛН USD

- пару редизайнов (гигагерцовый аналог он такой) около 800 000 USD на раз попробовать....итого 3МЛН USD

Сумарно в год: около 2.5 МЛН USD+3 МЛН USD=6МЛН USD год

От идеи до масс продакшина берите минимум 2 года (если чип тупо ординарный) и года 3-5 если реально что-то новое

Итого R&D двух чипов около 12 МЛН USD за 2 года.

Это по божески. Обычно 10 МЛН USD за 2 года на один чип.

P.S Сервера, канцелярка, картриджи в принтер и кофемашины ваще сто-десятое дело....

-

15 hours ago, Aleх said:

Баундари цепочка житага работает в режимах intest и extest. Очевидно, что если вы хотите задавать константы на аналог, то 1. нужен extest, 2. прошивать сканами тап контроллер и саму баундари скан чейн - нельзя, и триггеры, входящие в эти структуры нельзя сделать скановыми.

Всё верно кроме одного - баундари цепочка и состоит собственно из сканових тригеров - она-ж сканится :)

Берем баундари цепочку (ту часть что на выходах цифры) и в режиме extest устанавливаем константу перед началом ATPG теста - "аналог в режиме ATPG".

Залачиваем это состояние в латче баундари цепочки (баундари селы на выходах двойные - латч плюс тригер, тип по стандарту не помню...). Теперь можем использовать ее скановые тригеры как +1 скан цепь при ATPG, которая обзервит выход цифры.

Состояние аналоговых выходов нас не интересует во время ATPG. Поэтому часть баундари цепи на входах цифры можно просто использовать как +1 скан цепь при ATPG, которая драйверит вход цифры.

Понимая что есть +2 скан цепи (плюс к N штук внутри самой цифры), ЕТ их должен использовать чтобы автоматом драйверить входы цифры и обзервить выходы.

=============================

В результате имеем быстрий самоклокающийся (можна осцилятор отрубить) стандартный тестовый интерфейс. Используем баундари цепь для теста аналога на борту, и для драйва\обзерва входов\выходов цифры при ATPG. А также имеем внутренние скан цепи подключенніе к нему-же без дополнительных падов на корпусе. Всё в одном флаконе.

=============================

Поэтому и был вопрос:

Кто ни будь использовал JTAG боундари скан при генерации ATPG чтобы стимулировать входы и читать выходы цифры вместе со встроенными в цифру скан цепями?

-

23 hours ago, Aleх said:

Таки, а что же вы хотите генерить с помощью ЕТ?

Чтобы просто получить вектор, который задвигает в житаг баундари скан некое состояние на линиях, можно написать простенькую прогу. На входе у нее будет желаемое состояние входов аналога, а на выходе полный вектор для тестера. Когда я занимался этой темой, то подобные проги и отдельные вектора для джем-плеера писал за 20-30 минут. Полученный вектор грузите тестером в качестве инициализации, а потом гоните свой скан тест.

Именно поэтому предложение покрыть все сканами было не очень хорошее.

Во вторых, простенькая прога - это время разработки, это закупка компилятора, это затраты на поддержку, это затыки проекта по неделе на каждом баге...

ЕТ всё это умеет сам.

В итоге - для установки начального произвольного состояния аналога у нас получилось использовать боундари цепочку между цифрой и аналогом.

Осталась проблема:

================

А почему-бы вместо мультиплексора с выхода-на-вход не использовать туже боундари цепочку и позволить ЕТ самому решать что в неё задвинуть?

А скан цепочку к тому-же JTAG подключить.

23 hours ago, Aleх said:К сожалению, один скан порт годится только для очень маленьких микросхем, и не дает высокго покрытия.

Фолт кавередж точно не зависит одна большая или много маленьких цепочек. Совсем не зависит.

Насчёт много цепочек в паралель наружу....

1) "скан цепочка" для ЕТ это SCAN_IN, SCAN_OUT, SCAN_CLK как минимум

2) При малопиновом корпусе (SOIC-8) особо цепочек не натыкаешь наружу, а внутри может быть и ARM

3) А вы точно знаете как в бекэнде делать "много" выводов Clock Tree для каждого SCAN_CLK? Так чтобы в тесте это было много деревьев а в рабочем режиме одно сплошное со всеми сбалансированными листьями.

4) А вы у аналогового дизайнера спросили сколько будет стоять много быстрых (время теста = деньги) цифровых буферов на падах, которые ещё и с другими аналоговыми функциями замешаны? В гигагерцовых процах это ваще проблема.

5) А как с подключенными наружу цепочками Delay-Test (тот который проверяет величину задержек между тригерами) делать?

Поэтому лучше один быстрый цифровой порт.

-

10 hours ago, Aleх said:

Я не понимаю, почему в тестовом режиме нельзя заизолировать входы аналога так же, как это делается в лоу паэр флоу? Просто пропускаете логические входы аналога через and или or....

Типичное решение...

Плохо тем, что аналоговые дизайнеры не могут сказать в каком положении должны быть все 600 аналоговых входов при ATPG, а в каком при IDDQ...

Из-за одного бита прийдётся полляма $ за метал редизайн отвалить....

-

Для чего изначально был придуман JTAG он уже меньше всего и нужен в микросхеме.

Если он уже есть, то городить любые воркераунды (типа RS232, внешних скан цепей с тестмод-пинами и тд.) смысла мало.

Используя JTAG можно сразу получить всю мощь тестовых программ разработанных за десятилетия.

Поэтому использовать JTAG для того чтобы через него гонять и ATPG и функциональные тесты очень даже хорошая мысль.

2 hours ago, Aleх said:что то вроде логического RS-232 интерфейса с возможностью тестировать аналог - перехватывать управление, считывать данные с ацп и т.д. (вы не написали, что подразумеваете под аналогом, могу только гадать). Тогда можно было бы на тестере и покрытие проверить, и прогнать функциональный тест аналога через rs232.

RS-232 плохая мысль .... Осцилятор откуда брать?

Если осцилятор на борту (в аналоговой части) то как его оттримировать через RS-232...Битрейт какой ставить если осцилятор имеет разброс +/-40%?

28 minutes ago, Aleх said:Был еще один вариант, про который я забыл за давностью лет. Суть сводилась к тому, что если скан цепочка одна, то ее можно подключить к тап контроллеру в виде инструкции пользователя, ....

Вы правильно подошли к пониманию части вопроса. Скан цепочку цифры подключили. Хоть десять скан цепочек на один вход\выход JTAG по очереди.

Но, цифра будет дёргать аналог во время теста и вирубит всё (хоть с мультиплексор на входах\выходах хоть без).

Аналог это типично такое: OSC, PLL, ADC/DAC, BandGap, POR.

Это как можно решить?

-

On 3/29/2019 at 6:12 AM, Aleх said:

Для проверки каких то специфичных вещей через джитаг, в нем предусмотрены инструкции пользователя в качестве дополнения к стандартным id/intest/extest/sample/preload...... Пишете свой BIST для проверки аналога....Ну и наверно можно эти вектора гонять на вафертестере вместе с обычным Atpg в целях отбраковки.

В основном для этого JTAG и нужен.

On 3/29/2019 at 6:12 AM, Aleх said:Что касаетается увеличения покрытия, то первое, как уже писал - прошить все сканом, включая джитаг.

Если прошить боундари цепочку сканом, то скан цепочка будет случайным образом дергать аналог - очевидно что єто не допустимо.

Как при этом задать "ATPG режим" аналога вокруг?

Как извне подключится к скан цепочке - падов то 8 всего?

Если прошить "всё" сканом (включая TAP), то тут проблема в потере управляемости чипом - JTAG прошит и не существует.

On 3/29/2019 at 6:12 AM, Aleх said:Второй вариант - прямо в RtL выходы ядра завести на его же входы через мультиплексор, управляемый TESTMODE.

Типичное решение...

Первая проблема та-же что и в первом варианте - дерганье аналога во время ATPG.

Вторая - тайминг пасы с 300 выходов на 150 входов через весь кристалл.... не разгонишь скан тест аднако.

Третья - чем устанавливать этот TESTMODE? Как с TESTMODE выходить и сколько это занимает времени?

On 3/29/2019 at 6:12 AM, Aleх said:Третий вариант - специально созданый для таких целей стандарт IEEE 1500 shadowrapper (сам никогда это не делал)

По сути IEEE 1500 это обёртки вокруг блоков цифры, чтобы можно было через JTAG манипулировать отдельным блоком (напр. шит флеш). С ATPG никак не связано а уш тем более с увеличением фолт кавереджа.

On 3/29/2019 at 6:12 AM, Aleх said:BIST

Built In Self Test - Самотестирование аналога невозможно по одной простой причине - внутри чипа нет измерителя напряжения классом 0.01%

Но похоже вы имели ввиду функциональный тест аналога через JTAG . Собственно для этого баундари цепочка и нужна вокруг цифры.

==================================

Напомню изначальный вопрос:

Кто ни будь использовал JTAG боундари скан при генерации ATPG чтобы стимулировать входы и читать выходы цифры вместе со встроенными в цифру скан цепями?

-

On 3/26/2019 at 8:39 PM, Aleх said:

надо прокрутить машину состояний тап-контроллера в режим INTEST, а потом ходить по состояниям, в которых переключаются режимы shift и update.

Именно так. дергать порти JTAG. Подключать скан цепочки к TDI, вдувать их внутрь , идти в CAPTURE и опять скан...

On 3/26/2019 at 8:39 PM, Aleх said:Получается, что длины векторов будут намного больше числа элементов в цепи

Не получается. Обычно длинна даже фрагментированной цепочки пару сотен флопов. А сколько тех состояний JTAG....

On 3/26/2019 at 8:39 PM, Aleх said:определенные фрагменты вектора (хождение по машине состояний житаг) придется писать вручную - слабо верится, что atpg генератор такое умеет.

Да EncounterTest имеет возможность настройки каждой фазы ATPG процесса. Напр. можно скан фазу можно описать как последовательность JTAG переходов в скан, вдувание бита с клок пульсом, ...., в конце опять последовательность JTAG переходов в начальное состояние.

Дальше тулза сама будет применять эту последовательность в каждом тест векторе.

Да немножко больше время... процента на 0.1% от общего время скана....

И-да, мож уже JTAG тулзи сразу понимают, т.е. вместо дерганья битами самому можно сказать - JTAG иди в скан. Никто не в курсе?

On 3/26/2019 at 8:39 PM, Aleх said:К тому же, одного сигнала tdi недостаточно, чтобы ходить по машине состояний; надо еще управлять и tms.

...и клоком, и ресетом... Не вижу в чём тут трудность?

On 3/26/2019 at 8:39 PM, Aleх said:Принимая все это во внимание, существуют куда более простые способы увеличить покрытие на интерфейсах, чем развлечения с баундари скан и житагом.

поделитесь пожалуйста

И на всяк случай уточню пару ограничений:

- Пинов кроме JTAG на корпусе чипа нет. SOIC-8

- Надо ещё и аналогом полностью управлять уметь и желательно через тот-же JTAG . Аналог тоже ведь тестировать надо...

-

Уточнение.

Все цифровые выходы должны быть предустановлены в определённое значение (чтоб аналог на борту не вырубил чип) и оно не должно меняться во время ATPG.

JTAG интерфейс предполагается использовать для скана в\из цепочек. Т.е JTAG должен работать как обычно.

Подключать цепочки на пины нельзя.

Так кто-то пробовал сделать и запихать в Encounter Test?

-

Кто ни будь использовал JTAG боундари скан при генерации ATPG чтобы стимулировать входы и читать выходы цифры?

-

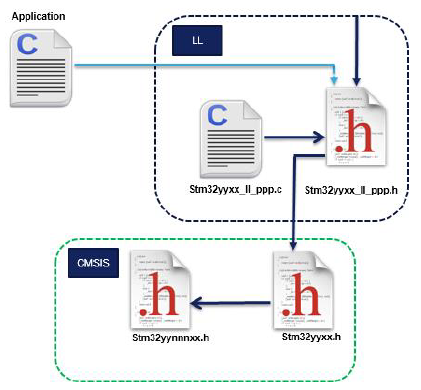

Спасибо за инфу. Как соотносится HAL\LL и CMSIS видно рисунке:

Для переносимости рекомендуют HAL, для тех кому нужны детали железа LL.

CMSIS в принципе и не надо.

Кроме того микс HAL и LL даже рекомендуется ST.

Похоже что мешать все API в один исходник вполне приемлемо....

==================================================

Остался вопрос не совсем по теме но всё-таки

Какой язык на сегодня наиболее популярен в ембедыд - C или C++?

HAL\LL и CMSIS єто чисто C. Хотя все соурсы включают external C для линковки с C++.

Про обертки C++ поверх RTOS читал.

А есть ли обертки или примеры как использовать C++ с HAL\LL драйверами?

-

17 hours ago, Aleх said:

Возможно, это зависит от вендора тула.

Cadence Encounter Test.С учетом того что в миксид сигнал чипах цифра внутри аналога и без падов, тулза просто обязана ставить боундари скан без падов...

А кстати зачем боудари скан вам понадобился?

Для теста самого чипа внутри он вроде как и не нужен....

-

1 hour ago, HardEgor said:

Микс используют, потому что полная изоляция уровней архитектуры по мере роста иерархии либо становится ограниченной и теряет возможности, либо становится слишком "дорогой" по памяти и/или по производительности.

Как я вижу в драйвере USB, HAL как раз и использован как наслоение над CMSIS с целью изоляции особенностей архитектуры.

А не наоборот добавлен CMSIS с целью ускорить работу. Это не понятно.

Ещё CMSIS использован как интерфейс к RTOS. Видимо чтобы от конкретной RTOS отвязать драйвер. Это понятно.

Выходит к RTOS и битам USB полезли через CMSIS, а к апликейшену через HAL....

В общем, запутал меня ST :(

Это что нормально лепить всё в кучу?

про мелкую блочную память из latch'ей

в Разработка цифровых, аналоговых, аналого-цифровых ИС

Опубликовано · Пожаловаться

Надо определится что мы называем латчем.

Если это асинхронный RS-тригер на 2-х перекрученных NAND (для памяти чёбы не использовать?), то будут лупы.

Если это латч в смысле тригер управляемый уровнем а не еджем - то STA по дефолту хавает. Ну можно тайм боровинг задать ещё.