HFSS

-

Постов

441 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные HFSS

-

-

Измерьте, кому несложно, на своих платах напряжение на выходе передатчика AD936X (на дифпаре).

Спасибо.

-

Тоже пробуем работать с с этой AD9361 + балун (TCM1-63AX+) +.... Имеем в наличии готовую плату с этим хозяйством от скажем "производителя"..

Тоже смотрел/изучал/считал какое диффернциальное сопротивление выбрать. В итоге сделал на плате 100 Ом. Сложно сказать сколько потеряно мощности (а может и нет) т.к. естестевенно топология у меня другая нежели у "производителя", есть различия в типах SPDT и их количестве (у меня их больше и потери мои немного больше имеют).

Работает. Но по поводу выбора сопротивления дифпары сомнения остались.

Раз уж коснулиcь сдесь и AD9361, то задам вопрос тут.

Наблюдаю величину напряжения (постоянка) на выходах предатчика (та самая диф пара 100 Ом, предатчик в режиме передачи), около 1,04 В, хотя подаю через индуктивность туда 1,3 В.

Измеряю то же самое на плате "производителя" , там практически ничего не падает на этих выходах, почти теже 1,3 В имеем.

Собственно не совсем понятно, должно так быть или не должно...

В документации вижу графики, которые гласят что после включения передатчика появляется некая просадка, но она мизерная и я действительно её фиксирую на плате "производителя"...

Такие вот дела.

За коментарии буду признателен.

-

HFSS, судя по описанию как раз все должно работать автоматом. В режимах 1000 и 10 прямо так и написано, а в 100 не имеет значения полярность.

Спасибо за разъяснения. Это очень хорошая новость. Приятно. :rolleyes:

-

Обычно в доках на PHY нужно искать подтверждения. Что-нибудь вроде такой записи:

"The line interface on the AQR107-AQR109 supports automatic A/B and C/D pair

swaps, polarity inversions, auto-X (MDI versus MDI-x operations), and semi-cross

(A/B or C/D only). It also supports provisionable ABCD to DCBA pair reversal for

ease of routing with stack-jacks via bit 1.E400.1:0. Note that this reversal does not

swap polarities (thus, A+ maps to D+, etc.)."

Ну и для уточнения посмотреть в карту регистров, поискать биты отвечающие за полярность линий и проверить их состояние по умолчанию и возможность их изменения.

В последнее время все PHY чипы с которыми доводилось сталкиваться инверсию физ. линий поддерживали. Мало того, такую инверсию еще и USB HUB-ы поддерживают.

Проблема была только в случае, когда программисты не хотели менять оригинальный софт производителя PHY, в котором нужно было менять эти настройки.

Спасибо за информацию.

У меня вот это написано в доке

"Polarity Correction

The RTL8211E-VB(VL)/RTL8211EG-VB automatically corrects polarity errors on the receive pairs in 1000Base-T and 10Base-T modes. In 100Base-TX mode polarity is irrelevant. In 1000Base-T mode, receive polarity errors are automatically corrected based on the sequence of idle symbols. Once the

descrambler is locked, the polarity is also locked on all pairs. The polarity becomes unlocked only when the receiver loses lock. "

Я правильно понимаю, что у меня полярность пар менять нельзя?

Спасибо.

-

Странный у Вас разъем какой-то, не видел подобного.

Вот и мне подобный (HR911196AE) пришлось ставить... тоже распиновка не понравилась.. через одно место она.

И насколько я помню, в GbE полярность пар значения не имеет, так что подводить можно как удобно.Uree, а немогли бы вы ткнуть носом в документ где это подтверждается?

-

Собственно, интересуют соображения по переходу с микрополоска ( stripline microstrip ),

через слот-щель в волновод с торца.

Когдато на основе этого Planar Microstrip-To-Waveguide Transition in Millimeter-Wave Band - Kazuyuki Seo моделировал и делали под свои нужды.

-

Не могу найти информацию о существовании (не существовании) ограничений на длину трас от пинов последней микросхемы памяти (DDR3 / Fly-by) до терминирующих резисторов. Кто знает или встречал поделитесь информацией.

Кому интересно, то нашёл информацию таки: в некоторых источниках указывается ограничения в 500 мил, а вот например Фуджицу пишут что ограничений нет.

-

Если его использовать в коаксиально-волноводном переходе, то как предполагалось центровать жилу в отверстии? Делать свою диэлектрическую втулку?

Или есть что-то более подходящее?

Мы именно в квп его использовали. Варианты были разные - и с второпластовой втулкой и с напайкой доплнительного металла (трубки) и просто так как есть.

В некоторых изделиях спользовали подстроечные винты , в некоторых не использовали для подстройки ничего (пеерход не суперузкополосный - нам хватало полосы).

А вы с какой целью то хотите штырь центровать?

-

Не могу найти информацию о существовании (не существовании) ограничений на длину трас от пинов последней микросхемы памяти (DDR3 / Fly-by) до терминирующих резисторов. Кто знает или встречал поделитесь информацией.

Еще не понятно допускается ли тянуть трассу до терминируещего резистора не от самого пина последней микрухи , а например через переходное отверстие на некотором расстоянии от последней памяти , т.е. перходку поставить прям на линию (сам думаю что не особо хорошо так делать, но инфы что то не нашёл).

-

Именно.

Они не терминируются ничем внешним

Спасибо.

-

Не проходите под требования :laughing: Придется ставить терминаторы.

а терминаторы уж если ставить, то я правильно понимаю что только на адресные линии и управление ?

а на линии шин данных, стробы нет необходимости (короткие они, менее 25мм).

-

Не проходите под требования :laughing: Придется ставить терминаторы.

Ближе к вечеру по МСК скину небольшую либу с этими и другими футпринтами: чисто шутки ради- сможете сравнить.

Почти прохожу. Немного короче линии надо сделать. :rolleyes:

А библиотеку ждёмс )

А расстояния и импедансы, друг мой, это все зависит от стека платы, так что вперёд определитесь с количеством слоев ВАШЕЙ платы, потом определитесь с тем, у кого будете ее делать и попросите у них стекап под плату, они же вам и импедансы дорог и зазоры посчитают.Если же, вам скажут, типа делайте как хотите, мы всё могём... то тогда polar 9000 вам в помощь, вводите параметры материала, типа эпсилона и тп, ширины/высоты/зазоры и пытаетесь получить 50 ом =)

у нас стекап на данных скринах с мегтроном, поэтому вам знания моих зазоров и линий не помогут от слова совсем.

Причём сдесь воновые сопротивления ? к чему вы всё это написали....

Ширину линий и растояние между линиями спросил лишь чтобы оценить насколько близко вы их не боитесь располагать, мой друг

это всё что мне интересно )

это всё что мне интересно ) -

yuri.job, спасибо за скрины.

А какова у вас ширина линий? Какогово расстояние между линиями? И растояние лияния -строб?

-

Не только- у вас заметные стабы на каждой микросхеме памяти.

стабы это что такое?

Получите очень заметный выигрыш если хотя бы раза в 2 сократите "необитаемые острова".Не повторяйте распространенную ошибку- распланируйте плату, причем так чтобы вам четко было видно что где встало и куда и идет, сделайте все фанауты, и потом беритесь за ддр3. Как минимум после указанных действий у вас будет "реальная" площадь доступная для разводки, а само выравнивание делайте когда чисто физически минимум все ближайшие сигналы проложены.

Спасобо за советы.

И все же- что за проц, шаг выводов и скорость памяти? Если чего-то опасаетесь можете в лс написать.шаг у проца 0.65, память 1600 LP.

Путаете модуль с микросхемой памяти :laughing:Да. спасибо. Но есть ещё (документ TN-46-14) вот что

(Some system designs can operate without requiring V TT . The approximate system

boundaries enabling V TT exclusion are:

• Two or fewer DDR components in the system

• Moderate current draw

• Trace length <2in (5cm)

• SI and drive strengths within data sheet limits (determined through simulation))

ПС. Больно странные футпринты банок возле памяти- уж не 0603 случаем?0402 там, но может корявые конечно, давно были сделаны, так и использую))

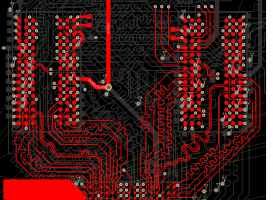

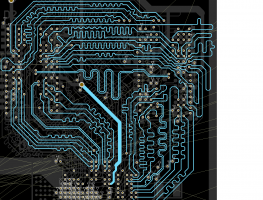

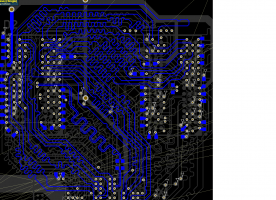

К вопросу ДДР3....А не могли бы вы выложить послойные скрины ?

ЗЫ, на мой взгляд, я бы свапанул местами блок питания и еммц (ну или нанд), чипы памяти сделал бы миллиметра 3 друг от друга и сдвинул бы их правее, тогда данные завелись бы примерно так же, а адреса от праца к левому чипу, а от него к правому почти без выравнивания. плис было бы место под источник питания, если его поставить вместо еммц. кстати а чего еммц старую ставите? всмысле наверно что то типа еммц4.х? или проц другую не держит?Спассибо за совет. Тоже об этом думал (сдвиг одной памяти вверх) - может и пеерделаю позже.

еммц - 5 используем.

У вас ддр3 раскидан на 4 слоях, стало быть под плейны выходит 2, из которых как минимум один будет кусками. Сильно сомневаюсь что нормально положите без опор хайспиды :laughing: Наиболее вероятно что вы не используете потенциал камня.Не сомневайтесь :rolleyes: . Потенциал камня планируем использовать почти весь.

-

- если ничего не путаю, есть байтлейны которые не удалось в одном слое положить

- вы делаете типовые ошибки в плане захвата места используя нарост меандров в 2 стороны, т.е. неиспользованные пустые острова вам же потом и мешают все поставить как надо

- сильно напрасно взялись за выравнивание и вообще за ддр3 когда на плате почти и нет ничего толком.

- да так и есть. Да клок прыгает из слоя в слой. Был вариант без этого прыгания, но там приходилось другие трассы тянуть в разных слоях и тесно очень под памятью было. В общем остановился на варианте который и видите.

-с меантром да согласен, но не уверен что большого выигрыша получу.

- ддр3 первый раз трассирую, поэтому в первую очередь взялся именно за неё. С замечанием конечно согласен.

Для флайбая глубоко ошибаетесь :laughing: Гуглите минимум по кейворду ddr3 flyby- количество документов запредельно. Туда же routing guidelines.Читал вот этот документ от микрона TN4108. Там написано следующее

The VTT supply is still required on the motherboard. However, the external parallel

termination resistors required for DDR2 are not required for DDR3 JEDEC-compliant

modules; the VTT terminating resistors are built onto the module.

т.е. терминация осуществлена внутри ддр3. Или нет? Запутался я чтото.

-

Насколько я могу понять наблюдается следующее:

флайбая(не вижу терминаторов+ зачем то скачете из слоя в слой ), ни т- бранча(точно не он)

Ну и есть немало вопросов по отдельным участкам, например

Ну и есть немало вопросов по отдельным участкам, напримерРеализован именно флайбай. О каких терминаторах идет речь? На сколько я знаю для DDR3 не нужны они. Или я глубоко ошибаюсь? Ткните тогда в документ.

-

....насколько я вижу корпуса, речь идет о двух 16 битных планках, но при взгляде на разводку я не могу сказать что вижу флайбай или Т-бранч. Мне кажется вижу какую-то дикость

Есть ли послойные скриншоты разводки ддр3? Какое-то непомерное место ушло на них, хотя должно вмещаться раза в 2 меньшую область.

Есть ли послойные скриншоты разводки ддр3? Какое-то непомерное место ушло на них, хотя должно вмещаться раза в 2 меньшую область.Ну и сомнительно браться за U4 не разобравшись с PMIC(?) в левом нижнем углу :laughing:

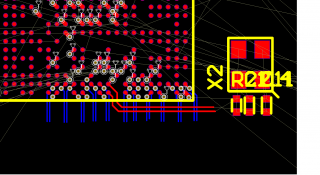

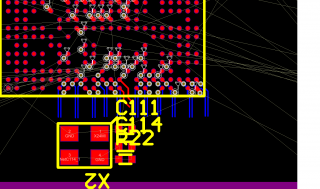

Скрины, да пожалуйста. Теперь что видите?

Выложите хоть кто-нибудь свою трассировку с парой DDR ....хоть флайбай, хоть Т-схему.

За U4 особо не брался. ещё с питанием и тд. надо разобраться... что как оказаолось не так тревиально как казалось мне на первый взгляд.

Слоёв всего 6ть.

-

Предельно это между микросхемами , а запредельно Это под микросхемами?

По такой логике внутри микросхем вообще жуть.

Внутри микросхем маделируется всё на сто раз, а тут надо чтобы работало с первого раза. А определить на сколько можно сближать линии на глазок предлагаете? Я уже нарушил стандартные правила по трассировке скоростных трасс, но не безсоновательно, а на основе своего опыта, Еще больше (плотнее украдывать) не могу себе позволить. Моделировать времени нет.

Все в цифрах, где кто указывает минимальные расстояния, и на какой длине они должны быть выполнены?.У вас все можно сделать короче и выполнивши все, что сейчас у вас сделано ( и да же лучше).

Сейчас придут другие и вас научат

Микросхемы стык в стык ставит и справляются.

А у вас площади столько, что формально еще одну микросхему памяти можно поставить.

У меня глубокие сомнения есть по поводу стык в стык и установки ещё одной памяти.

Покажите пример плотной трассировки (своей), чтоб стыт в стык и т.д.

Ну а другие конечно пусть приходят и пишут свои мысли и если могут рекомендации. Как всегда выслушать буду рад. Но только по делу.

-

Справа у вас линии DDR за пределы Plane -- Это явная ошибка, если Plane являются опорными для этих линий

Никаких PlanОВ ещё и в помине нет. О таких ошибках тет и речи быть не может. Сто лет назад всё изучено.

Я бы задумался в первую очередь, как сдвинуть D2 и D3. Это же однотипные микросхемы, ОЗУ, видимо?Ну и поднять все, естественно. Думаю, кварцевый резонатор будет работать, куда его ни поставь. Но зачем делать плохо?

Не помещается так - поверните всю расстановку и разводку на 90°.

Однотипные, DDR3. Но сдвинуть не могу (Разве что на ширину резистора) - потому как в тор слое (крассный), уже и так предельно (и запредельно ) близко трассы между собой проходят.

Фиолетовая линия это мето где будет снята маска и будет припаян экран. Куда ж там поднимать то...

На 90 и на 45 уже пройденный этап. Там возникают свои неудобства и сложности, Отказался от таких вариантов.

-

??? Но хозяин барин

Просто подвиньте все (D1, D2,D3) вверх. места много

Да и D1 к D2,D3 можно подвинуть

Об остальном умолчу.

D1 к D2,D3 подвинуть уже нельзя. Это далеко не первая попытка трассировки с целью сближения.

Вверх сдвигать тоже места нет как виидте. Не все слои просто были показаны.

Об остальном не молчите. Критике всегда рад.

Если она не касается гуляния дифпар со слоя на слой, слишком близкого расстояния между высокоскоростными трассами, расположения скоростных трасс на тор и bot слое критукуйте. Буду рад.

Ну и всё же по расположению кварца хотелось бы услышать мнение.

ь

-

И что мешает снизу?

Там куча дифпар на слое Bootom

Места для их разворота на нижнем слое нужно больше, чем для кварца

Дифпары на этом и заканчиваются. Планируются площадки или полуотверстия, в общем вниз не хотелось бы растить плату. А сбоку там место свободное в любом случае остаётся.

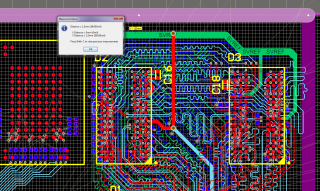

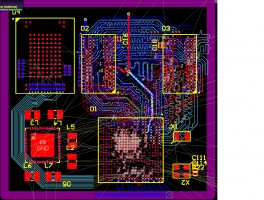

вот вся плата. чтоб вопросов не возникало

-

Хочется расположить кварц как показано на первой картинке (справа сбоку от СPU), конечно лучший вариант чем ближе тем лучше (вторая картинка), но важны габариты платы (вниз не хочется увеличивать её габориты).

Квару на 24 МГц, естественно всё вокруг залью землёй. Длинна проводников, если кварц располагать сбоку справа, около 10 мм.

Собственно хочу услышать мнения за и против.

-

Если вопросы теплоотвода и паразитных параметров такого перехода модуль-материнка остро не стоят и длины периметра хватает, то я рекомендую вариант с полу-отверстиями.

Вообще, переход к LGA выводам в корпусах модулей исторически был вынужденной мерой, безысходностью. Т.к. через залитые припоем полуотверстия ни вч сигнал не передашь, ни тепла много не сбросишь.

Сам я на стороне полуотверстий.

Так как полуотверстия или просто пины планируется располагать только по периметру модуля, то считаю что теплоотвод покрайней мере не хуже (а то и лучше) обеспечится именно через полуотверстия (диаметр самого отверстия минимальный 0,6 могут сделать, пину можно конечно намного уже).

Самое скоростное что нужно с модуля вывести это USB и RGMII . Считаю что полуотверстия не особо тут помеха.

Прав?

-

Собственно вышел спор о том что лучше использовать металлизированные отверстия или LGA (пины на боттоме ).

Панируется сделать некий небольшой модуль (платка - четыре BGA ) с которой необходимо вывести кучу сигналов плюс питание и земля.

Металлизированные полуотверстия или LGA (пины на боттоме ) планируется располагать по периметру платы в трёх сторон.

Шаг пусть будет 1,2.

Собственно вопрос в том кто что думает по данному поводу?

Patch-антенна на 2.4 Гига

в RF & Microwave Design

Опубликовано · Пожаловаться

Ну что ж зато полнейшую инфу предоставил)

Как это давно было то...