Art55555

-

Постов

282 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные Art55555

-

-

Добрый день!

Ищу человека для выполнения задач в ПЛИС Xilinx по детектированию, записи и последующему воспроизведению следующих форматов:

- видеосигналы формата PAL.

- видеосигналы формата AHD: AHD 0.8, AHD 1.0 и AHD 2.0.

- видеосигналы формата CVI.

- видеосигналы формата TVI.

Аппаратная платформа моя.

Предложения прошу писать в личку.

-

Не понятно как это исправить только, ведь сейчас выход задержанного клока подключён и к BUFR и к BUFG. Как быть - то тогда?

Это исправил. Но данные по-прежнему некрасивые(

-

Опубликовано · Изменено пользователем Art55555 · Пожаловаться

Да, именно про это.Не понятно как это исправить только, ведь сейчас выход задержанного клока подключён и к BUFR и к BUFG. Как быть - то тогда?

-

А мне интересно, вы результаты DRC в Вивадо смотрите? Все ваши варианты кода должны были вызывать предупреждения DRC, в последнем варианте тоже есть серьёзная ошибка.

Unsupported clocking topology used for ISERDESE2

<xISERDES111>. This can result in corrupted data. The CLK / CLKDIV pins

should be driven by the same source through the same buffer type or by a

BUFIO / BUFR combination in order to have a proper phase relationship. Please

refer to the Select I/O User Guide for supported clocking topologies of the

chosen INTERFACE_TYPE mode.

Вы про это?

-

Наблюдения следующие.

Если ставим BUFR divide=4, то работает корректно только в режиме 21-40

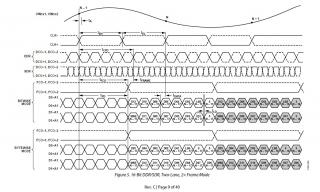

0x40 16-bit 1× DDR one-lane, wordwise 8 × fS Figure 7 (р.38 из datasheet на АЦП). Калибруется, выхожу на стабильные значения FF или АА.

если же в стандартном режиме 21-30 (0x30 16-bit 1× DDR two-lane, bytewise 4 × fS Figure 3 (default setting)) , то никаких 55 мы не видим. То 00, то 80, то каша.

Что-то явно с тактированием или пониманием тактирования.

Да, я сделал 2 счётчика. Один через PLL подал 100 на вход, получил 200 на выоде, счётчик по нему.

Второй по aclk_div.

Так вот, счётчик по aclk_div (при BUFR divide=4 идёт в 2 раза быстрее цлк-шного)...

В режиме 21-40 -одинаковая скорость.

-

Опубликовано · Изменено пользователем Art55555 · Пожаловаться

Что сделано.

1. Заменил тип на VAR_LOAD

2. Подал такт clk_200 с PLL, образованный из начальной 100 МГц путём умножения.

3. Занулил СЕ, INC.

Чего добились:

1. Наконец-то начал реагировать выход ISERDESE2.

Чего не добились:

"ЧИстых" 55 и АА, которые были раньше.

НАблюдения:

После старта платы перевожу в режим 21 регистр значение 30.

После этого видим "грязный" выход - 55. Теперь чистым он никогда не бывает. Дальше я играюсь сигналом CNTVALUEIN=> dco_delay (подаю с VIO) от 00 до 1F. От 55 мы потихоньку переходим к FF-F7 и уже к значению 1D получаем стабильный FF на выходе. Причём, если я прибаляю 1, т.е. на 1E - выход портится (FF-F7 вперемешку), прибавляю ещё 1 (1F) и опять вижу стабильный FF на выходе.

Т.е явного окна (плохо - умеренно- хорошо-умеренно-плохо) я ни вижу.

Также бывает, что при определённых значениях задержки вообще перестаёт работать Chipscope, который тактируется по aclk_div.

И ещё явный косяк с частотами, мне кажется. Сейчас проверяю зависимость между aclk_div и clk_200.

Текущий код ниже.

x_dco0 : IBUFDS

generic map (

DIFF_TERM => TRUE, -- Differential Termination

IBUF_LOW_PWR => FALSE, -- Low power (TRUE) vs. performance (FALSE) setting for referenced I/O standards

IOSTANDARD => "LVDS_25")

port map (

O => aclk, -- Clock buffer output

I => dco1p, -- Diff_p clock buffer input (connect directly to top-level port)

IB => dco1n -- Diff_n clock buffer input (connect directly to top-level port)

);

xIDELAY: IDELAYE2

generic map (

SIGNAL_PATTERN => "CLOCK",

REFCLK_FREQUENCY => 200.0,

HIGH_PERFORMANCE_MODE => "TRUE",

--FINEDELAY => "BYPASS",

DELAY_SRC => "IDATAIN",

CINVCTRL_SEL => "FALSE",

IDELAY_TYPE => "var_load",--"VARIABLE",

IDELAY_VALUE => 0,

PIPE_SEL => "FALSE"

)

port map (

DATAIN => '0',--,

IDATAIN => aclk,

DATAOUT => d_aclk,

C => clk_200, --200 MHz

CE => '0',

INC => '0',

LD => ld_dco_delay, --идет с VIO

CNTVALUEIN => dco_delay, --идет с VIO

CNTVALUEOUT => open,

REGRST => not AdcIdlyCtrlRdy,--'0',--

CINVCTRL => '0',

LDPIPEEN => '0'

);

bufio_adc: bufg port map ( i => d_aclk, o => aclk_main ); --FB

bufio_adc200: bufg port map ( i => clk_200i, o => clk_200 ); --FB

BUFR_ins1 : BUFR

generic map (

BUFR_DIVIDE => "4", -- Values: "BYPASS, 1, 2, 3, 4, 5, 6, 7, 8"

SIM_DEVICE => "7SERIES" -- Must be set to "7SERIES"

)

port map (

O => aclk_div, -- 1-bit output: Clock output port

CE => '1', -- 1-bit input: Active high, clock enable (Divided modes only)

CLR => '0', -- 1-bit input: Active high, asynchronous clear (Divided modes only)

I => d_aclk -- 1-bit input: Clock buffer input driven by an IBUFG, MMCM or local interconnect

);

x_IDELAYCTRL : IDELAYCTRL

port map (REFCLK => clk, RST => reset, RDY => AdcIdlyCtrlRdy);

xISERDES111: ISERDESE2

generic map (

SERDES_MODE => "MASTER",

INTERFACE_TYPE => "NETWORKING",

IOBDELAY => "Both",

DATA_RATE => "DDR",

DATA_WIDTH => 8,

DYN_CLKDIV_INV_EN => "FALSE",

DYN_CLK_INV_EN => "FALSE",

NUM_CE => 1,

OFB_USED => "FALSE",

INIT_Q1 => '0',

INIT_Q2 => '0',

INIT_Q3 => '0',

INIT_Q4 => '0',

SRVAL_Q1 => '0',

SRVAL_Q2 => '0',

SRVAL_Q3 => '0',

SRVAL_Q4 => '0'

)

port map (

-- Registered outputs

Q1 => dco_calib_out(0),

Q2 => dco_calib_out(1),

Q3 => dco_calib_out(2),

Q4 => dco_calib_out(3),

Q5 => dco_calib_out(4),

Q6 => dco_calib_out(5),

Q7 => dco_calib_out(6),

Q8 => dco_calib_out(7),

-- Unregistered output

O => open,--IntBitClk, --ser_dat(ii),

-- Carry out for bit expansion

SHIFTOUT1 => open,

SHIFTOUT2 => open,

-- Serial data in from PAD or IODELAY

D => aclk,--'0',

DDLY => '0', --d_aclk,--d_aclk,

-- Carry in for bit expansion

SHIFTIN1 => '0',

SHIFTIN2 => '0',

-- Clock signals

CLK => aclk_main,-- high-speed clock

CLKB => not aclk_main, -- inverted clock

CLKDIV => aclk_div,-- divided clock

-- Clock enable

CE1 => '1',

CE2 => '0',

-- Reset

RST => reset, --rst(i),

--- NOT USED

BITSLIP => '0', -- bitslip operation-------------------

OCLK => '0', -- high-speed clock

OCLKB => '0', -- inverted clock

DYNCLKSEL => '0',

DYNCLKDIVSEL => '0',

CLKDIVP => '0',

OFB => '0' -- feedback path

);

dco_calib_out_t<=dco_calib_out when rising_edge(aclk_div);

-

Ещё одно наблюдение.

Если вывести режим ацп с 2-кратной скоростью в 21 регистр подать значение 40 (100 = DDR one-lane, wordwise), то значение выходного ISERDES2 помучается FF. На сигналы LD и CNTVALUEIN по-прежнему реакции нет, а вот, если подать '1' на СЕ, то измение есть, только 1 такт, такое ощущение, что реально не задерживается ничего. Если подать на СЕ единицы на постоянную, то видим, что FF часто сменяются FE, но если единицу убрать, то опять всё возвращается на FF.

Ситуация на том же месте в итоге((

-

Вывести его на вывод и

Промерить частоту, допустим осциллографом. Потом пронаблюдать этот сигнал стабилен или нет.

Ладно это я посмотрю.

А настройки DDR/SDR 8 бит выход правильно заданы?

Ладно это я посмотрю.А настройки DDR/SDR 8 бит выход правильно заданы?

1. Мне не нравится вообще число АА. Ведь мы должны получать все 1 или все 0?

2. Сейчас мы делаем так. Принятый сигнал отправляем на IDELAYE2 для формирования. Из задержанного делаем aclk_main и aclk_div. А на вход D ISERDESE2 подаём "чистый" принятый сигнал aclk, после. Правильно ли это? Может, из "чистого" (несдвинутого) делать aclk_main и aclk_div, ими защёлкивать, а сдвинутый подавать на ISERDESE2 ?

-

Атрибут оставьте в этом состоянии.

Проверяем частоту aclk_div. Какая она? Реальная ...на вашем железе.

Атрибут оставил.

А как его проверишь - то? Я сделал по нему счётчик - бежит, всё в порядке.

-

Опубликовано · Изменено пользователем Art55555 · Пожаловаться

-

Не совсем.

BUFR делит на 4. Поскольку ISERDESE2 в данном случае принимает только 8 бит и в DDR режиме.

Если АЦП в DDR режиме также.

В итоге получается вот что.

Результат - всё тот же АА на выходе.. какое бы значение я бы не задавал.

Сигнал dco_calib_out_t должен отправляться на вход калибровочной машины. И там всегда АА.

x_dco0 : IBUFDS

generic map (

DIFF_TERM => TRUE, -- Differential Termination

IBUF_LOW_PWR => TRUE, -- Low power (TRUE) vs. performance (FALSE) setting for referenced I/O standards

IOSTANDARD => "LVDS_25")

port map (

O => aclk, -- Clock buffer output

I => dco1p, -- Diff_p clock buffer input (connect directly to top-level port)

IB => dco1n -- Diff_n clock buffer input (connect directly to top-level port)

);

xIDELAY: IDELAYE2

generic map (

SIGNAL_PATTERN => "CLOCK",

REFCLK_FREQUENCY => 200.0,

HIGH_PERFORMANCE_MODE => "TRUE",

--FINEDELAY => "BYPASS",

DELAY_SRC => "IDATAIN",

CINVCTRL_SEL => "FALSE",

IDELAY_TYPE => "VAR_LOAD",--"VARIABLE",

IDELAY_VALUE => 0,

PIPE_SEL => "FALSE"

)

port map (

DATAIN => '0',--,

IDATAIN => aclk,

DATAOUT => d_aclk,

C => aclk_div,

CE => set_idelay_dco,

INC => '1',

LD => ld_dco_delay,

CNTVALUEIN => dco_delay,

CNTVALUEOUT => open,

REGRST => not AdcIdlyCtrlRdy,

CINVCTRL => '0',

LDPIPEEN => '0'

);

bufio_adc: buf port map ( i => d_aclk, o => aclk_main ); --FB

BUFR_ins1 : BUFR

generic map (

BUFR_DIVIDE => "4", -- Values: "BYPASS, 1, 2, 3, 4, 5, 6, 7, 8"

SIM_DEVICE => "7SERIES" -- Must be set to "7SERIES"

)

port map (

O => aclk_div, -- 1-bit output: Clock output port

CE => '1', -- 1-bit input: Active high, clock enable (Divided modes only)

CLR => '0', -- 1-bit input: Active high, asynchronous clear (Divided modes only)

I => d_aclk -- 1-bit input: Clock buffer input driven by an IBUFG, MMCM or local interconnect

);

x_IDELAYCTRL : IDELAYCTRL

port map (REFCLK => clk, RST => reset, RDY => AdcIdlyCtrlRdy);

xISERDES111: ISERDESE2

generic map (

SERDES_MODE => "MASTER",

INTERFACE_TYPE => "NETWORKING",

IOBDELAY => "Both",

DATA_RATE => "DDR",

DATA_WIDTH => 8,

DYN_CLKDIV_INV_EN => "FALSE",

DYN_CLK_INV_EN => "FALSE",

NUM_CE => 1,

OFB_USED => "FALSE",

INIT_Q1 => '0',

INIT_Q2 => '0',

INIT_Q3 => '0',

INIT_Q4 => '0',

SRVAL_Q1 => '0',

SRVAL_Q2 => '0',

SRVAL_Q3 => '0',

SRVAL_Q4 => '0'

)

port map (

-- Registered outputs

Q1 => dco_calib_out(0),

Q2 => dco_calib_out(1),

Q3 => dco_calib_out(2),

Q4 => dco_calib_out(3),

Q5 => dco_calib_out(4),

Q6 => dco_calib_out(5),

Q7 => dco_calib_out(6),

Q8 => dco_calib_out(7),

-- Unregistered output

O => open,--IntBitClk, --ser_dat(ii),

-- Carry out for bit expansion

SHIFTOUT1 => open,

SHIFTOUT2 => open,

-- Serial data in from PAD or IODELAY

D => aclk,--'0',

DDLY => '0', --d_aclk,--d_aclk,

-- Carry in for bit expansion

SHIFTIN1 => '0',

SHIFTIN2 => '0',

-- Clock signals

CLK => aclk_main,-- high-speed clock

CLKB => not aclk_main, -- inverted clock

CLKDIV => aclk_div,-- divided clock

-- Clock enable

CE1 => '1',

CE2 => '0',

-- Reset

RST => reset, --rst(i),

--- NOT USED

BITSLIP => '0', -- bitslip operation-------------------

OCLK => '0', -- high-speed clock

OCLKB => '0', -- inverted clock

DYNCLKSEL => '0',

DYNCLKDIVSEL => '0',

CLKDIVP => '0',

OFB => '0' -- feedback path

);

dco_calib_out_t<=dco_calib_out;

-

Опубликовано · Изменено пользователем Art55555 · Пожаловаться

Подходит для INC/DEC режима. Если прямая загрузка кода задержки со входов, то режим VAR_LOAD.Далее С- это clk у вас 100 МГЦ, надо 200 Мгц поскольку нужен для управления IDELAYCTRL.

Поправил, ещё такой вопрос. Я првильнопонимаю, что BUFR должны делить на 8 в моём случае?

-

В ручном режиме нужно добиться, что у вас работает установка задержки IDELAYE2

путем ее проверки на выходе.

На входе С, Клок на этом примитиве CLK(???-что за сигнал )- должен aclk_div.

Все другие управлениющие сигналы (для idelaye2 iserdese2) производЯтся синхронно с этим сигналом.

Он становится основным клоковым сигналом.

Потом проверить наличие этого сигнала. Какова его частота.

Также нужно следить за установкой аттрибута IDELAY_TYPE (fixed, variable, var_load and etc) IDELAYE2.

С - это основной клоковый сигнал (100 МГц), в данной реализации просто стоит здесь. Заменил на aclk_div. В прошлых реализациях пробовал его. Работает также. Сейчас проверим. А по настройке IDELAY_TYPE variable подойдёт?

-

Учёл все рекомендации.

Результат такой же.

Сигнал dco_calib_out ВСЕГДА равен AA. Пробовал менять задержку через CNTVALUEIN - ничего не меняется. Если же пытаюсь подстраиваться через CE/INC, то на 1 такт АА превращается в BA. Не фиксируется. Код ниже.

x_dco0 : IBUFDS

generic map (

DIFF_TERM => TRUE, -- Differential Termination

IBUF_LOW_PWR => TRUE, -- Low power (TRUE) vs. performance (FALSE) setting for referenced I/O standards

IOSTANDARD => "LVDS_25")

port map (

O => aclk, -- Clock buffer output

I => dco1p, -- Diff_p clock buffer input (connect directly to top-level port)

IB => dco1n -- Diff_n clock buffer input (connect directly to top-level port)

);

xIDELAY: IDELAYE2

generic map (

SIGNAL_PATTERN => "CLOCK",

REFCLK_FREQUENCY => 200.0,

HIGH_PERFORMANCE_MODE => "TRUE",

--FINEDELAY => "BYPASS",

DELAY_SRC => "IDATAIN",

CINVCTRL_SEL => "FALSE",

IDELAY_TYPE => "VARIABLE",

IDELAY_VALUE => 0,

PIPE_SEL => "FALSE"

)

port map (

DATAIN => '0',--,

IDATAIN => aclk,

DATAOUT => d_aclk,

C => CLK,

CE => set_idelay_dco,

INC => '1',

LD => ld_dco_delay,

CNTVALUEIN => dco_delay,

CNTVALUEOUT => open,

REGRST => reset,

CINVCTRL => '0',

LDPIPEEN => '0'

);

bufio_adc: buf port map ( i => d_aclk, o => aclk_main ); --FB

BUFR_ins1 : BUFR

generic map (

BUFR_DIVIDE => "4", -- Values: "BYPASS, 1, 2, 3, 4, 5, 6, 7, 8"

SIM_DEVICE => "7SERIES" -- Must be set to "7SERIES"

)

port map (

O => aclk_div, -- 1-bit output: Clock output port

CE => '1', -- 1-bit input: Active high, clock enable (Divided modes only)

CLR => '0', -- 1-bit input: Active high, asynchronous clear (Divided modes only)

I => d_aclk -- 1-bit input: Clock buffer input driven by an IBUFG, MMCM or local interconnect

);

-- x_IDELAYCTRL : IDELAYCTRL

-- port map (REFCLK => clk, RST => reset, RDY => AdcIdlyCtrlRdy);

xISERDES111: ISERDESE2

generic map (

SERDES_MODE => "MASTER",

INTERFACE_TYPE => "NETWORKING",

IOBDELAY => "Both",

DATA_RATE => "DDR",

DATA_WIDTH => 8,

DYN_CLKDIV_INV_EN => "FALSE",

DYN_CLK_INV_EN => "FALSE",

NUM_CE => 1,

OFB_USED => "FALSE",

INIT_Q1 => '0',

INIT_Q2 => '0',

INIT_Q3 => '0',

INIT_Q4 => '0',

SRVAL_Q1 => '0',

SRVAL_Q2 => '0',

SRVAL_Q3 => '0',

SRVAL_Q4 => '0'

)

port map (

-- Registered outputs

Q1 => dco_calib_out(0),

Q2 => dco_calib_out(1),

Q3 => dco_calib_out(2),

Q4 => dco_calib_out(3),

Q5 => dco_calib_out(4),

Q6 => dco_calib_out(5),

Q7 => dco_calib_out(6),

Q8 => dco_calib_out(7),

-- Unregistered output

O => open,--IntBitClk, --ser_dat(ii),

-- Carry out for bit expansion

SHIFTOUT1 => open,

SHIFTOUT2 => open,

-- Serial data in from PAD or IODELAY

D => aclk,--'0',

DDLY => '0', --d_aclk,--d_aclk,

-- Carry in for bit expansion

SHIFTIN1 => '0',

SHIFTIN2 => '0',

-- Clock signals

CLK => aclk_main,-- high-speed clock

CLKB => not aclk_main, -- inverted clock

CLKDIV => aclk_div,-- divided clock

-- Clock enable

CE1 => '1',

CE2 => '0',

-- Reset

RST => reset, --rst(i),

--- NOT USED

BITSLIP => '0', -- bitslip operation-------------------

OCLK => '0', -- high-speed clock

OCLKB => '0', -- inverted clock

DYNCLKSEL => '0',

DYNCLKDIVSEL => '0',

CLKDIVP => '0',

OFB => '0' -- feedback path

);

dco_calib_out_t<=dco_calib_out;

-

Дизайн этот странный какой-то. Вы заводите на вход данных SERDES задержанный клок, и на вход клока SERDES тот же самый задержанный клок, естественно, изменение задержки не будет менять значения на выходах SERDES. И ещё непонятно, зачем пропускать клок через IBUFGDS(он же вроде BUFG вставляет) а потом ещё и через SERDES, а не прямо по цепочке IBUFDS -> IDELAY -> (BUFIO, BUFR параллельно)

Это скрин от XAPP524, выход SERDES идёт на клоковые буферы, а при выходе из компонента сразу заводится на вход.

По поводу IBUFGDS. Такт приходит с клоковых ног, и из P и N я делаю общий глобальный клок. Или я что-то не так понимаю? ))

В итоге, как подключать-то?

-

Примитив IDELAYCTRL в системе заведен?

Можно проверить работает ли IDELAYE2,

увеличили значение задержки посмотрели на выходах CNTVALUEOUT код задержки. Все коды должны быть стабильны.

В данной реализации НЕ заведён, но в ряде предыдущих был однозначно. Не могу сказать, что что-то изменилось после этого. Тем не менее, сегодня его вставлю, отпишусь.

По поводу CNTVALUEOUT-вчера заводит длятеста IN (результат такой же, как и с инкрементом задержки на 1/32), OUT же оставил открытым, сегодня проверю.

Спасибо!

-

Сделал 2 различных варианта работы.

Пробовал как в XAPP 524, так и и по XAPP585.

В обоих документах калибровка начинается с "выравнивания" такта.

Про данные позже.

Вход защёлкнут IBUFGDS. Далее так идёт на IDELAY2, выходит задержанный сигнал, идёт на вход DDLY ISERDES. Выход, который О, раздваивается на IOBUF (нужен в качестве быстрого такта для ISERDESов) и на BUFR (делит на 4) и используеся в качестве делённой частоты, также идёт на ISERDESы. Выход ISERDES анализируется.

Также отмечаю, что пробовал ещё несколько вариантов деления частоты, использования MMCM и др.

Подстройку провожу с помощью C и CE на IDELAYE2. Совершенно не нравится, что результат не меняется или меняется на 1 отчёт, а потом восстанавливаеся.

Поясню. В режиме защёлкивания такта DDR я всегда получаю значение 55. Если даю задержку (через VIO), то один такт получаю что-то типа 5E, а потом опять 55.

Если ставлю SDR, то итоговое значение FF, которое также не меняется - хоть на СЕ всегда подавай 1.

Один из вариантов кода привожу ниже.

x_dco0 : IBUFGDS

generic map (

DIFF_TERM => TRUE, -- Differential Termination

IBUF_LOW_PWR => TRUE, -- Low power (TRUE) vs. performance (FALSE) setting for referenced I/O standards

IOSTANDARD => "LVDS_25")

port map (

O => aclk, -- Clock buffer output

I => dco1p, -- Diff_p clock buffer input (connect directly to top-level port)

IB => dco1n -- Diff_n clock buffer input (connect directly to top-level port)

);

xIDELAY: IDELAYE2

generic map (

SIGNAL_PATTERN => "CLOCK",

REFCLK_FREQUENCY => 200.0,

HIGH_PERFORMANCE_MODE => "TRUE",

--FINEDELAY => "BYPASS",

DELAY_SRC => "IDATAIN",

CINVCTRL_SEL => "FALSE",

IDELAY_TYPE => "VARIABLE",

IDELAY_VALUE => 0,

PIPE_SEL => "FALSE"

)

port map (

DATAIN => '0',

IDATAIN => aclk,

DATAOUT => d_aclk,

C => aclk_div,

CE => set_idelay_dco,

INC => '1',

LD => '0',

CNTVALUEIN => "00000",

CNTVALUEOUT => open,-

REGRST => reset,

CINVCTRL => '0',

LDPIPEEN => '0'

);

BUFR_ins1 : BUFR

generic map (

BUFR_DIVIDE => "4", -- Values: "BYPASS, 1, 2, 3, 4, 5, 6, 7, 8"

SIM_DEVICE => "7SERIES" -- Must be set to "7SERIES"

)

port map (

O => aclk_div, -- 1-bit output: Clock output port

CE => '1', -- 1-bit input: Active high, clock enable (Divided modes only)

CLR => '0', -- 1-bit input: Active high, asynchronous clear (Divided modes only)

I => IntBitClk -- 1-bit input: Clock buffer input driven by an IBUFG, MMCM or local interconnect

);

xCLK_FB_inv: bufio port map ( i => IntBitClk, o => aclk_int ); --FB

aclk_int_n<=not aclk_int;

xISERDES111: ISERDESE2

generic map (

SERDES_MODE => "MASTER",

INTERFACE_TYPE => "NETWORKING",

IOBDELAY => "IBUF",

DATA_RATE => "DDR",

DATA_WIDTH => 8,

DYN_CLKDIV_INV_EN => "FALSE",

DYN_CLK_INV_EN => "FALSE",

NUM_CE => 1,

OFB_USED => "FALSE",

INIT_Q1 => '0',

INIT_Q2 => '0',

INIT_Q3 => '0',

INIT_Q4 => '0',

SRVAL_Q1 => '0',

SRVAL_Q2 => '0',

SRVAL_Q3 => '0',

SRVAL_Q4 => '0'

)

port map (

-- Registered outputs

Q1 => dco_calib_out(0),

Q2 => dco_calib_out(1),

Q3 => dco_calib_out(2),

Q4 => dco_calib_out(3),

Q5 => dco_calib_out(4),

Q6 => dco_calib_out(5),

Q7 => dco_calib_out(6),

Q8 => dco_calib_out(7),

-- Unregistered output

O => IntBitClk, --ser_dat(ii),

-- Carry out for bit expansion

SHIFTOUT1 => open,

SHIFTOUT2 => open,

-- Serial data in from PAD or IODELAY

D => '0',-- aclk,--'0',

DDLY => d_aclk,--d_aclk,

-- Carry in for bit expansion

SHIFTIN1 => '0',

SHIFTIN2 => '0',

-- Clock signals

CLK => aclk_int,-- high-speed clock

CLKB => aclk_int_n, -- inverted clock

CLKDIV => aclk_div,-- divided clock

-- Clock enable

CE1 => '1',

CE2 => '0',

-- Reset

RST => reset, --rst(i),

--- NOT USED

BITSLIP => '0', -- bitslip operation-------------------

OCLK => '0', -- high-speed clock

OCLKB => '0', -- inverted clock

DYNCLKSEL => '0',

DYNCLKDIVSEL => '0',

CLKDIVP => '0',

OFB => '0' -- feedback path

);

dco_calib_out_t<=dco_calib_out;

-

У меня за основу принят xapp585. В системе 4 отдельных корпуса АЦП другого типа. Все работает.

Начинал с харр524, Казалось будет проще. Но в итоге отказался и перешел на xapp585.

Не заметил один из вопросов. Как определяются границы бита?

Принимаются данные через сердес и запоминаются Далее меняется задержка.

Но при очередной следующей задержке, если сменимись данные (код данных), то это означает что попали на фронт смены бита.

Так определяются границы задержек стабильного приема данных и вычисляется середина этого участка,

которая и окончательно устанавливается. Все это описано в xapp'ах и даже лучше.

Отправил Вам в личку сообщение. Посмотрите, плз. Спасибо!

-

Я НЕ использую FRAME - калибруюсь по последовательности - это нормально? Для чего-то ведь этот сигнал существует)

-

А информация из http://www.analog.com/media/en/technical-d...otes/AN-877.pdf для AD9681 применима? Там описаны биты сброса псевдослучайной последовательнсти.

Сброс последовательности мне не требуется, старт я вижу сразу, генератор PN23 будет генерить и сравнивать значения.

-

Я, конечно же, брал за основу эти документы.

Бросается в глаза то, что я не использую FRAME для детектирование правильности данных.

Просто у меня калибровочная машина подключена к каждой Data-lane и я ожидаю с неё попеременно 2 разных числа, которые мне известны.

Далее, после каждого сердеса идёт фифо, выход которого уже идёт на выход.

Правильно ли это?

Ещё возник вопрос по поводу PN23.

Подумал, что не совсем корректно калиброваться по 2 выходным значениям. Решил попробовать с PN23.

По поводу изобретения велосипеда - на гитхабе этой АЦП нет, а те, что есть - непонятный принцип работы.

Что есть дата и как подавать стартовую последовательность для AD9681 0x7FFC?

Также не понятно, для чего эти входные данные нужны в режиме генератора, к тому же 23 бита в "рабочем векторе", а входные(выходные) данные только 16.

Какие генераторы я нашёл, а также самописный почему-то не дают последоватьельность 0x7F80, 0x8004, 0x7000, указанную в даташите.

Кто-нибудь встречался с данными проблемами?

-

не стоит городить велосипед - возьмите готовый ад-ый код.

В описании микросхемы на AD нет ничего для ПЛИС.

При таком алгоритме вы попадете не в центр окна данных (sample window),а в его край, где данные боле-менее стабильны. Вроде и не страшно, но всё-же обратите на это внимание.А схема тактирования какая ?

Согласен. Для проверки после проведения калибрации уже вручную играюсь значением задержки, лучше сигнал не становится. Причём видно, что искажение сигнала происходит на уровне конкретного бита (как в положительной, так и отрицательной области).

Теперь про такт.

От АЦП заходит быстрый DCO. Защёлкиваю его IBUFGDS. Получили сигнал ACLK. Далее из него делаю инверсный через конструкцию

aclk_inv<=not aclk;

Параллельно с помощью BUFR делением на 4 получаю aclk_div.

Все эти дела подаются на ISERDESE2.

Да, подстройку по IDELAYE2 делаю по такту другому - 100 МГц (хотя делал и по делённому aclk_div - разницы не увидел)

-

Есть Artix7 и AD9681.

Приём сделан по схеме DATA_PIN- IBUFDS-IDELAYE2-ISERDESE2.

К выходу ISERDESE2 я подключил калибратор.

Выбранный режим приёма - DDR two-lane, bytewise.

Далее привожу алгоритм.

1) По SPI выбираю режим передачи данных DDR two-lane, bytewise -0x21 значение 30.

2) По SPI выбираю режим передачи тестовой последовательности, состоящей из 2 слов. - 0x0D значение 04.

3) Используя перебор 32 значений IDELAYE2 и 8 bitslip-ов я добиваюсь того, чтобы на выходе ISERDESE2 появились искомые A8 54 на одном лэйне и AA 55 на другом. Автомат проверяет, чтобы стабильный результат на выходе был не менее 8192 раз. Если нет, то либо задержка, либо (если задержка достигает 32 - битслип). В итоге стабильно добиваюсь такого результата:

4) По SPI выбираю режим отключения тестовой последовательности, состоящей из 2 слов. - 0x0D значение 00.

И вижу такой результат при подаче с генератора синуса частоты 1 МГц:

Т.е. явно видно, что какой-то бит явно "врёт", хотя если опять вернуться на тестовую последовательность, то всё по-прежнему ок.

В чём может быть проблема?

-

Имеется связка ПЛИС Artix 7 и SPI флеш N25Q256.

Делаем всё так, как описано в XAPP 1081.

1) Создаём bit-файл.

2) В IMPACT создаём MCS файл. Настройки - MultiBoot для прошивки SPI флэшки.

3) Перловским скриптом создаём Initial и Update MCS файлы, т.е. Golden и Update Bitstream.

4) Прошиваем флешку из IMPACT - успешно. Флешка грузит плисину после включения.

Следующая задача прошить Update - область флешки средствами ПЛИС. Для этого получаем с компа файл прошивки (Update.mcs) и пытаемся его зашить в SPI-флешку с помощью модулей, приложенных к XAPP 1081 (SpiFlashProgrammer.vhd+SpiSerDes.vhd).

Вопросы:

1) При работе перл - скрипта, то он выдаёт: Update_Start_address=x"00200000" и Update_End_address=x"00400000" , что не сходится с реальными размером MCS файла (5,5 Мб) . Реально в это адресное пространство занимает около 2 Мб.

2) MCS файл в ASCII формате. В каком виде его отправлять? Нужно ли что-то модифицировать в нём?

2) Надо ли вообще делать для этого MCS или нужно отправлять BIT или BIN?

3) Где и как просчитвать адреса для областей Golden и Update Areas?

4) Что делать с CRC? Нужно ли его считать самостоятельно или куда-нибудь вписывать?

Есть ли какие-нибудь примеры, где описаны подобные манипуляции?

Требуется сделать прошивку для ADAU 1701 (или аналога).

в Предлагаю работу

Опубликовано · Пожаловаться

Требуется сделать прошивку для ADAU 1701 (или аналога). Задача – цифровой эквалайзер. 1-октавная фильтрация сигнала. Уровень подавления по каждой октаве – не менее 20 дБ. Шаг подавления по каждой из октав – 1 дб.

Требования к прошивке:

1) Получить оцифрованный сигнал. Частота оцифровки 44 кГц.

2) Получить по мосту USB-UART с компа величину подавления по каждой из октав.

3) Применить 12 1-октавных фильтров.

4) Суммировать выходы всех фильтров.

5) Подать полученный сигнал на ЦАП.

6) Автоматическая загрузка прошивки из ПЗУ.

7) Память крайнего установленного режима работы.