Art55555

Участник*-

Постов

282 -

Зарегистрирован

-

Посещение

Весь контент Art55555

-

Конечно, умеет. Просто у меня их три.

-

Имеется один источник такта на плате. Необходимо из него получать 3 разные тактовые частоты, не имеющие единой "кратности", но формироваться они должны все именно от одной частоты, которая заходит на плату. Далее необходимо будет коммутировать их на каждое из 3-х ацп. Кто-нибудь встречался с подобной задачей?

-

Прием данных с AD9697

Art55555 ответил Art55555 тема в Цифровые схемы, высокоскоростные ЦС

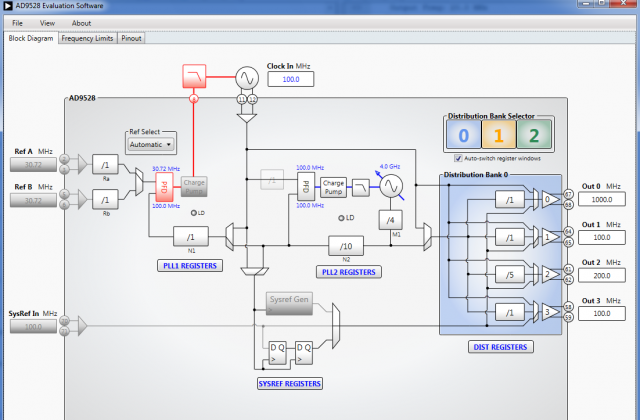

Получилось поставить линк, но теперь что-то данные плохие идут. I have AD9697, Kintex 7 and AD9528 for clocking. AD9528 works with SI570 (100 MHz base). AD9528 gives me clocks: 1000 Mhz - for AD9697 250 Mhz - Ref CLK (for Kintex) 31.25 Mhz - SysRef (for AD9697 and Kintex). I setup AD9697: N'=16, N=14, L=4, M=1, F=1, CS=0, K=32. What I do: 0571 15 058B 03 058C 00 058D 1F 058E 10 058F 0D 0590 0F 0571 14 SYNC OK (always '1')) Next: 0551 01, 0552 02, 0553 03, 0554 04, 0555 05, 0556 06, 0557 07, 0558 08 - Test pattrern refisters/ Tests: 1) 0574 01 - Result: b5b5b5b5----b5 (127 bit) 2) 0574 04, 0574 054, 0574 06 - Link down. 3) 0573 0E Result: 0705030108060402 0705030108060402 4) 0573 01 Result: aa55aa55aa55aa55aa55aa55aa55aa55 5) 0573 02 Result: ff00ff00ff00ff00ff00ff00ff00ff00ff00ff00ff00 6)0573 11 Result: b54ab54ab54ab54ab54ab54ab54ab54a 7) 057321 Result: aa55aa55aa55aa55aa55aa55aa55aa55 If 0571 14 - data wrong. Ramp test - fail/ -

Прием данных с AD9697

Art55555 ответил Art55555 тема в Цифровые схемы, высокоскоростные ЦС

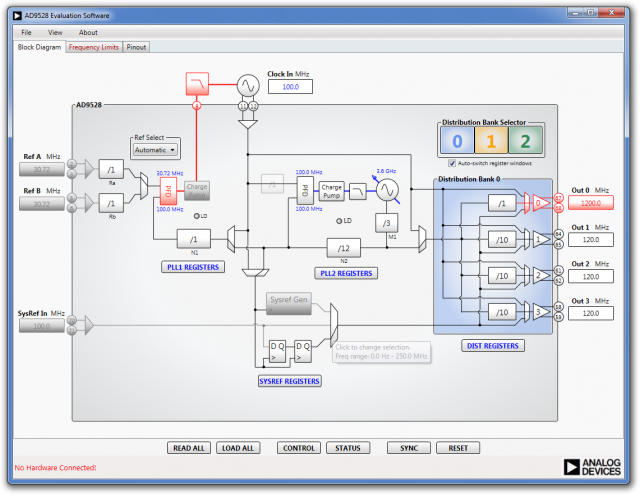

Выкладываю команды. I have AD9697, Kintex 7 and AD9528 for clocking. AD9528 works with SI570 (100 MHz base). AD9528 gives me 2 clocks 1200 MHz (OUT0 and OUT 13) for ADC and FPGA. Alsow AD9528 gives m2 2 clocks 120 MHz (OUT2 and OUT 3) for ADC and FPGA for SYS_REF. Additional clk 120 MHz foe FPGA OUT1. This seems well -counters OK. All screenshots here (AD9528 parameters): https://yadi.sk/d/yStQBZxBSRFnRQ Next stage I setup AD9697: I want to setup theese parameters JESD: N'=16, N=14, L=4, M=1, F=1, CS=0, K=32. What I do: 1) PWDN hard reset '1' 2) PWDN hard reset '0'. 3) Power down via SPI ( 0002 03) (address and command) 4) Power up via SPI ( 0002 00) (address and command) 5) Soft reset 0000 81 6) JESD lind down 0571 01 7) NEXT 1228 4F 1228 0F 1222 00 1222 04 1222 00 1262 08 1262 00 8) Setup Link Parameters: 058B 03 058C 00 058D 1F 058E 10 058F 0D 0590 0F 9) JESD lind up 0571 00. SYNC low(( Скрины https://yadi.sk/d/yStQBZxBSRFnRQ -

Проблема с AD9528

Art55555 ответил Art55555 тема в Цифровые схемы, высокоскоростные ЦС

Как я уже писал ранее, всё работает. Необходимо создать такт на выходе 1200 МГц на OUT 0 и на OUT 13. Судя по описанию, такую частоту эти выходы полностью поддерживаются. А вот софт от Аналога подсвечивает красным по поводу 0-го выхода, типа out of range, с 13-м всё ок. Физически не могу проверить - есть ли там частота или нет. Встречался кто с такой проблемой? -

Прием данных с AD9697

Art55555 ответил Art55555 тема в Цифровые схемы, высокоскоростные ЦС

Смотрите, что в итоге получается. Принял за основу следующие данные: N'=16, N=14, L=4, M=1, F=1, CS=0, K=32. Вопросы: 1) Я так и не нашёл где в Xilinx Core JESD PHY и JESD настраиваются N', N, M, CS? Регистрами они на АЦП настраиваются, а вот их ПЛИСная "вторая половина" отсутствует. 2) Последовательность у меня получается следующая (выложу по регистрово сегодня) сброс, powerdown link JESD, настройка (N'=16, N=14, L=4, M=1, F=1, CS=0, K=32.), powerup link JESD. Всё правильно? 3) Критерием того, что как минимум есть коннект, есть сигнал SYNC_N. Я правильно понимаю, что это выходной сигнал из порта rx_sync компонента JESD? На данный момент я его отправляю на OBUFDS, после чего, на АЦП? Так? -

Прием данных с AD9697

Art55555 ответил Art55555 тема в Цифровые схемы, высокоскоростные ЦС

Получается, мои действия следующие: 1) По даташиту 9697 выбираю требуемый режим передачи данных с АЦП. это парамерты (L,M,S K и т.д.) 2) Ввожу эти параметры в 2 ядра (JESD PHY и просто JESD), генерю ядра, делаю битник. 3) С помощью SPI настраиваю 9697 на эти параметры. Теперь вопросы? 1) Где этот SYNC_N смотреть? 2) Где смотреть символ "К"? -

Прием данных с AD9697

Art55555 ответил Art55555 тема в Цифровые схемы, высокоскоростные ЦС

Как это можно мне использовать? -

АЦП AD9697 +Xilinx

Art55555 ответил Art55555 тема в Цифровые схемы, высокоскоростные ЦС

Так и делаем уже много лет)) -

Прием данных с AD9697

Art55555 опубликовал тема в Цифровые схемы, высокоскоростные ЦС

Есть Kintex 7 и AD9697. Для такта использую AD9528 ( в связке с SI570). Со стандартом JESD204B никогда не работал, разбираюсь. Есть знающие? На данный момент на выходе вижу нули. Файл прилагаю как в теле, так и в прикреплённых. ad9697.vhd ---------------------------------------------------------------------------------- -- Company: -- Engineer: -- -- Create Date: 19.09.2019 11:47:46 -- Design Name: -- Module Name: ad9697 - Behavioral -- Project Name: -- Target Devices: -- Tool Versions: -- Description: -- -- Dependencies: -- -- Revision: -- Revision 0.01 - File Created -- Additional Comments: -- ---------------------------------------------------------------------------------- library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; library UNISIM; use UNISIM.VComponents.all; -- Uncomment the following library declaration if using -- arithmetic functions with Signed or Unsigned values --use IEEE.NUMERIC_STD.ALL; -- Uncomment the following library declaration if instantiating -- any Xilinx leaf cells in this code. --library UNISIM; --use UNISIM.VComponents.all; entity ad9697 is Port ( clk : in STD_LOGIC; reset : in STD_LOGIC; ADC0_p : in STD_LOGIC; ADC0_n : in STD_LOGIC; ADC1_p : in STD_LOGIC; ADC1_n : in STD_LOGIC; ADC2_p : in STD_LOGIC; ADC2_n : in STD_LOGIC; ADC3_p : in STD_LOGIC; ADC3_n : in STD_LOGIC; MGT_clk_p : in STD_LOGIC; --clk_out1 MGT_clk_n : in STD_LOGIC; SYNCINB_p : out STD_LOGIC; SYNCINB_n : out STD_LOGIC; SYS_REF_CLOCK_p : in STD_LOGIC; SYS_REF_CLOCK_n : in STD_LOGIC; SYS_REF_CLOCK_OUT: out STD_LOGIC; PDWN : out STD_LOGIC; test_out0 : out std_logic_vector (15 downto 0); test_out1 : out std_logic_vector (15 downto 0); test_out2 : out std_logic_vector (15 downto 0); test_out3 : out std_logic_vector (15 downto 0); test_out4 : out std_logic_vector (15 downto 0) ); end ad9697; architecture Behavioral of ad9697 is signal ADC_p : std_logic_vector (3 downto 0); signal ADC_n : std_logic_vector (3 downto 0); signal rx_reset : STD_LOGIC; component jesd204_phy_0 is PORT( -- System Reset Inputs for each direction tx_sys_reset : in STD_LOGIC; rx_sys_reset : in STD_LOGIC; -- Reset Inputs for each direction tx_reset_gt : in STD_LOGIC; rx_reset_gt : in STD_LOGIC; -- Reset Done for each direction tx_reset_done : out STD_LOGIC; rx_reset_done : out STD_LOGIC; -- GT Common 0 I/O qpll_refclk : in STD_LOGIC; common0_qpll_lock_out : out STD_LOGIC; common0_qpll_refclk_out : out STD_LOGIC; common0_qpll_clk_out : out STD_LOGIC; rxencommaalign : in STD_LOGIC; tx_core_clk : in STD_LOGIC; txoutclk : out STD_LOGIC; rx_core_clk : in STD_LOGIC; rxoutclk : out STD_LOGIC; drpclk : in STD_LOGIC; -- PRBS mode gt_prbssel : in std_logic_vector(2 downto 0); -- Tx Ports -- Lane 0 gt0_txcharisk : in std_logic_vector(3 downto 0); gt0_txdata : in std_logic_vector(31 downto 0); -- Lane 1 gt1_txcharisk : in std_logic_vector(3 downto 0); gt1_txdata : in std_logic_vector(31 downto 0); -- Lane 2 gt2_txcharisk : in std_logic_vector(3 downto 0); gt2_txdata : in std_logic_vector(31 downto 0); -- Lane 3 gt3_txcharisk : in std_logic_vector(3 downto 0); gt3_txdata : in std_logic_vector(31 downto 0); -- Rx Ports -- Lane 0 gt0_rxcharisk : out std_logic_vector(3 downto 0); gt0_rxdisperr : out std_logic_vector(3 downto 0); gt0_rxnotintable : out std_logic_vector(3 downto 0); gt0_rxdata : out std_logic_vector(31 downto 0); -- Lane 1 gt1_rxcharisk : out std_logic_vector(3 downto 0); gt1_rxdisperr : out std_logic_vector(3 downto 0); gt1_rxnotintable : out std_logic_vector(3 downto 0); gt1_rxdata : out std_logic_vector(31 downto 0); -- Lane 2 gt2_rxcharisk : out std_logic_vector(3 downto 0); gt2_rxdisperr : out std_logic_vector(3 downto 0); gt2_rxnotintable : out std_logic_vector(3 downto 0); gt2_rxdata : out std_logic_vector(31 downto 0); -- Lane 3 gt3_rxcharisk : out std_logic_vector(3 downto 0); gt3_rxdisperr : out std_logic_vector(3 downto 0); gt3_rxnotintable : out std_logic_vector(3 downto 0); gt3_rxdata : out std_logic_vector(31 downto 0); -- Serial ports rxn_in : in std_logic_vector(3 downto 0); rxp_in : in std_logic_vector(3 downto 0); txn_out : out std_logic_vector(3 downto 0); txp_out : out std_logic_vector(3 downto 0) ); end component; component jesd204_0 is port ( rx_core_clk : in STD_LOGIC; rx_reset_done : in STD_LOGIC; rx_reset : in STD_LOGIC; rx_sysref : in STD_LOGIC; gt0_rxcharisk : in std_logic_vector(3 downto 0); gt0_rxdata : in std_logic_vector(31 downto 0); gt0_rxdisperr :in std_logic_vector(3 downto 0); gt0_rxnotintable :in std_logic_vector(3 downto 0); gt1_rxcharisk : in std_logic_vector(3 downto 0); gt1_rxdata : in std_logic_vector(31 downto 0); gt1_rxdisperr :in std_logic_vector(3 downto 0); gt1_rxnotintable :in std_logic_vector(3 downto 0); gt2_rxcharisk : in std_logic_vector(3 downto 0); gt2_rxdata : in std_logic_vector(31 downto 0); gt2_rxdisperr :in std_logic_vector(3 downto 0); gt2_rxnotintable :in std_logic_vector(3 downto 0); gt3_rxcharisk : in std_logic_vector(3 downto 0); gt3_rxdata : in std_logic_vector(31 downto 0); gt3_rxdisperr :in std_logic_vector(3 downto 0); gt3_rxnotintable :in std_logic_vector(3 downto 0); rx_aresetn : in STD_LOGIC; rx_reset_gt : out STD_LOGIC; rxencommaalign_out: out STD_LOGIC; rx_tvalid : out STD_LOGIC; rx_tdata : out std_logic_vector(127 downto 0); rx_start_of_frame : out std_logic_vector(3 downto 0); rx_end_of_frame : out std_logic_vector(3 downto 0); rx_start_of_multiframe: out std_logic_vector(3 downto 0); rx_end_of_multiframe: out std_logic_vector(3 downto 0); rx_frame_error: out std_logic_vector(15 downto 0); rx_sync: out STD_LOGIC; s_axi_aclk : in STD_LOGIC; s_axi_aresetn : in STD_LOGIC; s_axi_awaddr : in std_logic_vector(11 downto 0); s_axi_awvalid : in STD_LOGIC; s_axi_awready : out STD_LOGIC; s_axi_wdata : in std_logic_vector(31 downto 0); s_axi_wstrb : in std_logic_vector(3 downto 0); s_axi_wvalid : in STD_LOGIC; s_axi_wready : out STD_LOGIC; s_axi_bresp : out std_logic_vector(1 downto 0); s_axi_bvalid : out STD_LOGIC; s_axi_bready : in STD_LOGIC; s_axi_araddr : in std_logic_vector(11 downto 0); s_axi_arvalid : in STD_LOGIC; s_axi_arready : out STD_LOGIC; s_axi_rdata : out std_logic_vector(31 downto 0); s_axi_rresp : out std_logic_vector(1 downto 0); s_axi_rvalid : out STD_LOGIC; s_axi_rready : in STD_LOGIC ); end component; component ila_0 IS PORT ( clk : IN STD_LOGIC; probe0 : IN STD_LOGIC_VECTOR(15 DOWNTO 0); probe1 : IN STD_LOGIC_VECTOR(15 DOWNTO 0); probe2 : IN STD_LOGIC_VECTOR(15 DOWNTO 0); probe3 : IN STD_LOGIC_VECTOR(15 DOWNTO 0); probe4 : IN STD_LOGIC_VECTOR(15 DOWNTO 0) ); END component; --signal reset : std_logic := '0'; signal clk_mgt: std_logic := '0'; signal SYS_REF_CLOCK: std_logic := '0'; -- System Reset Inputs for each direction signal tx_sys_reset : STD_LOGIC; signal rx_sys_reset : STD_LOGIC; -- Reset Inputs for each direction signal tx_reset_gt : STD_LOGIC; signal rx_reset_gt : STD_LOGIC; -- Reset Done for each direction signal tx_reset_done : STD_LOGIC; signal rx_reset_done : STD_LOGIC; -- GT Common 0 I/O signal qpll_refclk : STD_LOGIC; signal common0_qpll_lock_out : STD_LOGIC; signal common0_qpll_refclk_out : STD_LOGIC; signal common0_qpll_clk_out : STD_LOGIC; signal rxencommaalign : STD_LOGIC; signal tx_core_clk : STD_LOGIC; signal txoutclk : STD_LOGIC; signal rx_core_clk : STD_LOGIC; signal rxoutclk : STD_LOGIC; signal drpclk : STD_LOGIC; -- PRBS mode signal gt_prbssel : std_logic_vector(2 downto 0); -- Tx Ports -- Lane 0 signal gt0_txcharisk : std_logic_vector(3 downto 0); signal gt0_txdata : std_logic_vector(31 downto 0); -- Lane 1 signal gt1_txcharisk : std_logic_vector(3 downto 0); signal gt1_txdata : std_logic_vector(31 downto 0); -- Lane 2 signal gt2_txcharisk : std_logic_vector(3 downto 0); signal gt2_txdata : std_logic_vector(31 downto 0); -- Lane 3 signal gt3_txcharisk : std_logic_vector(3 downto 0); signal gt3_txdata : std_logic_vector(31 downto 0); -- Rx Ports -- Lane 0 signal gt0_rxcharisk : std_logic_vector(3 downto 0); signal gt0_rxdisperr : std_logic_vector(3 downto 0); signal gt0_rxnotintable : std_logic_vector(3 downto 0); signal gt0_rxdata : std_logic_vector(31 downto 0); -- Lane 1 signal gt1_rxcharisk : std_logic_vector(3 downto 0); signal gt1_rxdisperr : std_logic_vector(3 downto 0); signal gt1_rxnotintable : std_logic_vector(3 downto 0); signal gt1_rxdata : std_logic_vector(31 downto 0); -- Lane 2 signal gt2_rxcharisk : std_logic_vector(3 downto 0); signal gt2_rxdisperr : std_logic_vector(3 downto 0); signal gt2_rxnotintable : std_logic_vector(3 downto 0); signal gt2_rxdata : std_logic_vector(31 downto 0); -- Lane 3 signal gt3_rxcharisk : std_logic_vector(3 downto 0); signal gt3_rxdisperr : std_logic_vector(3 downto 0); signal gt3_rxnotintable : std_logic_vector(3 downto 0); signal gt3_rxdata : std_logic_vector(31 downto 0); -- Serial ports signal rxn_in : std_logic_vector(3 downto 0); signal rxp_in : std_logic_vector(3 downto 0); signal txn_out : std_logic_vector(3 downto 0); signal txp_out : std_logic_vector(3 downto 0); --------------------------------------------------- ----------------------------------------------------- signal refclk0p : STD_LOGIC; signal refclk0n : STD_LOGIC; signal glblclkp : STD_LOGIC; signal glblclkn : STD_LOGIC; signal tx_reset : STD_LOGIC; signal tx_start_of_frame : std_logic_vector(3 downto 0); signal tx_start_of_multiframe: std_logic_vector(3 downto 0); signal txp : std_logic_vector(3 downto 0); signal txn : std_logic_vector(3 downto 0); signal s_axi_aclk : STD_LOGIC; signal s_axi_aresetn : STD_LOGIC; signal s_axi_awaddr : std_logic_vector(11 downto 0); signal s_axi_awvalid : STD_LOGIC; signal s_axi_awready : STD_LOGIC; signal s_axi_wdata : std_logic_vector(31 downto 0); signal s_axi_wstrb : std_logic_vector(3 downto 0); signal s_axi_wvalid : STD_LOGIC; signal s_axi_wready : STD_LOGIC; signal s_axi_bresp : std_logic_vector(1 downto 0); signal s_axi_bvalid : STD_LOGIC; signal s_axi_bready : STD_LOGIC; signal s_axi_araddr : std_logic_vector(11 downto 0); signal s_axi_arvalid : STD_LOGIC; signal s_axi_arready : STD_LOGIC; signal s_axi_rdata : std_logic_vector(31 downto 0); signal s_axi_rresp : std_logic_vector(1 downto 0); signal s_axi_rvalid : STD_LOGIC; signal s_axi_rready : STD_LOGIC; signal tx_aresetn : STD_LOGIC; signal tx_sysref : STD_LOGIC; signal tx_sync : STD_LOGIC; signal rx_aresetn : STD_LOGIC; --signal rx_reset_gt : STD_LOGIC; signal rxencommaalign_out: STD_LOGIC; signal rx_tvalid : STD_LOGIC; signal rx_tdata : std_logic_vector(127 downto 0); signal rx_start_of_frame : std_logic_vector(3 downto 0); signal rx_end_of_frame : std_logic_vector(3 downto 0); signal rx_start_of_multiframe: std_logic_vector(3 downto 0); signal rx_end_of_multiframe: std_logic_vector(3 downto 0); signal rx_frame_error: std_logic_vector(15 downto 0); signal rx_sync: STD_LOGIC; signal rx_sysref: STD_LOGIC; signal CLKFBIN,CLKFBOUT: STD_LOGIC; signal SYS_REF_CLOCK_1: STD_LOGIC; signal rx_core_4x,rx_core_4x_g: STD_LOGIC; signal rx_core_2x,rx_core_2x_g: STD_LOGIC; signal rx_core_i,rx_core: STD_LOGIC; signal trig0: std_logic_vector(15 downto 0); signal trig1: std_logic_vector(15 downto 0); signal trig2: std_logic_vector(15 downto 0); signal trig3: std_logic_vector(15 downto 0); signal trig4: std_logic_vector(15 downto 0); signal clk_mgt_g: STD_LOGIC; signal cnt_sys_ref: std_logic_vector(15 downto 0); begin SYS_REF_CLOCK_OUT<=rx_core_4x_g; process (SYS_REF_CLOCK_1) begin if(SYS_REF_CLOCK_1'event and SYS_REF_CLOCK_1='1')then cnt_sys_ref<=cnt_sys_ref+1; -- if cnt1=500 then ;end if; end if; end process; IBUFGDS_inst1 : IBUFDS_GTE2 -- generic map ( -- DIFF_TERM => TRUE, -- Differential Termination -- IBUF_LOW_PWR => TRUE) -- Low power (TRUE) vs. performance (FALSE) setting for referenced I/O standards -- IOSTANDARD => "LVDS_25") port map ( CEB =>'0', O => clk_mgt, -- Clock buffer : out I => MGT_clk_p, -- Diff_p clock buffer : in (connect directly to top-level port) IB => MGT_clk_n -- Diff_n clock buffer : in (connect directly to top-level port) ); BUFG5 : BUFG port map ( O => clk_mgt_g, -- 1-bit output: Output feedback clock (connect to feedback input of DCM/PLL) I => clk_mgt -- 1-bit input: Feedback clock input (connect to input port) ); --IBUFGDS_inst2: IBUFDS_GTE2 ---- generic map ( ---- DIFF_TERM => TRUE, -- Differential Termination ---- IBUF_LOW_PWR => TRUE) -- Low power (TRUE) vs. performance (FALSE) setting for referenced I/O standards ---- IOSTANDARD => "LVDS_25") -- port map ( -- CEB =>'0', -- O => SYS_REF_CLOCK, -- Clock buffer : out -- I => SYS_REF_CLOCK_p, -- Diff_p clock buffer : in (connect directly to top-level port) -- IB => SYS_REF_CLOCK_n -- Diff_n clock buffer : in (connect directly to top-level port) -- ); IBUFDS_inst2: IBUFDS generic map ( DIFF_TERM => TRUE, -- Differential Termination IBUF_LOW_PWR => TRUE, -- Low power (TRUE) vs. performance (FALSE) setting for referenced I/O standards IOSTANDARD => "LVDS_25") port map ( O => SYS_REF_CLOCK, -- Clock buffer : out I => SYS_REF_CLOCK_p, -- Diff_p clock buffer : in (connect directly to top-level port) IB => SYS_REF_CLOCK_n -- Diff_n clock buffer : in (connect directly to top-level port) ); OBUFGDS_inst3: OBUFDS -- generic map ( -- DIFF_TERM => TRUE, -- Differential Termination -- IBUF_LOW_PWR => TRUE) -- Low power (TRUE) vs. performance (FALSE) setting for referenced I/O standards -- IOSTANDARD => "LVDS_25") port map ( I => rx_core_i, -- Clock buffer : out O => SYNCINB_n, -- Diff_p clock buffer : in (connect directly to top-level port) OB => SYNCINB_p -- Diff_n clock buffer : in (connect directly to top-level port) ); MMCME2_BASE_inst : MMCME2_BASE generic map ( BANDWIDTH => "OPTIMIZED", -- Jitter programming (OPTIMIZED, HIGH, LOW) CLKFBOUT_MULT_F => 4.0, -- Multiply value for all CLKOUT (2.000-64.000). CLKFBOUT_PHASE => 0.0, -- Phase offset in degrees of CLKFB (-360.000-360.000). CLKIN1_PERIOD => 5.0, -- Input clock period in ns to ps resolution (i.e. 33.333 is 30 MHz). -- CLKOUT0_DIVIDE - CLKOUT6_DIVIDE: Divide amount for each CLKOUT (1-128) CLKOUT1_DIVIDE => 4, CLKOUT2_DIVIDE => 8, CLKOUT3_DIVIDE => 16, CLKOUT4_DIVIDE => 32, CLKOUT5_DIVIDE => 64, CLKOUT6_DIVIDE => 1, CLKOUT0_DIVIDE_F => 8.0, -- Divide amount for CLKOUT0 (1.000-128.000). -- CLKOUT0_DUTY_CYCLE - CLKOUT6_DUTY_CYCLE: Duty cycle for each CLKOUT (0.01-0.99). CLKOUT0_DUTY_CYCLE => 0.5, CLKOUT1_DUTY_CYCLE => 0.5, CLKOUT2_DUTY_CYCLE => 0.5, CLKOUT3_DUTY_CYCLE => 0.5, CLKOUT4_DUTY_CYCLE => 0.5, CLKOUT5_DUTY_CYCLE => 0.5, CLKOUT6_DUTY_CYCLE => 0.5, -- CLKOUT0_PHASE - CLKOUT6_PHASE: Phase offset for each CLKOUT (-360.000-360.000). CLKOUT0_PHASE => 0.0, CLKOUT1_PHASE => 0.0, CLKOUT2_PHASE => 0.0, CLKOUT3_PHASE => 0.0, CLKOUT4_PHASE => 0.0, CLKOUT5_PHASE => 0.0, CLKOUT6_PHASE => 0.0, -- CLKOUT4_CASCADE => FALSE, -- Cascade CLKOUT4 counter with CLKOUT6 (FALSE, TRUE) DIVCLK_DIVIDE => 1, -- Master division value (1-106) REF_JITTER1 => 0.0, -- Reference input jitter in UI (0.000-0.999). STARTUP_WAIT => FALSE -- Delays DONE until MMCM is locked (FALSE, TRUE) ) port map ( -- Clock Outputs: 1-bit (each) output: User configurable clock outputs CLKOUT0 => OPEN, -- 1-bit output: CLKOUT0 CLKOUT0B => OPEN, -- 1-bit output: Inverted CLKOUT0 CLKOUT1 => rx_core_4x, -- 1-bit output: CLKOUT1 CLKOUT1B => OPEN, -- 1-bit output: Inverted CLKOUT1 CLKOUT2 => rx_core_2x, -- 1-bit output: CLKOUT2 CLKOUT2B => OPEN, -- 1-bit output: Inverted CLKOUT2 CLKOUT3 => rx_core_i, -- 1-bit output: CLKOUT3 CLKOUT3B => OPEN, -- 1-bit output: Inverted CLKOUT3 CLKOUT4 => OPEN, -- 1-bit output: CLKOUT4 CLKOUT5 => OPEN, -- 1-bit output: CLKOUT5 CLKOUT6 => OPEN, -- 1-bit output: CLKOUT6 -- Feedback Clocks: 1-bit (each) output: Clock feedback ports CLKFBOUT => CLKFBOUT, -- 1-bit output: Feedback clock CLKFBOUTB => OPEN, -- 1-bit output: Inverted CLKFBOUT -- Status Ports: 1-bit (each) output: MMCM status ports LOCKED => OPEN, -- 1-bit output: LOCK -- Clock Inputs: 1-bit (each) input: Clock input CLKIN1 => SYS_REF_CLOCK_1, -- 1-bit input: Clock -- Control Ports: 1-bit (each) input: MMCM control ports PWRDWN => '0', -- 1-bit input: Power-down RST => '0', -- 1-bit input: Reset -- Feedback Clocks: 1-bit (each) input: Clock feedback ports CLKFBIN => CLKFBIN -- 1-bit input: Feedback clock ); BUFG1 : BUFG port map ( O => CLKFBIN, -- 1-bit output: Output feedback clock (connect to feedback input of DCM/PLL) I => CLKFBOUT -- 1-bit input: Feedback clock input (connect to input port) ); BUFG0 : BUFG port map ( O => SYS_REF_CLOCK_1, -- 1-bit output: Output feedback clock (connect to feedback input of DCM/PLL) I => SYS_REF_CLOCK -- 1-bit input: Feedback clock input (connect to input port) ); BUFG2 : BUFG port map ( O => rx_core_4x_g, -- 1-bit output: Output feedback clock (connect to feedback input of DCM/PLL) I => rx_core_4x -- 1-bit input: Feedback clock input (connect to input port) ); BUFG3 : BUFG port map ( O => rx_core_2x_g, -- 1-bit output: Output feedback clock (connect to feedback input of DCM/PLL) I => rx_core_2x -- 1-bit input: Feedback clock input (connect to input port) ); BUFG4 : BUFG port map ( O => rx_core_clk, -- 1-bit output: Output feedback clock (connect to feedback input of DCM/PLL) I => rx_core_i -- 1-bit input: Feedback clock input (connect to input port) ); ADC_p <=ADC3_p&ADC2_p&ADC1_p&ADC0_p; ADC_n <=ADC3_n&ADC2_n&ADC1_n&ADC0_n; x_jesd204_phy_0 : jesd204_phy_0 PORT MAP( tx_sys_reset => tx_sys_reset, rx_sys_reset => reset, ------------- tx_reset_gt => tx_reset_gt, rx_reset_gt => rx_reset_gt, ------------ tx_reset_done => tx_reset_done, rx_reset_done => rx_reset_done, qpll_refclk => SYS_REF_CLOCK_1, ------------------------qpll_refclk,--SYS_REF_CLOCK_1, ------------------------ common0_qpll_lock_out => common0_qpll_lock_out, common0_qpll_refclk_out => common0_qpll_refclk_out, common0_qpll_clk_out => common0_qpll_clk_out, rxencommaalign => rxencommaalign, ---------------- tx_core_clk => tx_core_clk, txoutclk => txoutclk, rx_core_clk => rx_core_clk, ------------------ rxoutclk => rxoutclk, drpclk => SYS_REF_CLOCK_1, ------------------------qpll_refclk,--*SYS_REF_CLOCK_1, -- gt_prbssel => "000", gt0_txcharisk => gt0_txcharisk, gt0_txdata => gt0_txdata, gt1_txcharisk => gt1_txcharisk, gt1_txdata => gt1_txdata, gt2_txcharisk => gt2_txcharisk, gt2_txdata => gt2_txdata, gt3_txcharisk => gt3_txcharisk, gt3_txdata => gt3_txdata, gt0_rxcharisk => gt0_rxcharisk, gt0_rxdisperr => gt0_rxdisperr, gt0_rxnotintable => gt0_rxnotintable, gt0_rxdata => gt0_rxdata, gt1_rxcharisk => gt1_rxcharisk, gt1_rxdisperr => gt1_rxdisperr, gt1_rxnotintable => gt1_rxnotintable, gt1_rxdata => gt1_rxdata, gt2_rxcharisk => gt2_rxcharisk, gt2_rxdisperr => gt2_rxdisperr, gt2_rxnotintable => gt2_rxnotintable, gt2_rxdata => gt2_rxdata, gt3_rxcharisk => gt3_rxcharisk, gt3_rxdisperr => gt3_rxdisperr, gt3_rxnotintable => gt3_rxnotintable, gt3_rxdata => gt3_rxdata, rxn_in => ADC_n, -------------------- rxp_in => ADC_p, ------------------- txn_out => txn_out, txp_out => txp_out ); x_jesd204_0: jesd204_0 port map ( rx_core_clk => rx_core_clk, rx_reset_done => rx_reset_done, rx_reset => rx_reset, rx_sysref => rx_sysref, gt0_rxcharisk => gt0_rxcharisk, gt0_rxdata => gt0_rxdata, gt0_rxdisperr => gt0_rxdisperr, gt0_rxnotintable => gt0_rxnotintable, gt1_rxcharisk => gt1_rxcharisk, gt1_rxdata => gt1_rxdata, gt1_rxdisperr => gt1_rxdisperr, gt1_rxnotintable => gt1_rxnotintable, gt2_rxcharisk => gt2_rxcharisk, gt2_rxdata => gt2_rxdata, gt2_rxdisperr => gt2_rxdisperr, gt2_rxnotintable => gt2_rxnotintable, gt3_rxcharisk => gt3_rxcharisk, gt3_rxdata => gt3_rxdata, gt3_rxdisperr => gt3_rxdisperr, gt3_rxnotintable => gt3_rxnotintable, rx_aresetn => rx_aresetn, rx_reset_gt => rx_reset_gt, rxencommaalign_out => rxencommaalign_out, rx_tvalid => rx_tvalid, rx_tdata => rx_tdata, rx_start_of_frame => rx_start_of_frame, rx_end_of_frame => rx_end_of_frame, rx_start_of_multiframe => rx_start_of_multiframe, rx_end_of_multiframe => rx_end_of_multiframe, rx_frame_error => rx_frame_error, rx_sync => rx_sync, s_axi_aclk => s_axi_aclk, s_axi_aresetn => s_axi_aresetn, s_axi_awaddr => s_axi_awaddr, s_axi_awvalid => s_axi_awvalid, s_axi_awready => s_axi_awready, s_axi_wdata => s_axi_wdata, s_axi_wstrb => s_axi_wstrb, s_axi_wvalid => s_axi_wvalid, s_axi_wready => s_axi_wready, s_axi_bresp => s_axi_bresp, s_axi_bvalid => s_axi_bvalid, s_axi_bready => s_axi_bready, s_axi_araddr => s_axi_araddr, s_axi_arvalid => s_axi_arvalid, s_axi_arready => s_axi_arready, s_axi_rdata => s_axi_rdata, s_axi_rresp => s_axi_rresp, s_axi_rvalid => s_axi_rvalid, s_axi_rready => s_axi_rready ); i_ILA55 : ila_0 port map ( clk => rx_core_clk,--inClk, probe0 => trig0, probe1 => trig1, probe2 => trig2, probe3 => trig3, probe4 => trig4 ); trig0(0)<=rx_tvalid; trig1<=rx_tdata(15 downto 0); trig2<=rx_tdata(31 downto 16); trig3<=rx_tdata(47 downto 32); trig4<=rx_tdata(63 downto 48); end Behavioral; -

Проблема с AD9528

Art55555 ответил Art55555 тема в Цифровые схемы, высокоскоростные ЦС

Ура! после изменения 202 на 03, все стало калиброваться. в конце всех настроек обязательно VCO-calibration. Самураю СПАСИБО! Тема пока актуальна, дальше меня ждут упражнения с SysRef и JESD. -

Проблема с AD9528

Art55555 ответил Art55555 тема в Цифровые схемы, высокоскоростные ЦС

Добрый день! 0x202, 0x03 - сейчас буду проверять. 1. 2. 3.Да, VXCO у нас Si570, реально выдаёт хороший 100 МГц, я проверял лично. Тут вот ещё что есть: https://analogdevices.telligenthosting.net/clock_and_timing/f/q-a/109939/ad9528-pll2-unlock/325607#325607 -

Проблема с AD9528

Art55555 ответил Art55555 тема в Цифровые схемы, высокоскоростные ЦС

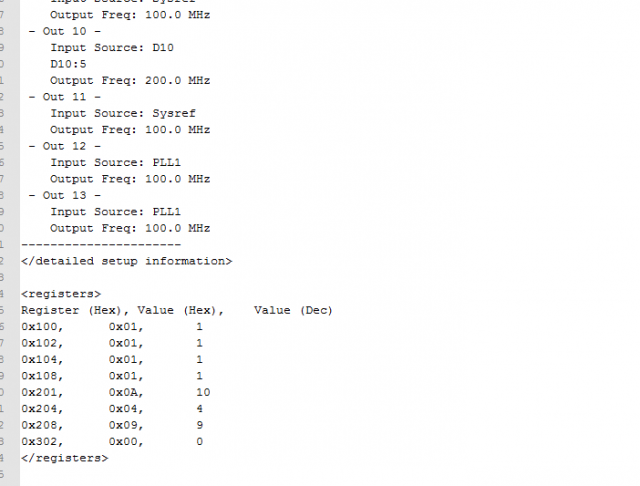

Больше параметров <registers> Register (Hex), Value (Hex), Value (Dec) 0x100, 0x01, 1 0x102, 0x01, 1 0x104, 0x01, 1 0x108, 0x01, 1 0x200, 0x03, 3 0x201, 0x0A, 10 0x202, 0x83, 131 0x203, 0x02, 2 0x204, 0x04, 4 0x205, 0x6C, 108 0x208, 0x09, 9 0x302, 0x00, 0 </registers> после этого VCO-calibration и считывание 508-509: 508 -11110000 509 -00001000 -

Проблема с AD9528

Art55555 ответил Art55555 тема в Цифровые схемы, высокоскоростные ЦС

Дело в том, что значения для этих регистров я генерил в программе AD9528 Evolution Software. Тем не менее, я поподавал разные значения на 201-209, потом проводит процедуру VCO-калибрации. Результат пока такой же(( -

Проблема с AD9528

Art55555 ответил Art55555 тема в Цифровые схемы, высокоскоростные ЦС

Пока мне нужно получить вот такую систему, чуть позже с сисрефом разберусь. В AD 9528Evalution Software конфигурирую то, что мне нужно. Далее, экспортирую регистры, которые по своим значениям отличаются от стандартных, в STP-файл. Вот они: Команду 0000 18 (адрес + данные) даю, чтобы видеть по SPI-ответ микросхемы. Команду 0000 81 - софт ресет - всегда даю перед всеми настройками. PLL по-прежнему не калибруется. Если же после всех регистров проделать команды с калибровкой (203 регистр), то : Регистр 508 выдаёт F0 Регистр 509 выдаёт 08 PLL2-LOCK в нуле. Да, видел не туда комутил (получилось "пробросить" 100 МГц-вый сигнал на 0-выход - здесь всё получилось) -

Проблема с AD9528

Art55555 ответил Art55555 тема в Цифровые схемы, высокоскоростные ЦС

До настройки регистров (считываю): 505 -00 506-00 507-00 508-10 509-10 Видно, что PLL не LOCK, VCXO-incorrect. После записанных регистров (указанных выше), я их прочитал, всё соответсвует. Но контрольные регистры читаются так: 505 -00 506-00 507-00 508-30 (VCXO-correct - статус изменился) 509-10 PLL - не LOCKED!! -

Проблема с AD9528

Art55555 опубликовал тема в Цифровые схемы, высокоскоростные ЦС

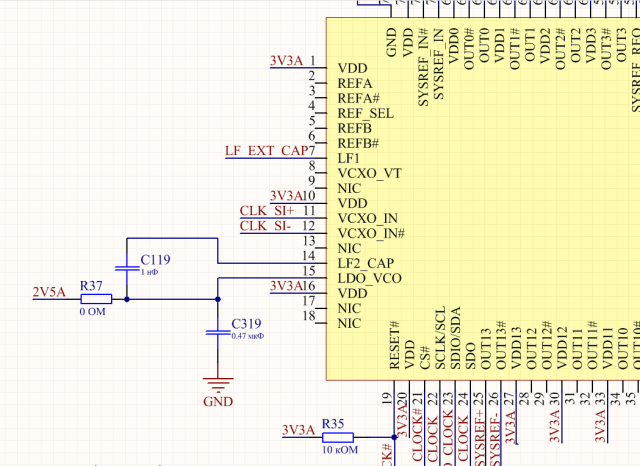

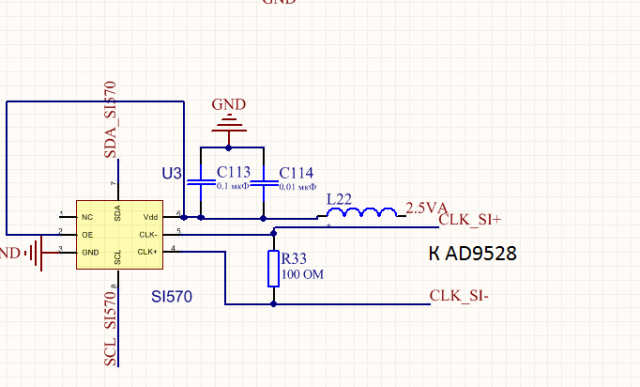

Работаю с микросхемой AD9528. На вход VXCO подаётся дифференциальный сигнал с Si570 (100 МГц). На выходе OUT0 необходимо получить 1 ГГц. Но пока хочу 20 МГц. Запускаю следующую последовательность: 0x000, 0x18, 1 0x000, 0x81, 1 0x100, 0x01, 1 0x102, 0x01, 1 0x104, 0x01, 1 0x108, 0x01, 1 0x201, 0xC0, 192 0x204, 0x03, 3 Перед каждой отправкой пускаю 0x00F 0x01, Далее, для проверки, запускаю процедуру чтения по этим регистрам - всё правильно, то что было записано, то и читается - правильно. На выходе ничего не меняется - какой-то дребезг идёт. Кто-нибудь работал с данной микросхемой? -

Совершенно верно, нужен аналог Sodimm только с тремя или четырьмя чипами. С 2-х канальным контроллером всё понятно.

-

Ранее использовал Artix7 в связке с Sodimm DDR2. На данный момент рассматривается вариант перехода на DDR3, отказавшись от планки SODIMM. Возможно-ли подключить несколько (2-3) отдельных чипов DDR3 к одному контроллеру MIG? Как при этом настраивать MIG? Как трассировать? Куда смотреть и чего читать по этой теме? Помогите пожалуйста.

-

Мда... Есть какой-нибудь выход из ситуации? Планок с однним ранком не нашел в продаже. MT8HTF25664HZ-800C1 от 100 штук (8 недель leed time) и стоит $160

-

Спасибо за ответ. MIG поддерживает работу с планками 2 ранка?

-

Проблема с DDR2

Art55555 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Sodimm DDR2 подключена к Artix7. Использую планку MT8HTF25664HZ-800C1. Сделал контроллер MIg. В ПЛИС сделан кольцевой буфер (пишу с большой скоростью, читаю медленнее). С данной планкой проблем нет. Вставляю другую планку, например PSD22G8002S, характеристики такие же - 2GB PC2-6400 CL6. Начинаю писать и читать, первые примерно 70 МБ - норм, потом данные не верные. Если сначала пишу, а потом только читаю, то проблем нет. В чем может быть причина? -

05 04.bmp

-

Проблемы с записью данных во флешку MT25Q

Art55555 опубликовал тема в Цифровые схемы, высокоскоростные ЦС

Есть Artix 7 и MT25Q. Запрос значений регистров, считывание производителя и кода устройства работает - отвечает корректно, всё ок. Но при записи и чтении не "падает" MISO, нет никакой реакции на мое MOSI, CLK, CS. Последовательность записи: 06 Write En 02 Page Prog 04 Write Disn Последовательность чтения:просто подаю команду 03. Реакции нет. Что-нибудь посоветуете? -

Читал, естественно. У нас температура 70 и более.