Petrovich

-

Постов

249 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные Petrovich

-

-

7 hours ago, _4afc_ said:

Может посмотреть в сторону Gowin GW1NR c ОЗУ внутри

SDR SDRAM

Аccess time: 4.5 ns/4.5 ns

Clock rate: 200/166/143 MHz

Data width: 16bits

Synchronous operation

Internal pipeline architecture

Fourinternal Banks (1024K x 16 bits x 4BANK)

Programmable mode

-Column address strobe latency: 2 or 3

-Burst length: 1, 2, 4, 8 bytes or full page

-Burst type: sequential mode or interval mode

-Burst-Read-Single-Write-Burst stop function

Byte masking function

Auto refresh and self refresh

4,096 refresh cycle / 64 ms

PSRAM

Clock frequency:166 MHz, the maximum frequency can beDDR332

32Mb storage space for one PSRAM

Double-edge data transmission

Data width: 16bits(QN88/LQ144) / 32bits (MG100)

Read/write data latching (RWDS)

Temperature compensatedrefresh

Partial arrays self-refresh(PASR)

Hybird sleepmode

Это интересный вариант. Спасибо. Почитаю.

-

Сейчас применяется SRAM 256К х 16

Нужно увеличить как минимум до 2-4М х16

Читать/писать нужно каждые 20nc. Это период семплирования аналогового сигнала и естественно это должно происходить равномерно.

-

Однако... :)

Я уж тогда десяток SRAM поставлю

-

8 minutes ago, MegaVolt said:

По моему никакая.... DDR рассчитана на чтение и запись большими кусками с огромными накладными расходами. Это оправдано при наличии внутреннего статического кеша. Т.е. прямой работы с DDR обычно нету. Есть страничный обмен между DDR и кешем с которым уже идёт работа.

Т.е. в вашем случае два буфера на размер страницы. Пока работаем с первым буфером второй буфер подгружается из DDR или выгружается обратно.

Но это всё подходит только при последовательном доступе. Если у вас полностью случайный доступ то даже не знаю что подсказать. Вам придётся найти DDR которая будет иметь накладные расходы меньше 20 тактов на запись и чтение...Печально, Вы подтвердили мои сомнения.

Доступ таки произвольный, буферы не помогут.

Спасибо за ответ.

-

Помогите с выбором пожалуйста.

Сейчас есть устройство имеющее FPGA и SRAM 7ns.

Каждые 20ns читается из памяти и тут же записывается в память по тому самому адресу.

С нынешней SRAM все работает прекрасно. Но стало не хватать объема, решили перейти на SDRAM.

Подскажите, какая из них ( DDR DDR2 DDR3 ... ) по скорости аналогична или лучше нынешней SRAM при таком режиме чтения/записи?

-

17 hours ago, ViKo said:

При исправной конфигурации DONE должен в единицу прыгнуть. У вас - нет. Значит, не сконфигурировалось.

nSTATUS в нуле говорит об ошибке.Похоже, надо перепаивать BGA.

Проблема решилась. оказалось все очень просто.

Линия CONF_DONE была хитро замкнута, толи через грязь на плате, то ли через волосок припоя, на землю.

Причем с приличным сопротивлением, но достаточным, что бы притянуть ее к 0.

Промывка, чистка, все привело в норму.

Спасибо всем за участие и советы.

-

1 minute ago, ViKo said:

При исправной конфигурации DONE должен в единицу прыгнуть. У вас - нет. Значит, не сконфигурировалось.

nSTATUS в нуле говорит об ошибке.Похоже, надо перепаивать BGA.

Да, судя по всему... как это не печально... :(

Как будет результат, напишу.

-

2 minutes ago, ViKo said:

Так CONFIG_DONE что показывает?

Сидит все время в нуле. Вот это то и странно...

Но если принятнуть вручную nCONFIG к нулю, то nSTATUS тоже переходит в 0.... то есть nCONFIG доходит до нужного места...

ненавижу BGA!

-

2 minutes ago, des00 said:

единицы и нули подайте. это более простой вариант. но по идее должно было работать. Может все же вы принимаете желаемое за действительное?

Про конфигурацию давно это было, надо документацию читать.

Подавал и 1 и 0 конечно и меандр... до лампочки.

По конфигурации. читал, точно такая же схема включения на другой плате с 10CL025. Подтянуто вверх nCONFIG и все нормально.

А тут как заколдованна...

-

Таки нет... завожу сигнал на L21 вывожу с L22.

Та же история... нет выхода. Уж эти выводы точно находятся в одном банке с JTAG ?

3 minutes ago, des00 said:ну либо вы принимаете желаемое за действительное и плис, не смотря на процесс заливки по жтаг, все же не запускается. Т.е. активности на conf_done нет. А такое может быть, если сразу после JTAG прошивки, инициализируется прошивка по PS. Проц же не запаян. Может там поискать?

Так подтянуто все что нужно.

Кроме nCONFIG еще разве что то должно быть подтянуто?

-

1 minute ago, des00 said:

ноги на пролет замыкаете из того же банка что и жтаг? у каждого банка свое питание ;)

а про надпись...есть те кто паттерны делает сам и иногда ноги "путает" вот потом веселье то начинается, когда нужно плату под бга поправить)

Подытожу. То что шьется и определяется это хорошо, если вы ставите в прошивке 1 и 0 на порты вводы вывода, а их там нет, то скорее всего проблема в питании банков.

Ну это самое логичное конечно, но не могли же питания ВСЕХ банков кроме JTAGа не припаятся.

Попробую вывести сигнал но ножки из банка JTAG.

-

1 minute ago, des00 said:

ИМХО проблемы с землей/питание банков. Как вариант, микросхема не та, или паттерн не тот. хотя в это сложно поверить)

Если бы была не та, то не обнаружилась бы JTAGом.

Да и надпись на ней есть :)

-

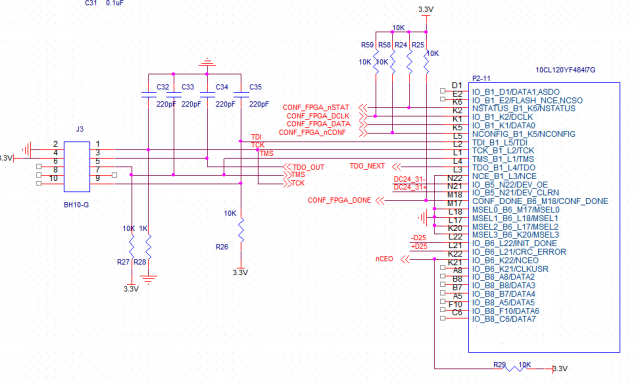

Привет всем.

На плате установлена 10CL120YF484I7G BGA484.

Включена с программирование по JTAG и PS.

Схема прилагается.

Режим PS пока не применяется, не установлен еще контролер.

JTAGом обнаруживается и прошивка заливается. Но!

По окончании заливки ни чего не работает!

Прошивка уже упрощенна до предела. Просто транслируется сигнал с одной ножки на другую.

На выходах просто третье состояние!

Все питание и земли подведены.

может такое происходить, если где не подпаялись выводы, земли или питания?

Ни каких мыслей,что происходит уже не осталось...

Такая же микросхема но не BGA и менее емкая , 10CL025 работает чудесно!

Буду благодарен, за любой совет!

-

пардон... адрес неверный

gura(at)novotest.com.ua

-

Для выполнения множества разовых работ требуется специалист по ЦОС. Требуется не программирование, а алгоритмизация и мат. моделирование.

Подробности в личку или почтой

gura(at)novotest.ua

-

Заработало. Все дело было в

волшебных пузырькахволшебном файлике. :)Спасибо.

-

Хм... а какой у Вас Квартус ?

И взяли Вы его там где обычно? ;)

-

Собираюсь заложить в новое устройство Cyclone 10LP.

С удивлением обнаружил, что для него нет IP FIR II !

Это так и задумано, или я не досмотрел?

Кто то уже использовал Cyclone 10LP. ?

-

Буду думать. Спасибо.

С описание памяти все нормально. Синтезируется именно как память.

-

Вопрос к спецам по Верилогу.

Стояла задача перемести сишную процедуру уплотнения данных для отображения на экране в FPGA.

Вроде все просто. И даже работает... но! Только если применяются блокирующие присваивания, что мне очень и очень не нравится.

Подскажите, что не так и как можно уйти от блокирующих присваиваний?

Во вложения файлики с кодом на си и Верилоге.

-

Разработка электронных устройств.

Большой опыт разработок с использование PIC, PIC32, ARM, BlackFin, FPGA ....

После разработки получаете полный пакет документации.

Возможно мелкосерийное производство.

Малые сроки, разумные расценки.

Оценка стоимости после согласования ТЗ, до начала работ.

Техсопровождение произведенных устройств.

обращаться: gura0675606626(собака)gmail.com

-

Не менее 2-ти летний опыт работы, базовые знание схемотехники,

умение качественной пайки, аккуратность,ответственность.

Творческий подход к работе.

Обязанности: Монтаж и наладка электронных приборов ( без пайки плат )

Полный рабочий день, зарплата достойная

по всем вопросам gura0675606626(собака)gmail.com

-

Однако..... :w00t: а сказать это нам???

Ну я считал что это очевидно, из уровней сигналов. Пардон, если кого ввел в заблуждение.

-

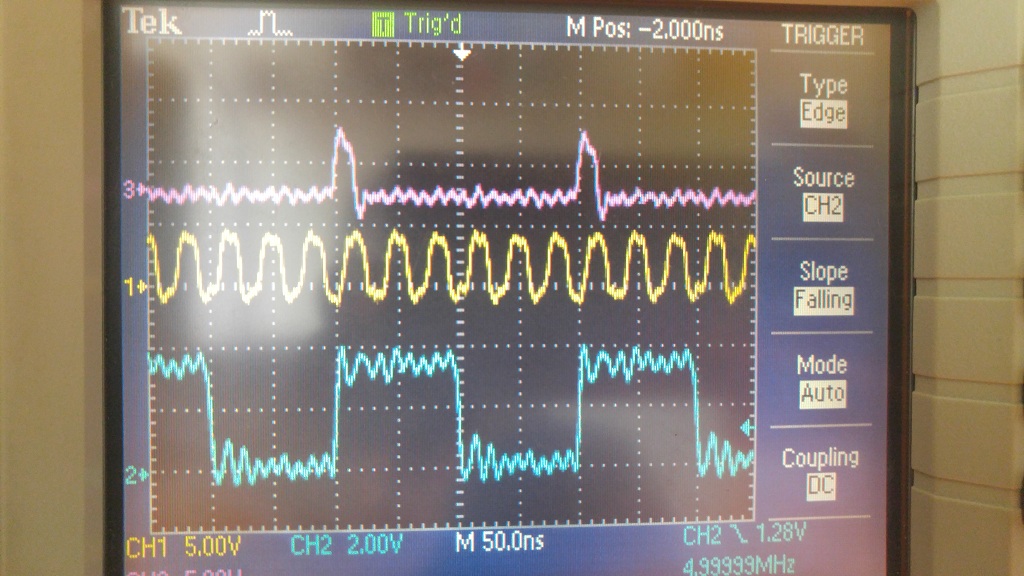

Как настройка входов могла влиять на осциллограммы?

Это были осциллограммы взяты из MAX10, после преобразования входных LVDS сигналов от AD9272. Так вот, преобразование от LVDS к обычным уровням происходило не правильно, что и приводило к затягиванию единичек.

Теперь выглядит так. Что не может не радовать :)

Выбор SDRAM

в Цифровые схемы, высокоскоростные ЦС

Опубликовано · Пожаловаться

https://www.issi.com/WW/pdf/61-64WV25616EDBLL.pdf

Пардон. 8ns.