VladimirB

Свой-

Постов

620 -

Зарегистрирован

-

Посещение

Весь контент VladimirB

-

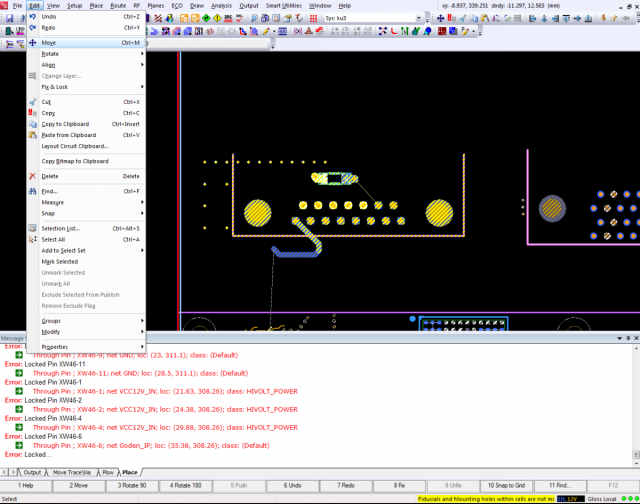

1) У меня Drill Drawing Throught отключён и не отображается, см. скриншот из 6 поста, а ошибка есть. 2) Почему тогда в ошибке пишется про Fiducials и Mounting Holes, а компоненты в которых их нет легко перемещаются?

-

Добрый день. Проблемный проект в приложении. Там один разъём и при попытке его сдвинуть вместе с дорожками в режиме Select Mode выдаёт ошибку, описанную выше. PCB2fill.rar

-

Но такие глюки сильно напрягают. Т.е. мне теперь на плате нужно будет удалять и вставлять заново все компоненты с монтажными отверстиями и реперными точками в Cells'ах стараясь не повредить при этом дорожки. И в целом целесообразность перехода на новую версию Ментора становиться под вопросом, т.к. помимо сильно измененного интерфейса вплывают глюки.

-

Добрый день. Компонент отдельно двигается. Всё разлочено. Но при выделении в режиме Selection mode и попыткой его сдвинуть выдаёт ошибку (см. скриншот). В cell editor не нашёл ничего криминального. Версия Xpedition 2.5. Пробовал делать ECO с полным удалением локальной библиотеки - не помогает. Хотел сегодня подготовить отдельный проект с этим разъёмом, но в нём всё заработало из коробки. Более того, когда я удалил с большой платы этот разъём и поставил заново - тоже всё стало двигаться. Что это такое - непонятно.

-

Тестирую Xpedition и у меня такая же проблема возникла. На EE 7.9.1. всё двигается в режиме Circuits Move and Copy, а на Xpedition пишет про Mounting Holes внутри компонентов. Компонеты без монтажных отверстий двигаются. Может кто-нибудь знает как решить данную проблему? P.S. Галочки ставил - не помогает.

-

Это Virtex 5, там блокировочная керамика со сверхнизкой индуктивностью выводов прямо под термораспределительной крышкой распаяна, вблизи кристалла, и по даташиту других маленьких кондёров не требуется. Исключением являются самые маленькие кристаллы XC5VLX20 и XC5VLX30 в 324/323 корпусах - у них встроенных кондёров нету.

-

Если у вас раньше работало, а потом перестало, то надо искать что изменилось. Может платы изготавливаются на другом заводе и/или толщина медной фольги другая (например была 35мкм а стала 18мкм). Может ревизия кристалла ПЛИС другая (она пишется, когда в Impact нажимаешь Get Device ID). Нам как-то китайцы привезли перемаркированные инженерные образцы Xilinx с ревизией кристалла 0, вместо 4 у production. Или партия/наименование/изготовитель конденсаторов по питанию отличается. Парт номер ПЛИС вы не назвали, но на мой взгляд танталовых конденсаторов по питанию ядра маловато, проверьте соответствует ли их номинал Virtex-5 FPGA PCB Designer’s Guide UG203. И по питанию банков также.

-

А какие номиналы резисторов R3 и R4 ??? И какое напряжение после делителя на Vgg получается???

-

DDR2

VladimirB ответил juvf тема в Работаем с ПЛИС, области применения, выбор

Может и не совсем по теме. У нас как-то на серийном изделии тоже пара плат в брак ушло. На плате ПЛИС Virtex6 и ATMega8 с друг другом взаимодействовали и подвисали через 1-2 секунды после включения питания. Причём подвисание было только на холодных платах (не прогревшихся выше +25град). Я дня три парился, перепаивал всё что мог, осциллографом тыкался, в морозилке платы охлаждал - всё вроде в норме, а не работает. Оказалось, что кварцевый генератор, от которого всё тактировалось, при старте сначала давал пару импульсов тактовой, потом затыкался на 10-20 мс, а потом начинал уже нормально генерить (заметил случайно). И микроконтроллеру это сильно не нравилось - он зависал на аппаратном уровне так, что программа даже не успевала стартовать. Вылечилось установкой повышенного startup time во FUSE битах. Так что причина может оказаться где-то в окружении и совсем не там, где ожидаешь. P.S. Чтобы DDR2 не заработала из-за звона, это надо постараться. Особенно, когда разработчик ПП слышал про гиперлинкс. Мне как-то на плате с Virtex6 и DDR2-800 все терминаторы запаяли 471Ом вместо 47Ом и всё работало. А я видал рабочие серийные платы с DDR3, на которых и импеданс дорожек вообще не был согласован и разрывы в плейнах были под данными и адресами во внутренних слоях (правда только с одной стороны, с другой был непрерывный плейн). -

Это падение напряжения на катушках индуктивности, через которые выходной каскад питается. У вас на плате эти индуктивности имеют большее резистивное сопротивление по постоянке, чем индуктивности на плате производителя. Тупо провод толще в намотке или количество витков (индуктивность) разное.

-

Выравнивание длин DDR3

VladimirB ответил speedtree тема в Работаем с трассировкой

Почему не может? DDR3 Write Leveling вроде должен эту задержку компенсировать автоматом. Иначе как тогда fly-by разводить: клок идёт последовательно через все чипы памяти, а DQS напрямую к каждому ? На 4 чипах памяти 4 см. может набежать легко. Другое дело поддерживает ли Write Leveling ваш контроллер памяти и в каких пределах он может задержку выровнять? P.S. Посмотрел TN4614 - это же манускрипт из музея 2006 года. И речь там про обычную DDR память без индексов 2 или 3. -

Пины под BGA

VladimirB ответил shunix тема в Работаем с трассировкой

Чего-то круто для первого раза: ПЛИС Xilinx в BGA c шагом 0.5 со сплошной матрицей шариков. HDI попахивает. -

Про изъюзанность и безпроблемность знаем и сами применяли её много раз. Просто ПЛИС были с железным МАКом и готовый драйвер был в SDK. А по этой теме вроде направление куда копать понятно, будет время добьём. На новые Марвеллы (как на ZedBoard) будем переходить обязательно, т.к. месяц назад, наконец-то, добрые люди выложили сверхсекретный даташит в закрома.

-

ArriaV, где ты?

VladimirB ответил _sda тема в Работаем с ПЛИС, области применения, выбор

С Кинтексами проблем нет. Сами покупаем небольшими партиями. Только надо смотреть при разработке ПП и закладываться на распространённые модели. Есть там пара-тройка редких в экзотических корпусах с большим кол-вом трансиверов. P.S. Главное к официалам Xilinx не обращаться, чтобы нервы в порядке сохранить. От них толку мало стало - на партии меньше 10 Кинтексов 325T ценник дороже, чем в кармане привезти с Дижикея. Сроки поставки несколько месяцев выдают. И ещё бывает всякие бумажки просят заполнять. В Макрогруппе менеджеры вообще сонные - пишешь запрос и ждёшь ответа две недели, а бывает забывают ответить. Впечатление такое, что клиенты и деньги их не интересуют. -

Дал другому разработчику FPGA в руки свой старый проект ISE 10.3 с менторовским MAC'ом и попросил переделать под эту плату и поднять гигабит. Гигабит поднялся. 1000BASE-T. Передавали и принимали с loopback через фифо внутри ПЛИС по 5000 пакетов максимальной длины 1500 - ни одной ошибки или потери пакета. Программное обеспечение на ПК и плата теже самые. Завтра попрошу менторовский MAC на 100BASE-TX переделать. Похоже чего-то не так либо с инициализацией 88E1111 или Xilinx TEMAC . Последний вызывает подозрения. Раньше TEMAC был аппаратный, бесплатный, с драйвером и примером в SDK. А теперь софтварный, без драйвера и примера для SDK и ёще и $520 хотят. Может он чего-то с PHY делает не по ГОСТу или в MDIO пишет неправильно?

-

Мы только в FullDuplex работаем - проверяли по осциллографу - две пары задействованы - соответственно коллизий быть не может, а обрезанные пакеты есть. Half Duplex пробовали один раз включать - там всё хорошо было.

-

Передача начинается с ПК по нажатию кнопки в программе - естественно жмём когда хотим. Можем и несколько раз нажать последовательно с паузами - результат не меняется.

-

Появилась новая информация. 1) Если на ПК в свойствах сетевой карты убрать Автопределение скорости и жёстко поставить 100BASE-TX FullDuplex то пакеты между ПК и платой начинают передаваться без ошибок и обрезанных пакетов нет. При этом в 88E1111, при инициализации в регистрах жестко устанавливаем 100BASE-TX FullDuplex и в случае автоопределения сетевой картой скорости, связь идёт в том же режиме. 2)Сетевую карту ПК замыкали кроссовой перемычкой саму на себя - ошибок нет, пакеты все передаются. Вот тут пишут, что Ethernet 100 пролезет везде, и можно ничего не согласовывать и использовать двухслойные и однослойные платы: https://electronix.ru/forum/index.php?showt...p;#entry1488846 Но несмотря на это, у нас всё разведено с расчётом на 1Гбит/c короткими диффпарами 100 Ом (длина 20мм) и стоят согласующие резисторы см. схему.

-

Vivado, т.к. оно поддерживает ограниченное кол-во семейств.

-

Да. Promiscuous mode включён. ОС Win 7. Смотрели на разных ПК. Дык там и ПЛИС другая. Можно попробовать завтра диффпары перекрестить, чтобы ПК проверить. А, чтобы так плату проверить, надо переписывать прошивку, делать генератор и проверятор пакетов.

-

У нас кварцевый генератор AU-25.000MBE-T.

-

Питание смотрели осциллографом с полосой 1ГГц - всё чисто. Кабеля разные пробовали. Короткие, длинные, заводские, самодельные. Ничего не меняется. Также осциллографировали сигналы на выводах разъёма RJ45 со встроенным магнетиксом при вставленном кабеле - они есть только на первых двух дифф.парах MDI0, MDI1 - на остальных контактах разъёма пустота. Если бы бы неправильно включён разъём - то сигналы были бы на других ногах разъёма. Также подпаивал на проводках другой разъём с другой цоколёвкой от HALO - соответственно цоколёвку заново смотрел. Самое обидное - никакой реакции, было бы хоть какое-нибудь ухудшение или улучшение. P.S. На соседней ветке форума вчера бурно обсуждали как на двухслойке 100МБит Ethernet работает. Вроде как преобладало мнение, что 100BASE-TX всё нипочём, и сопротивление волновое можно не согласовывать и длину дорожек по 10см делать. P.S.2 Вот фрагмент платы с Ethernet.

-

Marvell 88E1111 обрезает пакеты

VladimirB опубликовал тема в Работаем с ПЛИС, области применения, выбор

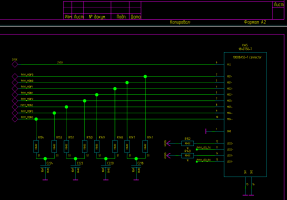

Добрый день. Есть самодельная плата с Kintex7 и Marvell 88E1111. В ПЛИС стоит ядро Xilinx TEMAC из Vivado 16.4. Принимаемые пакеты с MACa берем по интерфейсу AXIstream закольцовываем и отправляем обратно напрямую, без участия DMA и микроблейзов. Сеть 100BASE-TX, Full Duplex - 100МБит/c. Светодиоды на Марвеле, соответствующие светятся. Плату подключаем напрямую к ПК. С ПК отправляем 50 пакетов по 1514 байт с максимально возможной скоростью. Назад в ПК приходят все пакеты, но примерно 2-3 штуки из них обрезанные по длине, случайным образом. Т.е. начало пакета правильное (счётчик), потом он резко обрывается. Косяк на приёме данных с ПК. Смотрели чипскопом обрезанные пакеты идут уже с PHY на MAC. Включили внутри 88E1111 счётчик ошибок CRC, он увеличивается каждый раз на количество битых пакетов. Ещё когда в ПК смотрим обрезанные пакеты Wireshark'oм, то CRC у них правильная, что тоже указывает, что пакет побился на приёме, закольцевался с наружи TEMACa и ушёл обратно уже с новой CRC. Проблема наблюдается на нескольких одинаковых платах. Плата многослойка. От PHY до разъёма с магнетиксом где-то 20 мм. Микросхема PHY 88E1111 вызвала подозрение - перепаял на новую от другого поставщика, с другой датой изготовления - ничего не изменилось. Пробовали менять кабель, перепаивали резисторы согласующие на плате (вместо 50 ом ставили 75, 100, 120), добавлял конденсаторов по питанию, меняли разъём с магнетиксом: вместо MagJack TRP, аккуратно привертолётили HALO HFJ11-1G01ERL. Пробовали менять ПК на ноутбук. Ничего не меняется вообще - стабильно 2-3 пакета на 50 обрезанные. С ПК на ноутбук той же программой передается всё нормально. Питание в норме 2.5В и 1В, цифровое и аналоговое питание 2.5В развязано фильтром. Смотрели осциллографом и питание и сигналы на разъёме Ethernet. Ничего подозрительного не увидели. Подскажите люди добрые, в чём тут может быть проблема? Может еррата какая-нибудь есть? P.S. ещё заметили, что пакеты обрезаются только когда идёт одновременный приём и передача данных. Если данные только принимать и не передавать обратно, то счётчик ошибок CRC в PHY не увеличивается. -

Тактовая AD9361

VladimirB ответил Тимур090793 тема в Цифровые схемы, высокоскоростные ЦС

Опечатки там скорее всего нет, т.к. питание 1.3В Взять любой КМОП буфер, поддерживающий питание 1.3В. Вот первый, например, первый попавшийся в гугле: 74AVCH1T45. Джиттера буфер много не добавит: помниться тут в теме про PLL кто-то фазовые шумы ТиниЛоджиков мерял - они очень низкие получались. Ну и резистивный делитель никто не отменял. Я бы два этих варианта заложил, а там какой лучше окажется. Сами мы на своих платах кварц Epson 40МГц пока юзаем - работает. Внешнее тактирование ещё не пробовали. P.S. ИМХО по AD9361 у аналоговых девиц чего-то выпрашивать на форуме бесполезно. Микросхема сложно-навороченная, а к ней даташитик страниц на 20 приложили и UG на 128 страниц. Вопросов тьма, а ответов на форумах нету. Типовой ответ, такой же как и в UG: "смотрите код на C++". -

Если вы проектировали систему связи (или другой мегадевайс) на AD9364, то посмотрите на её внутренности для начала, как базис для реализации на россыпи. А если вы хотите конкретики, дык и от вас нужна тогда конкретика: 1) скорость передачи/вид модуляции? 2) частотное, временное, кодовое разделение? 3) несущие частоты фиксированы или нужна возможность их перестраивать во всём вашем диапазоне? 4) относительная скорость движения объектов (эффект доплера) 5) характеристики канала связи (городская застройка, открытое поле, канал земля-воздух, канал воздух-воздух). А если со смесителями и тройным преобразованием проблема, то можно ж и без них обойтись: берете АЦП и ЦАП с тактовыми в районе 1.5...3ГГц и цифруете прямо радиоэфир или выдаете сигнал напрямую с ЦАП. И всё делаете в цифре на вашем Кинтексе. Вот, например, в метре от меня на соседнем столе лежит почти готовый радиомодем на ваш диапазон - только фильтры, МШУ и УМ добавить. Никаких смесителей не надо - прямая оцифровка рулит :)