GriXa

-

Постов

54 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные GriXa

-

-

Цитата

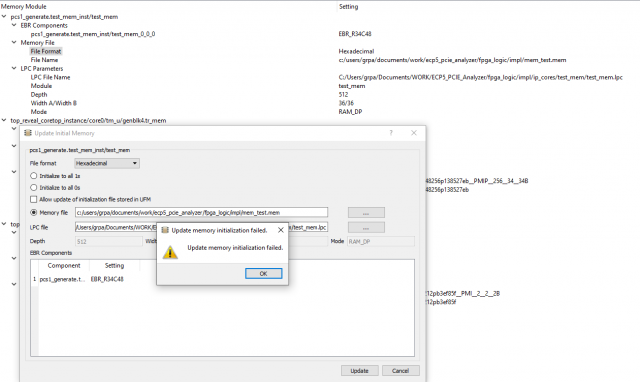

Не уверен. На скриншоте написано failed.

А, да, извиняюсь, не посмотрели и неправильный скриншот отправил.

-

Quote

Можете выложить пример *.mem файла для MICO32 и пример включения BRAM?

Проект, в котором я обновлял память процессора *.mem - файлом, к сожалению, восстановить сейчас не удастся. Но там я BRAM подключал не вручную, он автоматически генерировался при создании ядра mico-процессора. В top-файле я использовал лишь instance всего ядра.

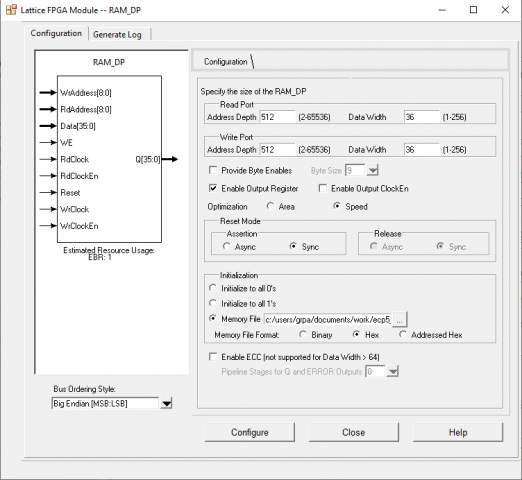

Сейчас я попробовал создать тестовую память в Clarity Designer с такими параметрами:

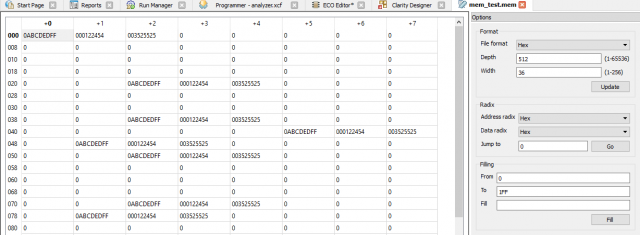

Подгрузил к ней инициализирующий mem-файл:

После компилляции в ECO-editor'е ещё раз попробовал подцепить этот файл, вроде всё получилось удачно:

Я пишу на VHDL, кусок кода с BRAM-памятью выглядит у меня так:

test_mem_inst : entity work.test_mem port map( WrAddress => (others => '0'), RdAddress => q_ra.read_addr(8 downto 0), Data => (others => '0'), WE => '0', RdClock => clk_100, RdClockEn => '1', Reset => rst, WrClock => rx_pclk_1, WrClockEn => '1', Q => mem_data_out );

-

Я использовал ECO-editor для обновления BRAM-блоков с программой для MICO32 soft-процессора. Elf-бинарник, создаваемый при компиляции сишного проекта, конвертировал в *.mem файл и обновлял с помощью ECO-editor'a.

Diamond весьма капризный в плане подключения подобных файлов. Можно для начала попробовать поработать с mem-редактором. Создать новый Memory File (File -> New -> File... -> Others Files -> Memory Files) и поэксперементировать с разными форматами, размерностями и прочим.

-

Да, можно. Для этого есть ECO-Editor. Во вкладке Memory Initialization можно выбрать необходимый BRAM, добавить файл инициализации, сохранить и сгенерировать заново бинарник.

В ECO-Editor'e можно изменять так же параметры многих других компонент ПЛИСины.

-

Добрый день!

Озвучьте, пожалуйста, каой САПР планируется использовать? Судя по изображениям Altium?

-

2 minutes ago, MegaVolt said:

offtop:

На редкость приятная картинка. Что за софт её выдаёт?

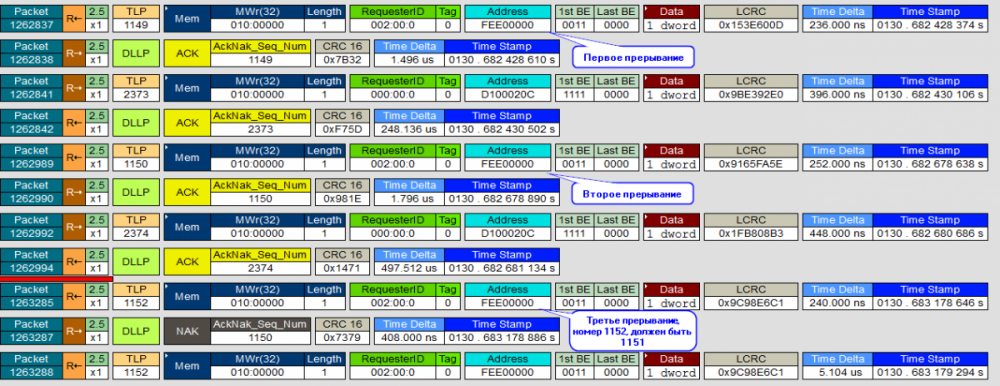

Это анализатор протокола Summit T24 от Teledyne. Софт - Teledyne LeCroy PCIe Protocol Suite

-

Добрый день!

Возникла следующая проблема.

ПЛИС Lattice ECP5UM, PCIExpress Core v6.5 подключен к COM-модулю. В ПЛИС работает таймер, который вызывает прерывание 0. После прерывания необходимо сбросить флаг состояния. Если писать в этот регистр напрямую через JTAG, всё работает нормально. Если это происходить при загрузке ОС, ПЛИС шлёт третее прерывание с неправильным номером пакета на Data Link уровне. Картинка с анализатора прикреплена ниже.

После отправки пакета с неправильным номером, CPU отвечает NAK-пакетом. ПЛИС повторяет попытку еще два раза, затем уходит в LinkTraining, затем повторяет попытку с неправильным номером и так до бесконечности. Абсолютно не понятно, почему ядро в этом случае пропускает один номер. И всегда на третьем прерывании.

Кто-нибудь сталкивался с подобным поведением?

-

Я так понимаю сначала парсит, а потом исправляет определенные константы на нужные для текущего синтеза значения?

Да, именно так. С помощью этого скрипта так же автоматически увеличивается номер версии и дата компилляции. Удобно при чтении регистров узнавать какая именно версия загружена в ПЛИС.

-

Для таких случаев использую отдельный *_pkg.vhd файл, в котором указываю необходимые константы. Tcl-скрипт парсит этот файл, подставляет нужные значения, и, к примеру, запускает компилляцию. В проекте в качестве generic-значения присваиваю эту константу.

Можно так же и в top-файле это делать, но на мой взгляд настраиваемые переменные удобнее держать в одном файле.

-

В своих проектах использую tcl скрипты для автоматического добавления номера версии и времени компиляции проекта.

К примеру, в регистре сохраняется версия прошивки и дата-время компиляции. Для golden и working версии она может быть разная.

Пример такого файла на vhdl

-- created at 07/Dec/2017-13:15:15-- DO NOT EDIT THIS FILE

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

package compile_time_pkg is

constant VER_VALUE : string := "30";

constant COMPILE_TIME : integer := 1512648915;

end package compile_time_pkg;

Скрипт создает этот файл, потом запускает компиляцию. При каждой последующей компиляции увеличивает, к примеру, счетчик версий и изменяет время на текущее. После успешной компиляции - копирует текущую прошивку в отдельную папку с названием, соответствующим данной прошивке. Что-то типа name_working_v12.bit

-

Добрый день!

Содержание документа не смотрел, но рассылать резюме было бы предпочтительнее в pdf-формате.

-

Мы используем Teledyne/Lecroy Summit T28. Пытаемся выловить баги в Virtex-7 PCIe корке, но пока только обнаружили баги в ПО самого анализатора. А что такое Verification IP? Недавно мы также применили аппноту от того же Ксайлинкса, которая позволяет произвести eye scan прямо в рабочем линке. Оказалось, что не все слоты одинаковые и настройки трансиверов очень влияют на размеры глаза.

Поделитесь, пожалуйста, какие именно баги в работе ПО анализатора Summit T28 Вы обнаружили?

-

Есть замечательная книга под названием "Advanced FPGA Design Architecture, Implementation, and Optimization" Steve Kilts. ISBN 978-0-470-05437-6

В книге показано на примерах, как структура дизайна влияет на скорость/пропускную способность/задержки в проекте.

Мне показалось, что там подробно расписано, в каких случаях удобно использовать FSM, где лучше использовать тонну комбинаторной логики, а где кучу маленьких процессов.

Если для описания используется VHDL, то Вам, возможно, было бы интересно обратить внимание еще на Two Process Method (Jiri Gaisler).

-

Опубликовано · Изменено пользователем GriXa · Пожаловаться

Добрый день!

Использую ПЛИС от Lattice (MACHXO3). В верхнем модуле в качестве входов-выходов хочу использовать type record.

Проблема в том, что если в Diamond установить в качестве синтезатора Sinplify, он не сохраняет название сети.

К примеру, есть *_pkg.vhd, где у меня описан type:

package pkg1 is type t_my_type is record test_input_1 : std_logic; test_input_2 : std_logic; test_input_3 : std_logic; end record end package pkg1;

В *_top.vhd использую этот тип:

entity test is port ( .... .... group1 : out t_my_type; .... ); end entity test;

В итоге, после синтеза имею для этих выходов следующие имена цепей:

group1[0]

group1[1]

group1[2]

А хотелось бы, что бы сохранялось полное имя типа

group1.test_input_1

group1.test_input_2

group1.test_input_3

Lattice LSE сохраняет имена как надо, но можно ли сделать подобное в Synplify?

-

А их логический анализатор (Reveal) поддерживает SystemVerilog?

Не могу ответить на этот вопрос. Работаю только с VHDL. Про SV пишут следующее. Так что высока вероятность, что нет.

ЗЫЖ и как по мне использование синплифай это достоинство, а не недостаток (учитывая что он достаётся нахаляву).Использование синплифай это, безусловно, достоинство. Вот только если через годик-другой они его вдруг выкинут из Diamond'а, то могут появиться проблемы со старыми дизайнами. Результаты синтеза Синплифая и Даймонда отличаются как по используемым в ПЛИС ресурсам, так и по времянкам.

-

Все в Лэтисах хорошо, только

1. Сырой родной софт для синтеза. Поэтому они встраивают в свой Даймонд Синплифай. Часто Синплифай дает лучшие результаты. Есть весьма забавный баг с FSM в LSE-синтезаторе. Будут ли они в будущем отказываться от Синплифая - неизвестно. И эта неизвестность немножко напрягает.

2. Очень мало примеров и обучающих материалов. Не сравниться с Ксайлинксом или Альтерой.

3. Сыроватая документация. Можно встретить в двух разных документах противоречащие утверждения.

4. Недоработанная автоматизация сборки проекта. Невозможно с помощью скрипта генерировать IP ядра для ECP5.

Вот-вот должно выйти обновление для Даймонда. Быть может часть недоработок в ней будет исправлена.

Но в итоге вполне себе хорошие ПЛИСЫ по очень приятной цене.

-

А если взять ПЛИС с PCIExpress и прописать в Configruation Header

Class Code 0x07 - Simple Communication Controller,

Sub-Class 0x00

Interface 0x01 ... 0x06 16xxx-compatible

А дальше к нему прикрутить контроллер, к примеру контроллер 16650,

то может он сможет автоматически распознаваться в UEFI?

-

-

По поводу библиотек, как уже написал Tausinov,

нельзя совместно использовать ieee.numeric_std и std_logic_arith.

Как пишут здесь, "The alternative numeric package ieee.std_logic_arith should not be used for new designs"

Ну и тут подробнее: http://insights.sigasi.com/tech/deprecated...-libraries.html.

Для преобразовываете std_logic_vector в signed или unsigned и наоборот, удобно пользоваться шпаргалкой.

-

Добрый день. Проблема может быть в неправильной времянке, неправильно подключеных пинах и еще во многом другом. Я бы Вам посоветовал пощупать это дело осциллографом, чтобы убедиться, что все остальное функционирует соглсано ожиданиям.

-

Перехожу в папку u-boot-xlnx/include/configs... и не вижу zynq_zed.h

К сожалению, помочь разобраться не могу. Волею судеб Линукс и Зедборд лежат на полке. Их место занял Лэттис и PCIE.

-

Неплохие материалы для освоения Зинки в целом и Линукса в нем:

http://www.googoolia.com/wp/2014/10/29/les...m-host-of-zynq/

https://embeddedcentric.com/zynq-training-course/

https://embeddedcentric.com/embedded-operating-systems/

И еще немножко тут:

https://forums.xilinx.com/t5/Xcell-Daily-Bl...ded/ba-p/651297

-

Опубликовано · Изменено пользователем GriXa · Пожаловаться

Добрый день!

Мне кажется, с помощью простых if и else, парсер сделать крайне затруднительно. Нужно думать в сторону сложной комбинаторики, функций и for ... loop'ов

Подобный парсер видел для SPI интерфейса. Решение для VHDL было весьма изящно, на мой взгляд.

Для модуля создавался package, в котором с помощью констант и type были описаны параметры строковых данных.

К примеру,

package parser_pkg is --! maximum length of data packet constant MAX_DATA_LEN : integer := 54; -- Serial communication constants --! message is from command interface constant SER_COM_CMD_INTF_TYPE : std_logic_vector(7 downto 0) := X"55"; -- ... куча других констант --! command data structure type cmd_t is record --! message command cmd : std_logic_vector(15 downto 0); --! message type msg_type : bc_msg_type_t; --! interface intf_type : bc_intf_type_t; --! message length msg_len : integer range 0 to MAX_DATA_LEN; --! answer code answer : std_logic_vector(15 downto 0); --! answer length answer_len : integer range 0 to MAX_DATA_LEN; --! target host FPGA (Master / Slave) target_host: target_host_t; end record cmd_t; constant CMD_MIO_DUMMY : std_logic_vector(15 downto 0) := X"0000"; --! dummy command to reset interface type cmd_arr is array(integer range <>) of cmd_t; -- List of all supported commands with length (in bytes) and category constant BC_CMD_CMD_LIST : bc_cmd_arr := ( (CMD_MIO_DUMMY, MIO, CMD_INTF,0,EC_OK,0,BOTH), (CMD_MIO_GETNBTIMMEAS, MIO, CMD_INTF,0,EC_OK,2,SINGLE), (CMD_MIO_GETSTATUS, MIO, CMD_INTF,0,EC_OK,2,SINGLE), (CMD_MIO_GETLKDMODINF, MIO, CMD_INTF,4,EC_OK,12,SINGLE), (CMD_MIO_GETNBLKDMOD, MIO, CMD_INTF,0,EC_OK,2,SINGLE), (CMD_MIO_STOREUID, MIO, CMD_INTF,6,EC_OK,0,BOTH), (CMD_MIO_GETUID,MIO, CMD_INTF,0,EC_OK,6,SINGLE), (CMD_MIO_GETVERSION,MIO, CMD_INTF,0,EC_OK,8,SINGLE), (CMD_MIO_GETERRORCODE,MIO, CMD_INTF,0,EC_OK,4,SINGLE), (CMD_MIO_GETHWINF,MIO, CMD_INTF,0,EC_OK,52,BOTH), (CMD_MIO_DECLAREMASTER,SCO,CMD_INTF,16,EC_OK,12,BOTH), (CMD_MIO_STARTSAFECOM,SCO,CMD_INTF,0,EC_OK,0,BOTH), (CMD_MIO_TAKECFGDATA,SCO,CMD_INTF,24,EC_OK,0,BOTH), (CMD_MIO_STORECFGDATA,SCO,CMD_INTF,0,EC_OK,0,BOTH) );

-- далее следует огромный список функций для работы с командами, к примеру:

-- Function declaration --! @details Get command message properties --! --! InP: Command --! OutP: message properties function get_bc_cmd_cmd (cmd : std_logic_vector(15 downto 0)) return cmd_t; end package parser_pkg;

Подобные функции используются в State Machine для реализации парсера.

Получился большой блок комбинаторной логики. К счастью, он работал лишь на частотах меньше 50МГц.

-

Не нашел такой темы в этой ветке, потому создал новую.

Анонс новости на Digi-Key : https://www.digikey.com/en/news/press-relea...d-pads-makerpro

Тут есть документация : https://eewiki.net/display/MentorGraphicsDo...umentation+Home

Перевести проект PCI-e платы c Altera на Lattice

в Предлагаю работу

Опубликовано · Пожаловаться

Да, проект под ПЛИС Вам придётся переделывать заново - у Lattice семейства ECP нет встроенного PCIE-контроллера. Есть только блок сериалайзера-десериалайзера, а само ядро PCIE выполнено с помощью логического IP-блока.

Ещё рекомендую Вам узнать отдельно цену ядра, оно не бесплатное.

Так же в зависимости от сложности остальной части проекта следует проверить его реализуемость под конкретно выбранную ПЛИС - ядро PCIE, в зависимости от конфигурации, может занимать от ~6K до ~14K ячеек.