-

Постов

1 610 -

Зарегистрирован

-

Посещение

-

Победитель дней

2

Весь контент juvf

-

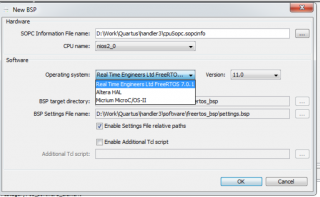

Да, прикрученна. Ставил Frertos без каких либо трудностей. Единственное, исходники ртос пришлось докачивать по мойму. Даже сейчас в NiosIDE при создании нового BSP предлагается FreeRTOS (можно сказать из коробки). Да и порт в демках FreeRTOS есть для ниоса. ДОлго в проекте работал..... Сейчас почему-то "BSP type 'freertos' unknown"?

-

Интеграция AD и TC

juvf ответил juvf тема в Altium Designer, DXP, Protel

Печально. Согласитесь, что сделано через место, в котором ни когда не светит солнце. С одной стороны глоболизация - это хорошо решили библиотеку переместить в централизованное сетевое хранилище, с другой стороны не научили АД НЕНАПРЯМУЮ обращаться к библиотеке при движении мышки. Букву s ввел в окне Libraries - ад удалил все имена из Component Name, которые не на s. Нажал t - остались только st*. Когда библиотека в сети, то эта фильтрация длиться очень очень долго. Это же не HD, и не SSD, это сетевой ресурс. До него доступ на порядок (если не на два, три) меньше. Например.... такая технология: яндекс.диск/дропДиск/гуглДиск (далее яд), Можно разместить библиотеку на яд в облако. До облачного яд может быть доступ 3Гб, а может быть 9600 бит/сек (а может быть вообще по расписанию - каждое утро с 8 до 9). На рабочих ПК ставим клиента яд и делаем локальные копии библиотек. АД работает с локальными копиями, быстро, шустро. При сохранении библиотеки АД быстро сохранит локально, а клиент ЯД в фоне синхронизирует с облаком. Я думал, что может Vault работает по подобной технологии? Может родное хранилище библиотек работает как-то через локальные копии.... ps а как ад с ваултом работает при отсутствии сетевого ресурса? если комп в офлайне, то вообще библиотеки не доступны? С яд можно в офлайне работать. Правда могут быть коллизии на сохранение.... но это можно административно решить. -

2018 Вопросы начинающих

juvf ответил Sanchosd тема в Altium Designer, DXP, Protel

В слоях над/под опасной дорожкой добавить Polygon Pour Cutout -

Интеграция AD и TC

juvf опубликовал тема в Altium Designer, DXP, Protel

Вопрос скорее к сотрудникам Родник-а, у вас есть опыт интеграции AD в TeamCenter? Мы перешли на ТС и интегрировали в него АД. Разработчики по всей стране, база TC удаленно в одном городе. Есть куча библиотек R.PcbLib, R.SchLib, C.PcbLib, C.SchLib, L.PcbLib, L.SchLib, и т.д. на удаленном сервере. Каким то образом эти библиотеки собраны в ТС в одну TC_ADLib.DBLIB. В рабочем AD на локальной машине инициализирована только одна удаленная библиотека TC_ADLib.DBLIB Сначала вообще было не возможно работать в АД. В схемном редакторе взять элемент из библиотеки и поместить на схему было запрещено, т.е. берёшь drap-ом элемент, тащишь на схему, курсор мышки изменяется на знак ЗАПРЕТ. Нет возможности драп&дроп добавить эл-мент на схему. Обратился к сисадминам. Сисадмин сделал тоже самое... но не отпускал мышку на схеме.... через минуты 3 знак запрета изменился на элемент, отпустил мышку и вуаля - элемент добавлен. Они нашли, что во время драп, альтиум начитает слать бешеную кучу запросов на ipv6. Но у нас нет ipv6. Админ отключил у меня на пк ipv6, ад перестал обращаться на ipv6 и добавление эл-та стало возможным. Ад работает.... но некоторые операции длятся минутами.... десятками минут. Ад часто подвисает. Всё что связанно с библиотекой - всё тормозит. Любая операция обращения к библиотеке - тормозит. Если открыть R.PcbLib с удаленного сервера, то сохранение будет 2,5 минуты. Если скопировать R.PcbLib на локальный диск открыть/поправить/сохранить - то сохранение доли секунд. Я понимаю, что тут нужно разбираться с каналом связи между ПК и сервером ТС/библиотекAD.... Нужно скорость как то поднимать.... Но всё таки вопрос к АД: Не раз встречал замечания к АД, что если библиотеки на удаленном сервере, то комфортной работы не будет.... АД постоянно обращается к библиотеке на диске, и постоянно тормозит. может мы не правильно что-то организовали? Может АД при запуске долго вычитать библиотеку, а потом быстро работать? Может библиотеки как-то должны быть на ПК в локальных копиях? Может локальные копии должны синхронизироваться через SVN, или через Vault? Altium Vault - это вроде как тот же ТС, тот же централизованный сервер с шаблонами и библиотеками. Как с Vault АД работает? Также, при каждом драп&дроп AD отправляет сотню запрос на удаленный сервер и пока не получит ответ, пользователь ждёт? -

2018 Вопросы начинающих

juvf ответил Sanchosd тема в Altium Designer, DXP, Protel

Это делается через варианты. Гулите мануалы по вариантам в АД. Странное желание. По госту в сборке пишется позиционное обозначение. Через спецификацию находится нужный элемент. Монтажники могли к этому привыкнуть.... но это очень не удобно. На разных предприятиях работал... давно уже у монтажников стоит ПК с AD/P-Cad. Поставьте монтажнику стрый ПК и АД Вьювер. Там можно вывести PCB List, можно в 3д плату показать.... подсветить выбранный элемент из списка -

Nios2 FreeRTOS

juvf опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Когда-то, был сделан проект в Q11 для Cyclon III c NIOS2, с FreeRTOS. Freertos был прикручен из коробки Nios IDE. Девайс сделан, отлажен и запущен в серию. Прошло время... за это время эникэйщики успели сломать сервер лицензий. Понадобилось в этом проекте поковыряться. Сервер лицензий через "боль" восстановили. Вроде в Q11 проект собрался.... но вот в IDE NIOS не собирается. Требует пересобрать BSP. Открываю редактор BSP и получаю сообщение Вопрос: в чём дело? Проект не менялся, по на пк не менялось. Всё тот же Q11. Почему IDE не знает freertos? Может это связанно с тем, что в лицензии не хватает какого-нибудь модуля? -

2018 Вопросы начинающих

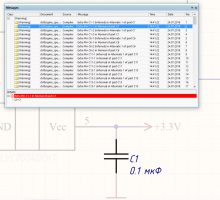

juvf ответил Sanchosd тема в Altium Designer, DXP, Protel

в свойствах пина в Mode Alternative1 было Designator: "1", Display Name: "1", в свойствах пина в Mode Normal было Designator: "1", Display Name: "" (Display Name был пустой) ps Вопрос остался риторический: Как из этого "Warning: Extra Pin C1-1 in Normal of part C1" понять, что причина ворнинга в том, что поля в свойстве пина разные? И вообще, как это перевести? Я их не отключаю и ни кому не советую. -

2018 Вопросы начинающих

juvf ответил Sanchosd тема в Altium Designer, DXP, Protel

Спасибо, помогло!!! Ни одного ворнинга и ни одной ошибки. Компилиться в "ноль"!!! -

В чем ртос поставяется? в исходниках? тогда для дебага не нужны ни какие плуги. в кубе чистая фриртос, без FRTOS1. И куб добавляет в проект фриртос в виде исходников (как и остальные компаненты).

-

какая-то кастомная FreeRTOS. Добавлена какая-то configUSE_HEAP_SCHEME , нет xPortGetFreeHeapSize().... лучше та, которая вам нужна. Я обычно использую heap_1.c, мне не нужно динамически задачи создавать и удалять. не будет фрагментации. почитайте про схемы, выберете себе подходящую. Вот тут про память, кучи, стеки разжованно. Если после запуска планировщика не создаете/удаляете задачи/симафоры/очереди, то heap_1.

-

какой хип? heap_1.c, heap_2.c...or heap_4.c?

-

а что дает xPortGetFreeHeapSize() до xTaskCreate()?

-

так мануалов полно в инете.... configMINIMAL_STACK_SIZE - это размер стека ТОЛЬКО для IDLE таска. общий размер, который ртос отьест для всех задач, семафоров, очередей и т.п, задается параметром configTOTAL_HEAP_SIZE

-

2018 Вопросы начинающих

juvf ответил Sanchosd тема в Altium Designer, DXP, Protel

А что там смотреть? Футпринт один для обоих вариантов, в котором две контактные площадки с номерами 1 и 2. В УГО в нормальном варианте кондер вертикально, в альтернативном - горизонтально. Имена/номера пинов одинаковы, 1 и 2. Почему ворнинг....? И вообще... прежде чем решать проблему, хочу понять проблему... что не нравиться компилятору.... я не носитель английского.... но этот месадж шаблон сносит.... "Warning: Extra Pin C1-1 in Normal of part C1" - что это такое? Где глагол? "Внимание: В режиме Normal С1 дополнительный пин С1-1"! А что дополнительный пин? Введён доп. пин? Присутствует доп.пин? Удален? Где как минимум глагол to be? И что такое вообще "дополнительный пин"? У меня в УГО два режима: "Normal" и "Alternate 1". Ни каких дополнительных пинов в обоих режимах нет. Не понятно, что за ворнинг и какой смысл до разработчика ПП хочет донести АД этим ворнингом? -

2018 Вопросы начинающих

juvf ответил Sanchosd тема в Altium Designer, DXP, Protel

-

2018 Вопросы начинающих

juvf ответил Sanchosd тема в Altium Designer, DXP, Protel

7-ая секция/без секций/в одной секции добавить ноги питания. "Наглядность та же." - если просто смотреть схему на бумаге, то да.... таблицей даже наглядней и удобней. Вот только в CAD, коей является АД, это опасно. У вас в таблице будет написано одно, а в скрытых ногах подключение другое. И то, что надпись в таблице не соответствует реальному подключению не видно. и АД это не покажет. Тем не менее.... это дело вкуса.... делайте таблицы в ручную проверяйте скрытые ноги... НО при любой подходе ворнингов не должно быть. ps если используете не все секции, то остальные входы должны быть подтянуты к земле/питанию (для некоторых кмос, не помню каких). По ескд очень удобно в таблице показать, что пины такие на землю. В ад нужно вытащить все неиспользуемые секции и посадить входы явно. Нужно неиспользуемые секции вытаскивать на схему. Это тоже коряво. Как вы в таких случаях поступаете? -

2018 Вопросы начинающих

juvf ответил Sanchosd тема в Altium Designer, DXP, Protel

Не хотел отвечать, ибо не устраивать спор. Но поддержу Владимира Я не различаю ворнинг и ошибку, а тем более error и Fatal error. Вообще, что такое Fatal error? Чем он отличается от error? Проект должен копиляться или проверять в ноль. Ни каких ворнингов и ерроров. Либо настраивайте правила, чтоб не было ворнинга (например на D3 нога 4 должна быть так и так), либо устраняйте условия ворнинга. Тем более у Panych ворнингов было ПАРУЭКРАНОВ!!! ps Это весьма распространённое явление выстрела себе в ногу в АД. Забудьте про скрытые выводы. Их не должно быть. Схема может быть транслирована в пдф. Там скрытые выводы не видны. Да и в АД этот "финт" ухудшает читаемость. смотришь в схему и не видно пинов/цепей. Может получитсья так, что ногу нужно зацепить на AGND, а она зацепилась скрытым пином на GND, а может вообще быть NoNet. Попробуйте сделайте на микросхме все пины срытые.... на резисторах скрытые.... на кондёрах.... Как ваша схема будет выглядеть? Ни чего не должно быть неявного. Всё должно быть очевидно и прозрачно!!! pps Если вы любите делать цепи-невидимки скрытые пины, то либо настраивайте правила, чтоб не было ворнингов (я уже не говорю за ерроры и тем более ФАТАЛ (кто это придумал?) ероры), либо явно подцепляйте выводы, чтоб не было ворнинга... там более ПАРУ ЭКРАНОВ. Имхо. -

2018 Вопросы начинающих

juvf ответил Sanchosd тема в Altium Designer, DXP, Protel

Не должно быть ни одного предупреждения. Проект должен проверяться/компиляться в ноль, т.е. ни одной ошибки, ни одного предупреждения. За каждым ворнингом прячутся баги. -

2018 Вопросы начинающих

juvf ответил Sanchosd тема в Altium Designer, DXP, Protel

-

2018 Вопросы начинающих

juvf ответил Sanchosd тема в Altium Designer, DXP, Protel

Если хотите идти пропой idf, то бубен - это CircuitWorks, мануал можно глянуть тут -

2018 Вопросы начинающих

juvf ответил Sanchosd тема в Altium Designer, DXP, Protel

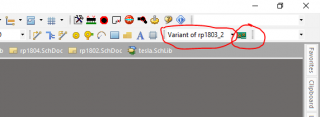

Этого мало, т.е. если вы нарисовали в SW сами деталь и откроете свои idf - ни какие модели SW не подтянет. Прежде нужно бубном стучать. У меня часть элементов нарисована в SW и сохранена как степ. Ни один компонент не порисовался. Нужно бубном что-то сопоставлять. Более того - я степку ПП сохранил на флешку дома, на работе открыл - где тут мои солиды и степ модели отдельных компонентов? Нету! Нужно таскать на флешке все исходники.... на работе делать сопоставления.... нееее... это не наш метод. Тем более часть компонентов с 3dcontentcentral, часть компонентов с официальных библиотек от Altium-а ( а там вообще нет отдельно 3д на деталь, только *.libPcb), часть деталей с библиотек от производителей микросхем, часть деталей вообще с библиотеки колеги... бывшего. Альтиумом тупо на любом пк сохранил ПП в степ, на любом пк открыл ПП в компасе. Ни какие исходные степ/sw не нужны. я сам не делал. В схематике есть меню Project->Variants... в PCB есть см рисунок. В схематике тоже вверху выбор варианта. При выборе варианта в схеме не нужные УГО будут зачеркнуты красным. Не надо писать что-то как увас "Это не ставить в таком варианте". При генерации бом, выбераеете вариант и не нужных деталей не будет. вот вам зацепка -

2018 Вопросы начинающих

juvf ответил Sanchosd тема в Altium Designer, DXP, Protel

Решил проблему с 3D. Задача простая: примерить получившуюся плату в корпус до изготовления. Кому-то нужно сквозное проектирование - ищите пути... SW, circuitworks, ADский вольт или ещё что-то.... Всё это громоздкое и .... Пробовал ещё через IDF, тупо сохранить в АД в idf и открыть в SW - так не получается. SW вместо моделей рисует кубики. Все детали будут как кубики с максимальными габаритами РЭК. Кому интересно примерить плату в корпусе в пару кликов - Я использовал Компас3Д. В AD тупо сохраняешь STEP, в Компасе открывает. Компас открывает степки от АД на ура, без ворнингов, ни чего не съезжает, не пропадает. Сохраняется вся геометрия, все надписи, Плата открывается как сборка из деталей РЭК. То что нужно!!! Это делается через варианты. -

2018 Вопросы начинающих

juvf ответил Sanchosd тема в Altium Designer, DXP, Protel

Слона видел. Но это действительно слон, почти что новая планета. А вы сами пробовали это приготовить? Я видел эти руководства. Там тонна плагинов всяких нужна... и в AD и в SW. Там реализована фишка двунаправленной передачи. Можно сборку закинуть в SW, подвигать элементы и вернуть в AD. Мне нужно только из AD в SW. Да ещё эти плагины денег стоят. Да ещё и волт вроде задействован. Про волт отделная тема... всё через бубен с заячей лапкой. Отказались. Ооооо... дельный совет! Я искал в экспорте в АД галку, чтобы всю сборку одной деталью делало. Как это сделать? -

2018 Вопросы начинающих

juvf ответил Sanchosd тема в Altium Designer, DXP, Protel

Я это руководство видел, по нему научился SOIC, SMD и прочие примитивы делать в SW для AD. Хорошее руководство. В добавок научился сборку делать и привязку. Но не более. Тем более всякие дефолтные шаблоны шаманить. Можно и самому рисовать.... соики и смд, но например microUSB уже будет посложнее нарисовать. А попробуйте нарисовать модуль xBee? В 3dcontentcentral уже много чего, в том числе и всякие микросборки типа RFM96 или xBee, не нужно тратить время. Но это не главный плюс 3dcontentcentral (или любых сторонних 3D), Когда в одного рисуешь, то можешь ошибиться. Какой-нибудь размер не правильно понял - сделашь не правило футпринт и неправильно 3Д-модель. А если не там нарисовал контакт под ассиметричную ножку в футпринте, скачал левый 3D, вставил себе в футпринт - ОПА!!!! ножки не попали в контактные площадки. Что-то пошло не так! При таком подходе вероятность ошибиться в футпринте снижается. Зачем из АД в Солид? - я 3д платы засовываю в корпус и вижу, что например крепёжные отверстия на плате не попали. Или разъем выходит не туда, куда нужно, или габарит батарейки/реле/разъема вышел не туда. Раньше наоборот, корпус вставлял в АД, и там всё проверял. Но появился корпус с крышкой - в ад не видно, что под крышкой. А SW дает разрезы, можно внутрь заглянуть. Можно полупрозрачной крышку сделать... проще привязку делать. -

2018 Вопросы начинающих

juvf ответил Sanchosd тема в Altium Designer, DXP, Protel

а как? SW для меня другая планета. Я понимаю, что тут обсуждают AD, но всё же может кто-то уже портировал модели из AD в SW2018 И знает где и что в SW крутить? В SW8 и в SW10 таких проблем не было. Что интересно, STEP модели скачанные с 3dcontentcentral открываются и в AD и в SW18 нормально. А STEP модели, созданные в AD, открываются в SW18 c проблемами.