Gas Wilson

Свой-

Постов

141 -

Зарегистрирован

-

Посещение

-

Победитель дней

9

Весь контент Gas Wilson

-

Информация по изменениям в PDS 2022_2 SP1.2 PDS_2022.2_SP1.2_ads_Release_Notes_innek.pdf

-

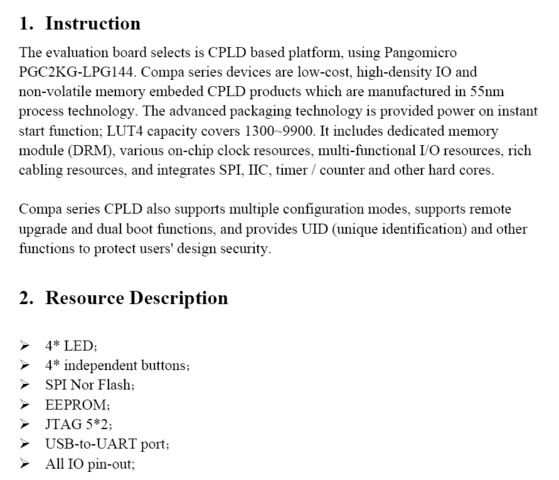

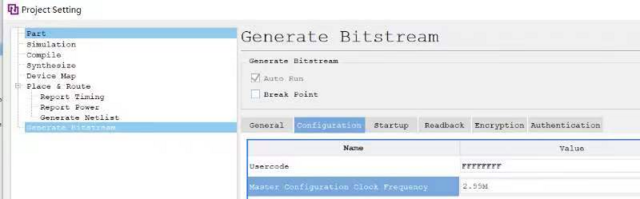

UG30004 - Compa Series CPLD configuration user guide https://disk.yandex.ru/i/nfSRF2HLCqWVpA

-

Добрый день. Первый документ будет чуть позже. UG041004_Logos2_HSSTLP_IP_innek.pdf

-

Titan2 Series FPGA Configuration User Guide UG050005_Titan2 series FPGA configuration (configuration) user guide V1.0 innek.pdf

-

Приветствую. Документация на Timing Analyzer Timing_Analyzer_User_Guide_innek .pdf

-

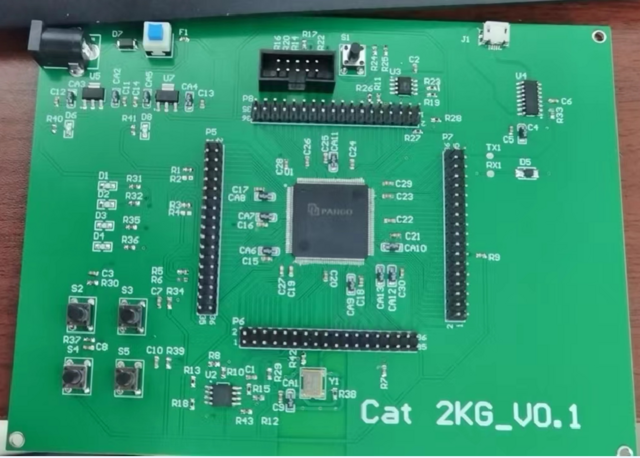

Приветствую! Все шаги как как по туториалу (пункт 4.4 и далее)? 01.LED experiment and simulation AXP100.pdf

-

Рад помочь 🙂 Принимаю плюсы в репутацию 🙂

-

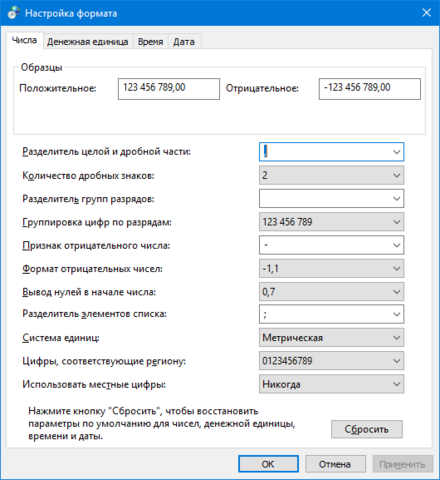

Привет! Это ошибка из за русской локали. TCL требует точку в качастве разделителя дробной части, а в русской стоит запятая

-

Userguide на PCIe IP core для Logos 2 UG042004_Logos2_PCIe_IP_UserGuide_innek.pdf

-

Питание ПЛИС

Gas Wilson ответил Styv тема в Работаем с ПЛИС, области применения, выбор

Интересные варианты мощных понижающих преобразователей со встроенной индуктивностью. Используются на отладках Alinx EZ8303_innek.pdf EZ8620_innek.pdf EZ8626_innek.pdf -

UG040012_Logos2 Board Hardware Design Guide V1.3_innek.pdf

-

Да, IP ядер у них мало, но обещают что работа ведётся. Вот список стандартных ядер из последней PDS ADC 1.1 ip_iars/adc/ipmxe_adc_v1_1.iar Logos2 HMIC_S 1.7 ip_iars/ddr/ips2l_hmic_s_v1_7.iar Titan2 HMIC_S 1.6 ip_iars/ddr/ips2t_hmic_s_v1_6.iar Titan2 HMIC_S 1.7 ip_iars/ddr/ips2t_hmic_s_v1_7.iar Logos HMIC_H 1.2 ip_iars/ddr/ipsl_hmic_h_v1_2.iar Logos HMIC_S 1.3 ip_iars/ddr/ipsxb_hmic_s_v1_3.iar Logos HMIC_S 1.3a ip_iars/ddr/ipsxb_hmic_s_v1_3a.iar DDR3 Interface 1.3 ip_iars/ddr/pgs_mc3q_v1_3_patch5.iar Logos2 HSSTLP 1.7 ip_iars/hsst/ipm2l_hsstlp_v1_7.iar Logos2 HSSTLP 1.8 ip_iars/hsst/ipm2l_hsstlp_v1_8.iar Titan2 HSSTHP 1.7 ip_iars/hsst/ipm2t_hssthp_v1_7.iar Titan2 HSSTHP 1.8 ip_iars/hsst/ipm2t_hssthp_v1_8.iar Titan HSST 1.1a ip_iars/hsst/ipm_hsst_v1_1a.iar Logos HSST 1.3e ip_iars/hsst/ipml_hsst_v1_3e.iar Logos HSST 1.4 ip_iars/hsst/ipml_hsst_v1_4.iar Titan2 iScan 1.7 ip_iars/iscan/ips2t_iscan_v1_7.iar Titan2 iScan 1.8 ip_iars/iscan/ips2t_iscan_v1_8.iar LVDS 1.0 ip_iars/lvds/ipsxe_lvds_v1_0.iar Logos2 PCI Express 1.4 ip_iars/pcie/ips2l_pcie_gen2_v1_4.iar Titan2 PCI Express 1.1c ip_iars/pcie/ips2t_pcie_v1_1c.iar Titan2 PCI Express 1.2 ip_iars/pcie/ips2t_pcie_v1_2.iar Logos PCI Express 1.2a ip_iars/pcie/ipsl_pcie_v1_2a.iar Logos2 QSGMII v1.2 ip_iars/qsgmii/ipsxd_qsgmii_v1_2.iar Titan2 QSGMII v1.0 ip_iars/qsgmii/ipsxe_qsgmii_v1_0.iar Logos2 HD/3G-SDI 1.2a ip_iars/sdi/ips_sdi_v1_2a.iar Logos2 HD/3G-SDI 1.3 ip_iars/sdi/ips_sdi_v1_3.iar TITAN2 12G-SDI 1.1 ip_iars/sdi/ipsxe_sdi_v1_1.iar Logos2 SEU 1.6 ip_iars/seu/ips2l_seu_v1_6.iar Logos SEU 1.2b ip_iars/seu/ipsl_seu_v1_2b.iar Logos2 SGMII 1GbE v1.2 ip_iars/sgmii/ips2l_sgmii_v1_2.iar Titan2 SGMII 1GbE v1.1c ip_iars/sgmii/ips2t_sgmii_v1_1c.iar SGMII 1GbE v1.9a ip_iars/sgmii/ips_sgmii_v1_9_patch2.iar Logos SGMII 1GbE v1.1c ip_iars/sgmii/ipsl_sgmii_v1_1c.iar 10/100/1000M Ethernet MAC 1.1 ip_iars/ts-mac/pgs_tsmac_v1_1_patch5.iar Logos2 XAUI v1.2a ip_iars/xaui/ips2l_xaui_v1_2a.iar Titan2 XAUI v1.1b ip_iars/xaui/ips2t_xaui_v1_1b.iar XAUI v1.5b ip_iars/xaui/ips_xaui_v1_5_patch2.iar Logos XAUI v1.1b ip_iars/xaui/ipsl_xaui_v1_1b.iar

-

-

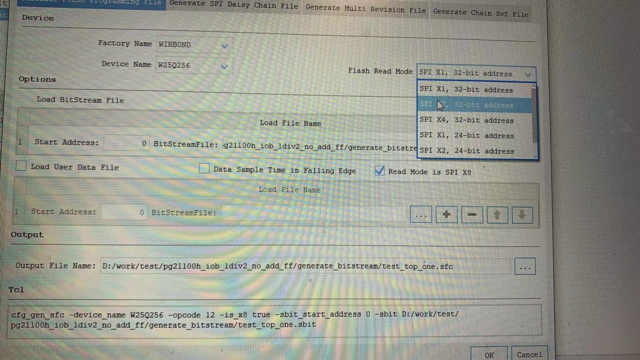

Ну как обычно - пока фича не работает 🙂 Но можно в программаторе прошить. So far,the development environment PDS does not support X8 mode writing, we can use another way. The software can generate two SFC files. The first file is written to chip U 5 by default through the software. Then the chip U 6 is welded to the U 5 position for writing the second file. after completion, the two chip can be welded to the original location.

-

Новая ревизия ADS Syntesis User guide - 2.3 https://disk.yandex.ru/i/s_MRfBQ1U_VlDA

-

Route_Constraint_Editor_User_Guide 2.0 _innek.pdf

-

Вот исходники примера https://disk.yandex.ru/d/vF5OO0ovsQ2zkw

-

UG030005 Compact Series CPLD Input Output Interface (IO) User Guide_innek.pdf

-

UG030003 Compact Series CPLD Clock Resources Clock PLL User Guide_innek.pdf

-

Описание нового релиза PDS - PDS_2022.2-rc3 Release_Notes_PDS_2022.2-rc3_innek.pdf

-

-

Нет, планов таких у них нет. Вопрос с Synplify не решился? 🙂

-

Я понимаю 🙂 К сожалению пока платы под рукой нету - сам проверить не могу. Просто пересылаю ответы техподдержки.

-

-

Ответ техподдержки you may add sbit than choose read mode is spix8 choose x4 in flash read mode as well